# **DIAMOND TRANSISTOR OPA660**

By Klaus Lehmann, Burr-Brown International GmbH

## CIRCUIT TECHNOLOGY WITH THE DIAMOND TRANSISTOR OPA660

The monolithic integrated circuit OPA660 uses the Diamond structure to act as an ideal transistor. However, this circuit has the advantage that it avoids the biasing circuits and eliminates the need for an offset voltage compensation network. With this element, peripheral components are reduced to the essential minimum. Using the DC-coupled wideband voltage amplifier and buffer, conventional and new circuit designs of the OPA660 can be compared with each other.

A report in <u>Electronik Industrie 90</u> (vol. 1, p.70) presented basic explanations, along with a schematic overview of circuits possible with the voltage-controlled current source OPA660. This article is intended to describe the practical circuit design. From the many possible application circuits, this article first examines the basic circuits without external feedback.

## **DIAMOND TRANSISTOR**

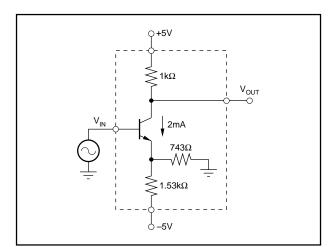

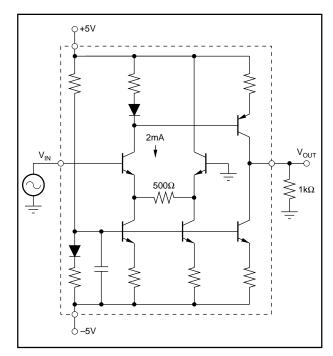

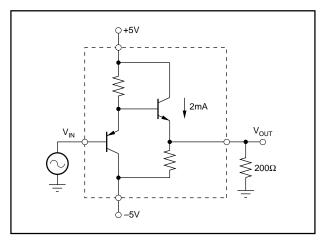

Figure 1 illustrates what is probably the simplest DCcoupled voltage amplifier. Several factors in the circuit design are disadvantageous for easy and general application: the input offset voltage which is dependent upon temperature ( $V_{10} = -627 \text{mV}$ —see Table I), the output offset voltage— also dependent upon the temperature ( $V_{00} = + 3\text{V}$ ), and the bias current ( $I_0 = 2\text{mA}$ ), which flows through the output load resistor (1k $\Omega$ ). When the offset-free signal voltage  $V_{1N}$  appears at the output, it is amplified as desired

FIGURE 1. DC-Coupled Voltage Amplifier.

(G = 2) but is superimposed with bias voltage and current. These DC currents and bias voltages, which are determined by the transistor, are systematically compensated in the following circuit variations. V<sub>10</sub> and I<sub>0</sub> require that the emitter resistor be divided (743 $\Omega$  and 1.53k $\Omega$ ). The signal voltage gain results from:

$$G = \frac{V_{OUT}}{V_{IN}} \approx \frac{Ik\Omega}{743\|1.53k\Omega} = 2$$

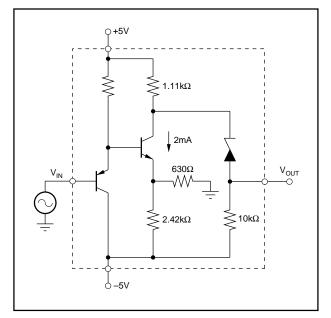

FIGURE 2. Adjustment of V<sub>10</sub>.

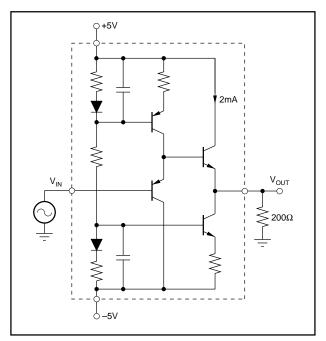

Further important parameters are summarized in Table I. In Figure 2,  $V_{10}$  is compensated with a previously inserted complementary emitter follower (pnp), while  $V_{00}$  is compensated with a zener diode inserted afterward.  $I_0$  still requires division of the emitter resistor (630 $\Omega$  and 2.42k $\Omega$ ). The signal gain now results from:

$$G = \frac{V_{_{OUT}}}{V_{_{IN}}} \approx (1.11 \text{k}\Omega \parallel 10 \text{k}\Omega) / (630\Omega \parallel 2.42 \text{k}\Omega) = 2$$

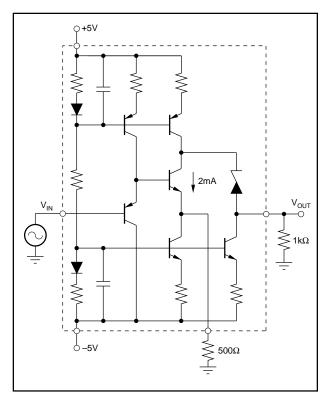

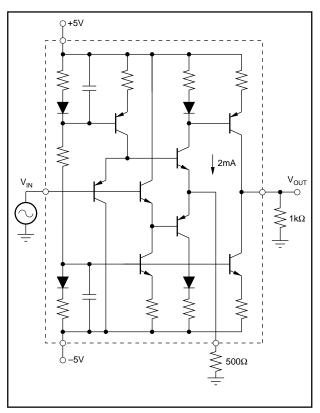

With current sources as shown in Figure 3, the gain determined by the resistors (500 $\Omega$  and 1k $\Omega$ ) can be achieved as desired, without bias currents and voltages.

$$G = \frac{V_{OUT}}{V_{IN}} \approx \frac{1k\Omega}{500\Omega} = 2$$

FIGURE 3. Circuit with Constant Current Sources.

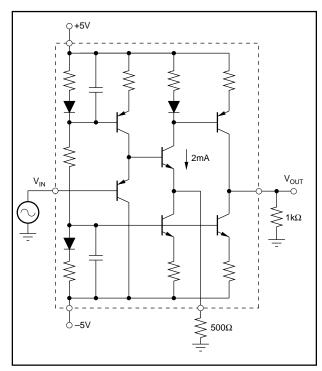

FIGURE 4. Insertion of PNP Current Mirror.

Figure 4 shows a variation comparable to Figure 3, in which the  $V_{00}$  is avoided using a current mirror instead of a zener diode. Figure 5 shows how a differential amplifier can be used to compensate the  $V_{10}$  in place of the previously inserted complementary emitter follower. This method has

FIGURE 5. Differential Amplifier for Compensation of  $V_{10}$ .

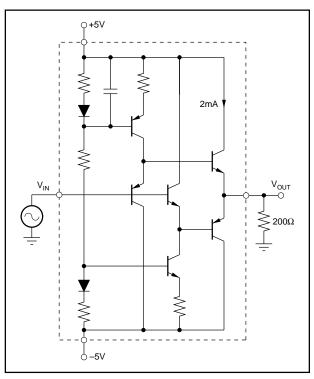

FIGURE 6. Diamond Structure.

the disadvantage that the emitter resistor  $(500\Omega)$  is connected on both sides to "hot" adaptors. The previously discussed methods using zener diodes or resistors instead of current sources are also possible here. Figure 6 illustrates the most developed and elegant method with a complementary

symmetric circuit, called "Diamond structure" in laboratory jargon. Ideally, the three signal terminals are free from bias currents and offset voltages. In this case:

$$G = \frac{V_{OUT}}{V_{IN}} \approx \frac{1k\Omega}{500\Omega} = 2$$

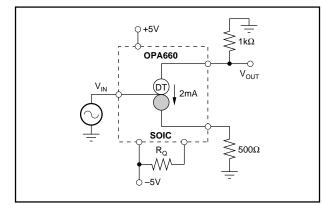

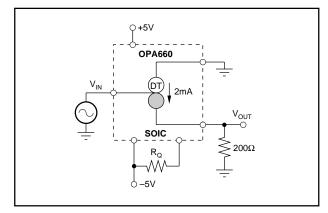

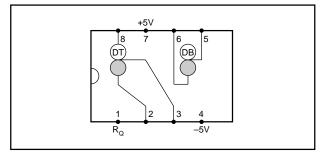

The active operating area of the previously discussed circuit designs that are not complementary-symmetric is limited by the polarity of the input signal. For instance, when the signal current as shown in Figure 4 exceeds the quiescent current ( $I_o = 2mA$ ) through the emitter resistor ( $500\Omega$ ) using a negative input signal, it will load up to a signal limitation. This limitation does not correspond to Figure 6. This circuit looks like a quasi-ideal transistor and is characterized as the Diamond Transistor (DT) in the following. Burr-Brown offers this monolithic integrated circuit under the name OPA660. Figure 7 shows how the DT is used in the DC-coupled voltage amplifier examined here. With the resistor  $R_Q$ , the quiescent current  $I_Q$ , for example  $I_Q = 2mA$ , is adjusted, as is the transconductance gm. Thus the following equation holds:

$$G = \frac{V_{OUT}}{V_{IN}} = \frac{1k\Omega}{500\Omega + \frac{1}{gm}} \approx \frac{1k\Omega}{500\Omega} = 2$$

FIGURE 7. Diamond Transistor in a DC-Coupled Voltage Amplifier.

#### **DIAMOND BUFFER**

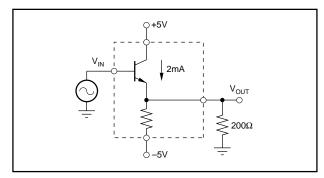

The simplest form of a DC-coupled buffer is the emitter follower as illustrated in Figure 8. The disadvantage of this buffer is that the voltage offset is dependent upon the temperature ( $V_{10} = -627 \text{mV}$ , see Table II) between the input and output signals, while the ability to handle negative signals depends upon the quiescent current ( $I_0 = 2\text{mA}$ ) and load resistor (200 $\Omega$ ). In Figure 9, an additional emitter follower is inserted to compensate the  $V_{10}$ . The next step is shown in Figure 10, in which the pull-up and pull-down resistors are replaced by constant current sources.

As shown in Figure 11, the advantages that can be achieved with a complementary symmetric solution are comparable to those using a Diamond transistor. A comparison of Figures

FIGURE 8. DC-Coupled Buffer.

FIGURE 9. Adjustment of V<sub>IO</sub> with Previously Inserted Complementary Emitter Follower.

FIGURE 10. The Pull-Up and Pull-Down Resistors are Replaced Here by Constant Current Sources.

11 and 6 demonstrates that Figure 11 is a part of the circuit illustrated in Figure 6. This section, which is also a so-called push-pull buffer design, is used in Figure 12 as a part of the Diamond transistor. The following equation applies:

$$G = \frac{V_{OUT}}{V_{IN}} = \frac{200\Omega}{200\Omega + \frac{1}{gm}} \approx 1$$

The integrated circuit OPA660 contains a complete DT as well as a part of the DT, shown in Figure 11, which is called the Diamond Buffer (DB) and is available in an 8-pin DIL or SOIC package (see Figure 13).

## **BASIC CIRCUITRY**

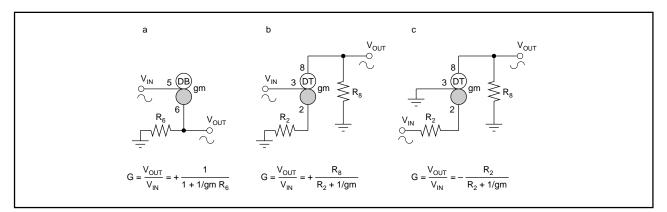

To give the reader an overview, the previous explanations of the DB and DT are summarized schematically in Figure 14. The common base circuit is also detailed in this presentation to complete the explanations. The signal transmission of the

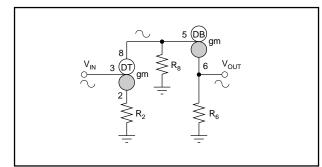

FIGURE 11. Push-Pull Buffer.

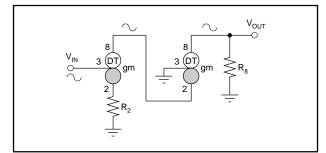

DT is the reverse of that of a normal transistor. The common emitter circuit with the DT does not invert the phase of the input signal, while the common base inverts. In many applications, the high-impedance output with its small output current capability seems to be a disadvantage, as shown in Figures 14b and 14c. In conventional circuits, the emitter follower is inserted afterwards. Figure 15 shows the connection between DT and DB, in which all advantages mentioned here are maintained. The signal-inverting variation as illustrated in Figure 14c has a low-impedance signal input (2). This disadvantage, however, can be avoided by connecting the emitter follower to the low-impedance input as shown in Figure 16. DB and DT form a differential amplifier with current output. This is the well-known function of an operational transconductance amplifier (OTA). The cascaded circuitry made up of two DTs shows similar external effects, as shown in Figure 17.

FIGURE 12. Push-Pull Buffer as a Part of the Diamond Transistor.

FIGURE 13. The OPA660 is Housed in an 8-Pole DIP or SOIC Package.

FIGURE 14. DC-Coupling of the Basic Circuits with DB and DT.

$V_{\text{IN}} \xrightarrow{5} (DB) \text{gm} \text{$

FIGURE 15. DT and DB Inserted Afterwards.

FIGURE 17. Cascaded Diamond Transistors.

FIGURE 16. Operational Transconductance Amplifier (OTA).

## SUMMARY

The applications presented here are intended to provide an overview of the versatile applications using DB and DT according to their prototype, the normal transistor. In contrast to the conventional transistor, the DB and DT require practically no circuit interface. The external components are reduced to the necessary functional elements. Looking at the results of Tables I and II, particularly from the DB and DT, one notices that some parameter are not exactly "ideal." Through their hard work, however, design engineers are coming closer and closer to this ideal. In this process, the OPA660 is the first step. Including feedback circuits in the combination of DB and DT results in, among other things, current-feedback and voltage-feedback amplifiers. Schematic examples of these designs are outlined in (1).

| PARAMETER               | CONDITION                | FIGURE                  |                         |                         |                         |                         |                         |                         |      |  |

|-------------------------|--------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|------|--|

|                         |                          | 1                       | 2                       | 3                       | 4                       | 5                       | 6                       | 7                       | UNIT |  |

| Input Offset Voltage    | –25°C<br>+27°C<br>+125°C | 722<br>627<br>445       | -19.1<br>-22.5<br>-28.4 | 15.0<br>18.2<br>24.2    | 14.1<br>17.1<br>22.9    | 0<br>0<br>0             | -1.8<br>-1.7<br>-1.3    | -13.9<br>-16.3<br>-20.1 | mV   |  |

| Input Bias Current      | -25°C<br>+27°C<br>+125°C | -14.4<br>-15.4<br>-17.4 | 10.2<br>10.1<br>9.8     | -11.9<br>-11.8<br>-11.6 | -12.2<br>-12.0<br>-11.8 | -15.6<br>-15.3<br>-14.8 | -8.8<br>-8.5<br>-8.0    | -2.2<br>-1.6<br>-0.9    | μΑ   |  |

| Output Offset Voltage   | -25°C<br>+27°C<br>+125°C | 3188<br>3000<br>2636    | -7.0<br>-0.7<br>10.2    | 47.0<br>35.5<br>14.5    | -33.1<br>-34.6<br>-38.2 | -4.7<br>-0.4<br>+7.1    | 2.5<br>3.4<br>4.3       | 40.1<br>30.0<br>16.3    | mV   |  |

| Output Bias Current     | -25°C<br>+27°C<br>+125°C | 1812<br>2000<br>2636    | 2009<br>2003<br>1993    | 18.2<br>0.6<br>–31.8    | -6.6<br>-2.5<br>4.6     | -4.7<br>-0.4<br>+7.1    | -0.9<br>0.2<br>1.8      | 15.6<br>0<br>–22.3      | μΑ   |  |

| Transconductance        | -25°C<br>+27°C<br>+125°C | 79.1<br>72.6<br>65.0    | 85.0<br>70.9<br>53.9    | 83.5<br>71.4<br>56.9    | 81.6<br>69.9<br>55.8    | 42.0<br>35.6<br>27.8    | 161.3<br>138.9<br>111.8 | 100.1<br>112.1<br>120.9 | mA/V |  |

| DC Gain                 | +27°C                    | 1.93                    | 1.92                    | 1.92                    | 1.88                    | 1.83                    | 1.90                    | 1.84                    | V/V  |  |

| Input Resistance        | 10kHz                    | 0.065                   | 0.38                    | 3.0                     | 3.0                     | 0.068                   | 1.6                     | 1.4                     | MΩ   |  |

| Input Capacitance       | 10MHz                    | 7.5                     | 2.2                     | 2.1                     | 1.9                     | 3.7                     | 3.8                     | 0.8                     | pF   |  |

| Output Resistance       | 10kHz                    | (1)                     | (1)                     | 48                      | 150                     | 153                     | 110                     | 27                      | kΩ   |  |

| Output Capacitance      | 10MHz                    | 3.0                     | 3.6                     | 2.5                     | 8.4                     | 8.4                     | 11.8                    | 2.8                     | pF   |  |

| Small Frequency Resp.   | 0.1Vp-p<br>–3dB          | 90                      | 65                      | 22                      | 22                      | 22                      | 19                      | 74                      | MHz  |  |

| Large Frequency Resp.   | 2Vp-p                    | 90                      | 65                      | 22                      | 22                      | 22                      | 19                      | 74                      | MHz  |  |

| Slew Rate               | 2Vp-p                    | 220                     | 140                     | 60                      | 70                      | 70                      | 50                      | 300                     | V/µs |  |

| Differential Gain       | 2Vp-p<br>5MHz            | 2.9                     | 2.4                     | 3.2                     | 1.4                     | 2.2                     | 0.2                     | 1.3                     | %    |  |

| Differential Phase      |                          | 1.6                     | 4.0                     | 1.8                     | 2.1                     | 0.9                     | 0.6                     | 0.05                    | deg  |  |

| Open-Loop Gain          | 10kHz                    | 37                      | 37                      | 65                      | 74                      | 69                      | 78                      | 70                      | dB   |  |

| Common-Mode Gain        | 10kHz                    | 6                       | 6                       | -13                     | -19                     | 11                      | -26                     | -1                      | dB   |  |

| Supply Reject. Positive | 1Hz                      | 0                       | -1                      | -33                     | -49                     | 48                      | -45                     | -52                     | dB   |  |

| Supply Reject. Negative | 1Hz                      | -4                      | -6                      | -37                     | -51                     | 56                      | -46                     | -38                     | dB   |  |

| Quiescent Current       | +27°C                    | 2                       | 2                       | 2                       | 2                       | 2                       | 2                       | 2                       | mA   |  |

TABLE I. Important Parameters of the Previously Examined Circuits (numbers correspond to the Figure numbers).

| PARAMETER               |                          | FIGURE                  |                      |                      |                   |                      |      |  |

|-------------------------|--------------------------|-------------------------|----------------------|----------------------|-------------------|----------------------|------|--|

|                         | CONDITION                | 8                       | 9                    | 10                   | 11                | 12                   | UNIT |  |

| Input Offset Voltage    | –25°C<br>+27°C<br>+125°C | 717<br>627<br>453       | 0.6<br>0.9<br>1.8    | 1.1<br>1.0<br>0.6    | 1.7<br>1.6<br>1.2 | 13.2<br>15.5<br>19.2 | mV   |  |

| Input Bias Current      | –25°C<br>+27°C<br>+125°C | -11.3<br>-15.2<br>-22.2 | 23.5<br>23.2<br>22.5 | 23.6<br>23.3<br>22.7 | 8.7<br>8.5<br>8.0 | 2.1<br>1.6<br>0.9    | μA   |  |

| DC Gain                 | +27°C                    | 0.922                   | 0.924                | 0.935                | 0.966             | 0.953                | V/V  |  |

| Input Resistance        | 10kHz                    | 0.023                   | 0.16                 | 1.4                  | 1.1               | 1.1                  | MΩ   |  |

| Input Capacitance       | 10MHz                    | 6.5                     | 2.3                  | 2.0                  | 3.9               | 0.8                  | pF   |  |

| Output Resistance       | 10kHz                    | 12.6                    | 12.8                 | 12.9                 | 6.8               | 8.2                  | Ω    |  |

| Small Frequency Resp.   | 0.1Vp-p                  | 383                     | 193                  | 195                  | 254               | 850                  | MHz  |  |

| Large Frequency Resp.   | 1Vp-p                    | 315                     | 180                  | 175                  | 234               | 760                  | MHz  |  |

| Slew Rate               | 1Vp-p                    | 490                     | 310                  | 273                  | 466               | 1210                 | V/µs |  |

| Differential Gain       | 1Vp-p<br>5MHz            | 5.8                     | 4.7                  | 4.4                  | 1.0               | 0.71                 | %    |  |

| Differential Phase      |                          | 0.07                    | 0.09                 | 0.014                | 0.19              | 0.026                | deg. |  |

| Supply Reject. Positive | 1Hz                      | -74                     | -44                  | -71                  | -70               | -49                  | dB   |  |

| Supply Reject. Negative | 1Hz                      | -37                     | -45                  | -72                  | -72               | -52                  | dB   |  |

| Quiescent Current       | +27°C                    | 2                       | 2                    | 2                    | 2                 | 2                    | mA   |  |

TABLE II. Important Parameters of the Previously Examined Circuits.

[1] Lehmann, K; <u>Elektronik Industrie 90</u>, Quasiideale Stromquelle, Vol. 1, p.70.

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated