## Using TI's CDCVF2310 and CDCVF25081 with TLK1501 Serial Transceiver

Kal Mustafa/Roger Chan

High Performance Analog

#### ABSTRACT

This test report discusses jitter transfer of TI's CDCVF2310 and CDCVF25081 clock drivers when driving TI's TLK1501 serial gigabit transceiver at 600 Mbit/sec. This application report summarizes the peak-to-peak and RMS jitter measurements taken during the testing of the clock drivers with the TLK1501. The CDCVF2310 is a high-performance clock buffer that provides 10 low-skew copies of CLK at 2.5 V or 3.3 V. The CDCVF25081 is a phase-lock loop clock driver that provides eight copies of zero-delay CLK. The CDCVF25081 operates from a nominal supply voltage of 3.3 V.

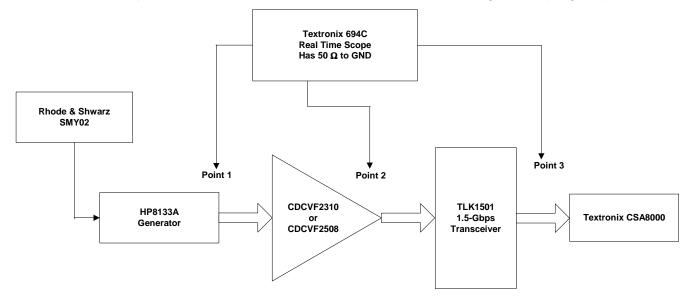

#### **Test Setup**

The block diagram of the test setup is shown in Figure 1. The clock source was provided by a HP8133A at 30 MHz. The clock was then driven into TLK1501 by either CDCVF2310 or CDCVF25081. Jitter measurements were taken at point 1, point 2, and point 3. A PRBS 2^7-1 pattern was generated by TLK1501 with the clock provided by the CDCVF2310 clock driver and the transmit jitter was then measured with a Tektronix CSA8000 digital sampling scope.

Transmission lines usually have  $50-\Omega$  characteristic impedance. The transmitted signals should be controlled such that surplus energy is absorbed at either the source or the load end of the line, preventing reflection. The termination method used in this report was a  $50-\Omega$  source termination for both clock drivers (CDCVF2310 and CDCVF25081), which are included on-chip and thus no external termination were required.

## **Test Results**

The TLK1501 was tested with the CDCVF2301 clock driver. The jitter at the output of HP8133A, CDCVF2310, and TLK1501 is summarized in Table 1. The total peak-peak jitter at the output of the Tek8133A was ~16 ps at 30 MHz. With the 30-MHz clock from the HP8133A, the CDCVF2310 provides a LVTTL clock with peak-to-peak total jitter of 20 ps, which was below the TLK1501 requirement of  $\leq$ 40-ps peak-to-peak.

| Reference Clock                                               | Period Jitter (ps) |       |                 | Comments              |

|---------------------------------------------------------------|--------------------|-------|-----------------|-----------------------|

|                                                               | PP                 | RMS   | V_Amplitude (V) |                       |

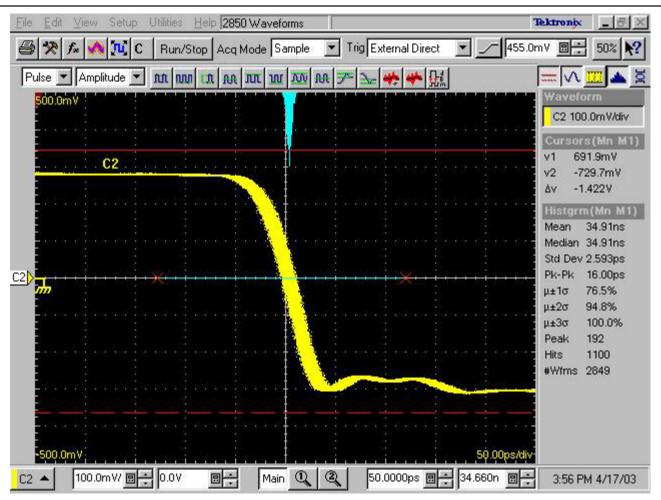

| Rohde & Schwarz                                               | 16                 | 2.593 | 1.422           | HP8133A set at:       |

| SMY02 +HP8133A                                                |                    |       |                 | V <sub>IH</sub> = 2 V |

| With 6-dB attenuator                                          |                    |       |                 | $V_{IL} = 0.8 V$      |

|                                                               |                    |       |                 | (See Figure 2)        |

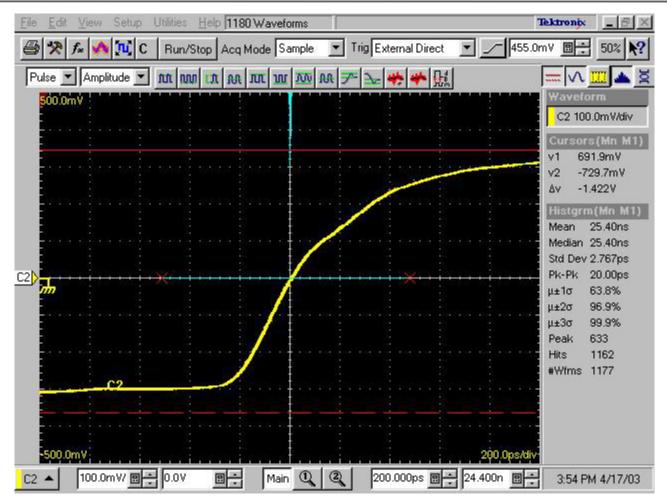

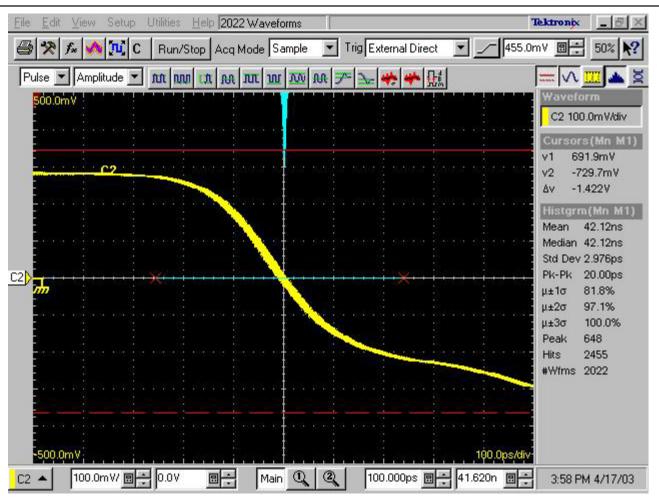

| Rohde & Schwarz                                               | 20 (rising edge)   | 2.767 | 1.422           | HP8133A set at:       |

| SMY02 +HP8133A                                                | 20(falling edge)   | 2.976 | 1.422           | $V_{IH} = 2 V$        |

| + CDCVF2310                                                   |                    |       |                 | $V_{IL} = 0.8 V$      |

| Without 6-dB attenuator                                       |                    |       |                 | (See Figure 3, 4)     |

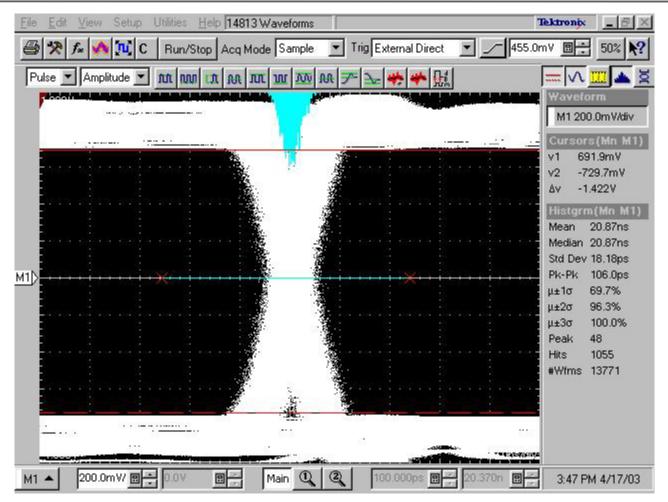

| Rohde & Schwarz<br>SMY02 +HP8133A<br>+ CDCVF2310<br>+ TLK1501 | 112                | 17.6  | 1.422           | HP8133A set at:       |

|                                                               |                    |       |                 | $V_{IH} = 2 V$        |

|                                                               |                    |       |                 | $V_{IL} = 0.8 V$      |

|                                                               |                    |       |                 | (See Figure 5)        |

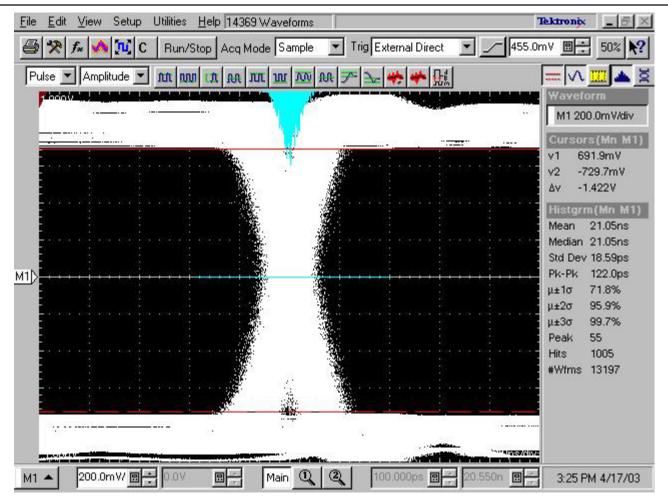

| Rohde & Schwarz<br>SMY02 +HP8133A<br>+ TLK1501                | 122                | 18.59 | 1.422           | HP8133A set at:       |

|                                                               |                    |       |                 | V <sub>IH</sub> = 2 V |

|                                                               |                    |       |                 | $V_{IL} = 0.8 V$      |

|                                                               |                    |       |                 | (See Figure 6)        |

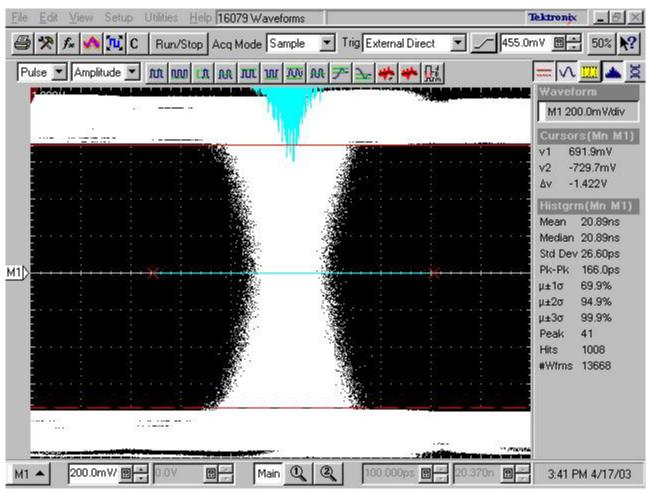

| Rohde & Schwarz                                               |                    |       |                 | HP8133A set at:       |

| SMY02 +HP8133A                                                | 166                | 26.6  | 1.422           | $V_{IH} = 2 V$        |

| + CDCVF25081                                                  |                    |       |                 | $V_{IL} = 0.8 V$      |

| (Zero-Delay PLL)                                              |                    |       |                 | (See Figure 7)        |

| + TLK1501                                                     |                    |       |                 |                       |

# Table 1.Jitter Result With CDCVF2310 Driving TLK1501 at<br/>600 Mbit/sec (30-MHz Clock)

Figure 2 through Figure 7 show the zero crossings of the eyes captured for each case in Table 1 using the CSA8000. There was no degradation in performance when driving the clock with the CDCVF2310. The following graph shows that the CDCVF2310 is able to drive the TLK1501 with less than the 40-ps peak-to-peak input jitter. The TLK1501 output jitter in PRBS data pattern is below 0.1 UI (166.67 ps), the output specification at 600 Mbit/sec.

## TEXAS INSTRUMENTS

Figure 2. Zero Crossing of Data Eye at 600 Mbit/sec: R&S SMY02→HP8133A

#### SCAA064

**TEXAS**

**INSTRUMENTS**

Figure 3. Zero Crossing of Data Eye at 600 Mbit/sec: R&S SMY02→HP8133A→CDCVF2310 Rising Edge

## TEXAS INSTRUMENTS

Figure 4. Zero Crossing of Data Eye at 600 Mbit/sec: R&S SMY02→HP8133A→CDCVF2310 Falling Edge

Figure 5. Zero Crossing of Data Eye at 600 Mbit/sec: R&S SMY02→HP8133A→CDCVF2310→TLK1501

## TEXAS INSTRUMENTS

#### SCAA064

#### Figure 6. Zero Crossing of Data Eye at 600 Mbit/sec: R&S SMY02→HP8133A→TLK1501

The TLK1501 was then tested with CDCVF25081, a phased-lock loop clock driver. The clock provided by CDCVF25081 had more jitter (166 ps) at 30MHz. Figure 7 was the zero crossings of the eyes captured by the CSA8000 with the CDCVF25081 clock driver. The TLK1501 output jitter increased to 166 ps in this setup.

#### Figure 7. Zero Crossing of Data Eye at 600 Mbit/sec: RS SMY02→HP8133A→CDCVF25081→ TLK1501

For testing purpose, we ran a PRBS 2^7-1 data pattern from the TLK1501 driver through 72 inches, 5 mil wide trace and loopback to the TLK1501 with both CDCVF2310 and CDCVF25081. No error was reported in both cases.

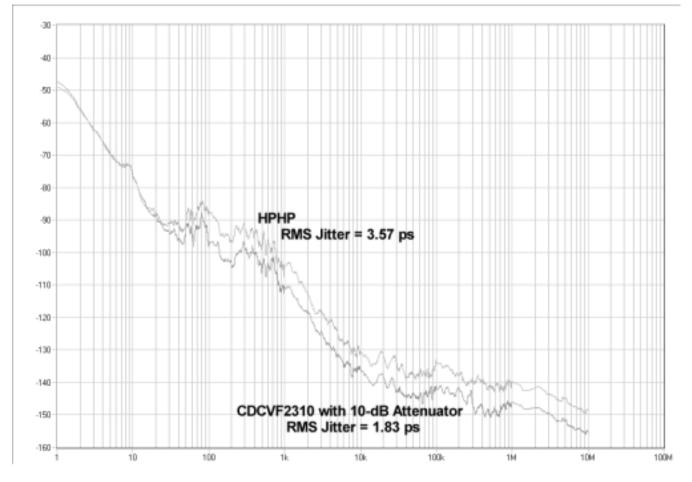

## **Phase Noise Plots**

Figure 8. Phase Noise of HP8133A and CDCVF2310 (12 kHz – 10 MHz)

## Conclusion

The CDCVF2310 is able to drive the TLK1501 and meets the jitter requirements without any problem. CDCVF2310 is recommended for applications that need high clock fan out (1:10) but can tolerate a small amount of clock skew (<100 ps). A phase-locked loop-based clock driver like the CDCVF25081 is not recommended as the clock driver for TLK1501.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated