# **Texas Instruments Voltage-Level-Translation Devices**

Nadira Sultana and Chris Cockrill

Standard Linear & Logic

#### ABSTRACT

In electronic systems design, there is a need to provide an interface between different voltage levels. Texas Instruments offers four split-rail bus transceivers with dual voltage-supply inputs. These transceivers allow translation between 3.3-V LVTTL/LVCMOS and 5-V CMOS, 2.5-V CMOS and 5-V CMOS, and 2.5-V CMOS and 3.3-V LVTTL/LVCMOS. These devices are the SN74LVCC3245A, SN74LVC4245A, SN74LVCC4245A, and SN74ALVC164245. This application report discusses the use of these devices to achieve successful voltage translation.

#### Contents

| Introduction                         | . 2 |

|--------------------------------------|-----|

| Device Description                   | . 3 |

| Dual-Supply Bus Transceivers         | . 3 |

| Configurable-Output Bus Transceivers | . 5 |

| Features and Benefits                | . 7 |

| Power-Up Considerations              | . 7 |

| Conclusion                           | 12  |

| Glossary                             | 12  |

#### **List of Figures**

| 1  | Switching Standards                                  | . 2 |

|----|------------------------------------------------------|-----|

| 2  | Comparison of Switching Standards                    | . 3 |

| 3  | SN74LVC4245A Pinout                                  | . 4 |

| 4  | SN74ALVC164245 Pinout                                | . 4 |

| 5  | SN74LVCC3245A Pinout                                 | . 5 |

| 6  | SN74LVCC4245A Pinout                                 | . 6 |

| 7  | SN74LVC4245A I <sub>CCA</sub> and I <sub>CCB</sub>   | . 8 |

| 8  | SN74LVCC4245A I <sub>CCA</sub> and I <sub>CCB</sub>  | . 9 |

| 9  | SN74LVCC3245A I <sub>CCA</sub> and I <sub>CCB</sub>  | 10  |

| 10 | SN74ALVC164245 I <sub>CCA</sub> and I <sub>CCB</sub> | 11  |

### List of Tables

| 1 | Possible Voltage-Translation Combinations          | 6 |

|---|----------------------------------------------------|---|

| 2 | Features and Benefits of Level-Translation Devices | 7 |

| 3 | Power-Up Sequence for Level-Translation Devices    | 7 |

# Introduction

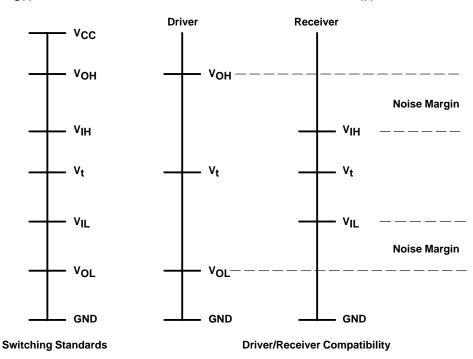

The simultaneous use of different supply-voltage levels has led to the need for voltage translation. In some cases, the logic devices are compatible with the different voltage levels, while in other cases they are not. To have switching compatibility between a driver and a receiver, the output of the driver must be compliant with the input of the receiver.  $V_{OL}$  of the driver should be equal to, or less than,  $V_{IL}$  of the receiver. To establish a high-level signal at the receiver,  $V_{OH}$  of the driver should be greater than, or equal to,  $V_{IH}$  (see Figure 1).

Figure 1. Switching Standards

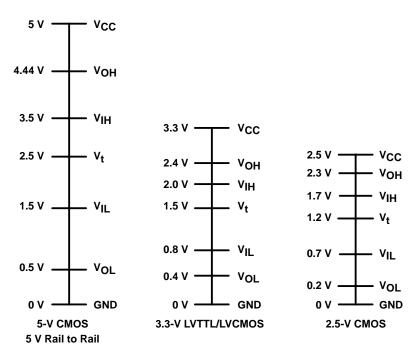

While translating from 3.3-V LVTTL/LVCMOS to 5-V CMOS, V<sub>IH</sub> for 5-V CMOS is 3.5 V, whereas V<sub>OH</sub> for 3.3-V LVTTL is 2.4 V (see Figure 2).

### Figure 2. Comparison of Switching Standards

Thus, standard 3.3-V devices cannot achieve this type of translation. Texas Instruments split-rail devices have two separate voltage supplies, one at each port. These devices allow for translation between 3.3-V LVTTL/LVCMOS to 5-V CMOS, 2.5-V CMOS to 5-V CMOS, 2.5-V CMOS to 3.3-V LVTTL/LVCMOS, and vice versa.

## **Device Description**

### **Dual-Supply Bus Transceivers**

The SN74LVC4245A (see Figure 3) is an 8-bit (octal) noninverting bus transceiver that has two power-supply rails. The A port is set at 5 V, while the B port is set at 3.3 V. This allows for translation from a 3.3-V to a 5-V environment, and vice versa. The data is transmitted from the A bus to the B bus, or the B bus to the A bus, depending on the logic level at the direction-control (DIR) input. If the buses must be isolated, the device can be disabled using the output-enable ( $\overline{OE}$ ) input.

| DB, DW, OR PW PACKAGE<br>(TOP VIEW)                                                                                 |                       |                                                                      |                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| (5 V) V <sub>CCA</sub> [<br>DIR [<br>A1 [<br>A2 [<br>A3 [<br>A4 [<br>A5 [<br>A6 [<br>A7 [<br>A8 [<br>GND [<br>GND [ | 3<br>4<br>5<br>6<br>7 | 24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16<br>15<br>14<br>13 | V <sub>CCB</sub> (3.3 V)<br>V <sub>CCB</sub> (3.3 V)<br>OE<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7<br>B8<br>GND |

The SN74ALVC164245 (see Figure 4) is a 16-bit (dual-octal) noninverting bus transceiver. Its operation is similar to the SN74LVC4245A. The only functional difference is that, in the case of the SN74ALVC164245, V<sub>CCA</sub> is set to 3.3 V, and V<sub>CCB</sub> is set to 5 V, the opposite of the SN74LVC4245A configuration.

| DGG OR DL PACKAGE<br>(TOP VIEW)                                                                                                                                                                      |                                                                                                                         |                                                                                                          |                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 1DIR<br>1B1<br>1B2<br>GND<br>1B3<br>1B4<br>(5 V) V <sub>CCB</sub><br>1B5<br>1B6<br>GND<br>1B7<br>1B8<br>2B1<br>2B2<br>GND<br>2B3<br>2B4<br>(5 V) V <sub>CCB</sub><br>2B5<br>2B6<br>GND<br>2B5<br>2B6 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22 | 48<br>47<br>46<br>45<br>44<br>43<br>42<br>41<br>40<br>39<br>38<br>37<br>36<br>35<br>34<br>33<br>32<br>31 | 1A8<br>2A1<br>2A2<br>GND<br>2A3<br>2A4<br>V <sub>CCA</sub> (3.3 V)<br>2A5 |

| 2DIR [                                                                                                                                                                                               | 24                                                                                                                      | 25                                                                                                       | ] 20E                                                                     |

Figure 4. SN74ALVC164245 Pinout

$V_{CCA}$  is the control side for these two devices. Therefore, the control inputs, DIR (direction) and  $\overline{OE}$  (output enable), should be driven by  $V_{CCA}$  CMOS logic. For the SN74LVC4245A, DIR and  $\overline{OE}$  should be driven by 5-V CMOS logic. For the SN74ALVC16425, DIR and  $\overline{OE}$  should be driven by 3.3-V CMOS logic.

### **Configurable-Output Bus Transceivers**

The SN74LVCC3245A and SN74LVCC4245A are 8-bit (octal) dual-supply bus transceivers with configurable output voltages. This means the data on the B bus follow the value of V<sub>CCB</sub>. In the SN74LVCC3245A, V<sub>CCA</sub> operates between 2.3 V and 3.6 V, while V<sub>CCB</sub> accepts voltages from 3 V to 5.5 V. This device allows translation from 3.3 V to 5 V, 2.5 V to 3.3 V, or 2.5 V to 5 V, and vice versa. The SN74LVCC4245A operates slightly differently. V<sub>CCA</sub> accepts a 5-V supply level, and V<sub>CCB</sub> accepts voltages from 3 V to 5 V. Therefore, this device translates only between 3.3 V and 5 V. SN74LVCC3245A and SN74LVCC4245A are shown in Figure 5 and Figure 6, respectively.

| DB, DW, OR PW PACKAGE<br>(TOP VIEW)                                                                          |                                                       |   |                                                                |   |                                                                              |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---|----------------------------------------------------------------|---|------------------------------------------------------------------------------|

| V <sub>CCA</sub> [<br>DIR ]<br>A1 [<br>A2 ]<br>A3 [<br>A3 ]<br>A3 [<br>A5 ]<br>A5 [<br>A7 ]<br>A8 ]<br>GND ] | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | U | 24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16<br>15<br>14 |   | V <sub>CCB</sub><br>NC<br>OE<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7<br>B8 |

| GND [                                                                                                        | 12                                                    |   | 13                                                             | μ | GND                                                                          |

NC - No internal connection

#### Figure 5. SN74LVCC3245A Pinout

| DB, DW, OR PW PACKAGE<br>(TOP VIEW)                         |  |                                                                      |                                                                                     |

|-------------------------------------------------------------|--|----------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| V <sub>CCA</sub> [<br>DIR [<br>A1 [<br>A2 [<br>A3 [<br>A4 ] |  | 24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16<br>15<br>14<br>13 | V <sub>CCB</sub><br>NC<br>OE<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7<br>B8<br>GND |

|                                                             |  |                                                                      |                                                                                     |

NC - No internal connection

### Figure 6. SN74LVCC4245A Pinout

$V_{CCA}$  is the control side for these two devices. Therefore, the control inputs should be driven by  $V_{CCA}$  CMOS logic. For the SN74LVCC4245A, DIR and  $\overline{OE}$  should be driven by 5-V CMOS logic, and for the SN74LVCC3245A, DIR and  $\overline{OE}$  should be driven by 3.3-V CMOS logic.

Table 1 details possible voltage-translation combinations.

| DEVICE          | SUPPLY VOLTAGE                                                                                                                                  | POSSIBLE<br>VOLTAGE-TRANSLATION COMBINATIONS<br>(TO/FROM) |                    |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------|--|

|                 |                                                                                                                                                 | A PORT                                                    | B PORT             |  |

| SN74LVC4245A    | $\begin{array}{l} 4.5 \ \text{V} \leq \text{V}_{CCA} \leq 5.5 \ \text{V} \\ 2.7 \ \text{V} \leq \text{V}_{CCB} \leq 3.6 \ \text{V} \end{array}$ | 5-V CMOS                                                  | 3.3-V LVTTL/LVCMOS |  |

| SN74ALVC164245A | $\begin{array}{l} 2.7 \ \text{V} \leq \text{V}_{CCA} \leq 3.6 \ \text{V} \\ 4.5 \ \text{V} \leq \text{V}_{CCB} \leq 5.5 \ \text{V} \end{array}$ | 3.3-V LVTTL/LVCMOS                                        | 5-V CMOS           |  |

|                 | $2.3 V \le V_{CCA} \le 3.6 V$<br>$3 V \le V_{CCB} \le 5.5 V$                                                                                    | 2.5-V CMOS                                                | 3.3-V LVTTL/LVCMOS |  |

|                 |                                                                                                                                                 | 2.5-V CMOS                                                | 5-V CMOS           |  |

|                 |                                                                                                                                                 | 3.3-V LVTTL/LVCMOS                                        | 5-V CMOS           |  |

|                 |                                                                                                                                                 | 3.3-V LVTTL/LVCMOS                                        | 3.3-V LVTTL/LVCMOS |  |

| SN74LVCC4245A   | $4.5 \text{ V} \le \text{V}_{CCA} \le 5.5 \text{ V}$                                                                                            | 5-V CMOS                                                  | 3.3-V LVTTL/LVCMOS |  |

| 5N74LV004243A   | $2.7 \text{ V} \leq \text{V}_{CCB} \leq 5.5 \text{ V}$                                                                                          | 5-V CMOS                                                  | 5-V CMOS           |  |

Table 1. Possible Voltage-Translation Combinations

# **Features and Benefits**

Table 2 summarizes the features and corresponding benefits of these level-translation devices.

| FEATURES                                                                                                          | DEVICES                                                          | BENEFITS                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Two separate power-supply rails: $V_{CCB}$ at the B port takes 3.3 V, $V_{CCA}$ at the A port takes 5 V.          | SN74LVC4245A<br>SN74LVCC4245A                                    | Allows 3.3-V to 5-V level translation, and vice versa                                                                                                                                                    |

| Two separate power-supply rails: $V_{CCB}$ at the B port takes 5 V, $V_{CCA}$ at the A port takes 3.3 V.          | SN74ALVC164245                                                   | Allows 3.3-V to 5-V level translation, and vice versa                                                                                                                                                    |

| Two separate power-supply rails: $V_{CCB}$ at the B port takes 5 V, $V_{CCA}$ at the A port takes 2.5 V to 3.3 V. | SN74LVCC3245A                                                    | Allow 3.3-V to 5-V, 2.5-V to 3.3-V, and 2.5-V to 5-V level translations, and vice versa                                                                                                                  |

| Output enable can be used to disable the device.                                                                  | SN74LVC4245A<br>SN74LVCC4245A<br>SN74ALVC164245<br>SN74LVCC3245A | Buses are isolated effectively without false signaling, when necessary.                                                                                                                                  |

| B port is configurable, which means B port is designed to track V <sub>CCB</sub> .                                | SN74LVCC4245A<br>SN74LVCC3245A                                   | Some real-time applications, such as PCMCIA, need full-rail data signals to maximize interface capability, which can be accomplished by tying $V_{CCB}$ of the device to the PCMCIA card voltage supply. |

| Table 2. Features and Benefits of Level-Translation | on Devices |

|-----------------------------------------------------|------------|

|-----------------------------------------------------|------------|

# **Power-Up Considerations**

TI level-translation devices offer an opportunity for successful mixed-voltage signal design. A proper power-up sequence always should be followed to avoid excessive supply current, bus contention, oscillations, or other anomalies caused by improperly biased device pins. Take these precautions to guard against such power-up problems.

- 1. Connect ground before any supply voltage is applied.

- 2. Next, power up the control side of the device (V<sub>CCA</sub> for all four of these devices).

- 3. Tie  $\overline{OE}$  to V<sub>CCA</sub> with a pullup resistor so that it ramps with V<sub>CCA</sub>.

- Depending on the direction of the data path, DIR can be high or low. If DIR high is needed (A data to B bus), ramp it with V<sub>CCA</sub>. Otherwise, keep DIR low.

Table 3 gives a brief summary about the power-up sequence of the devices.

| DEVICE         | V <sub>CCA</sub>          | V <sub>CCB</sub>           | OE                                       |

|----------------|---------------------------|----------------------------|------------------------------------------|

| SN74LVC4245A   | 5 V<br>(power up first)   | 3.3 V<br>(power up second) | Tied to $V_{CCA}$ with a pullup resistor |

| SN74LVCC4245A  | 5 V<br>(power up first)   | 3.3 V<br>(power up second) | Tied to $V_{CCA}$ with a pullup resistor |

| SN74LVCC3245A  | 3.3 V<br>(power up first) | 5 V<br>(power up second)   | Tied to $V_{CCA}$ with a pullup resistor |

| SN74ALVC164245 | 3.3 V<br>(power up first) | 5 V<br>(power up second)   | Tied to $V_{CCA}$ with a pullup resistor |

Table 3. Power-Up Sequence for Level-Translation Devices

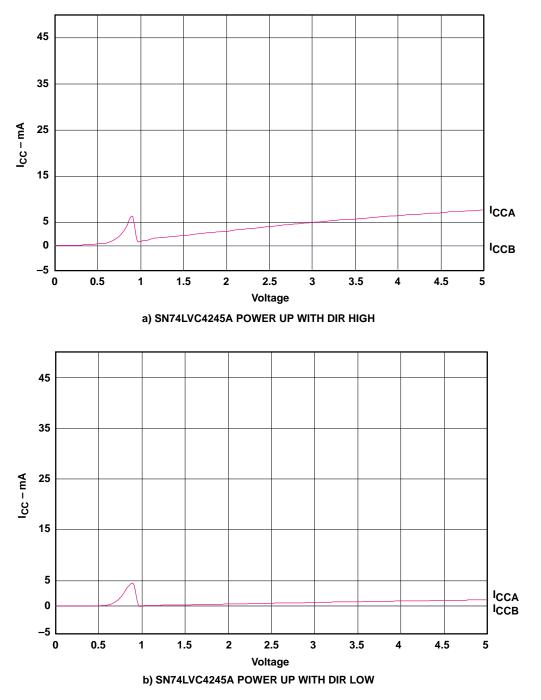

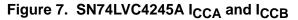

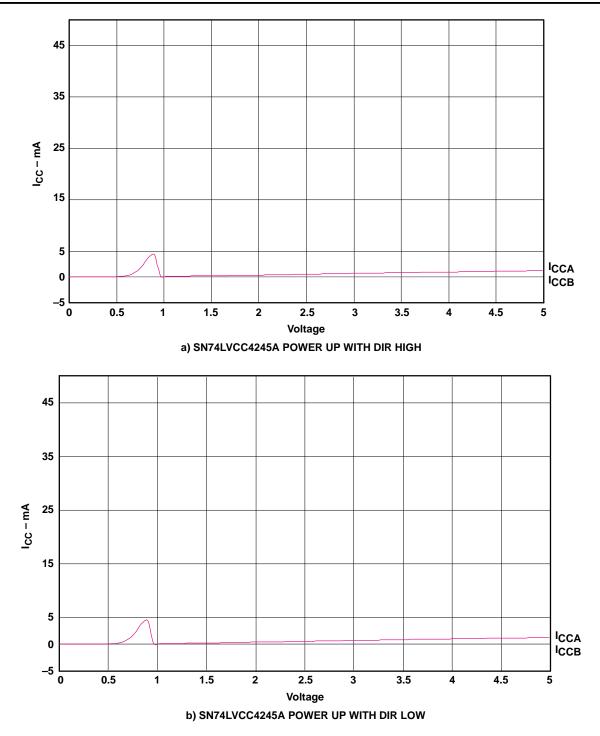

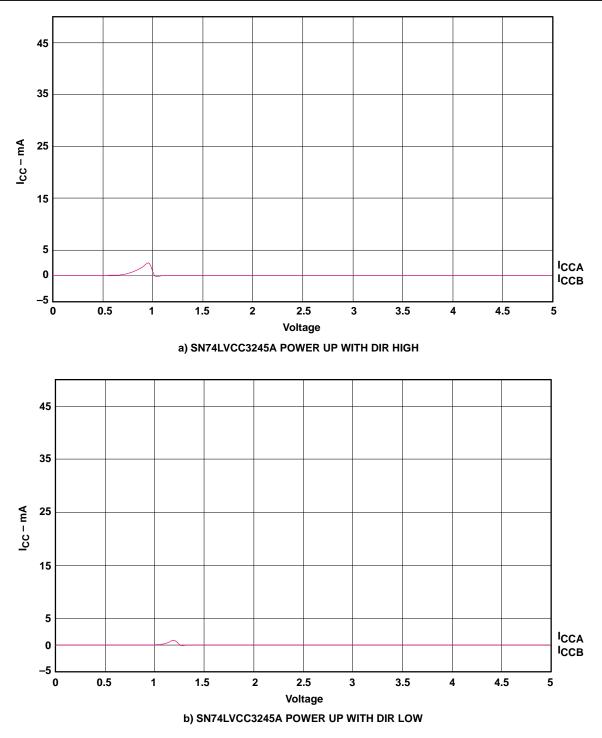

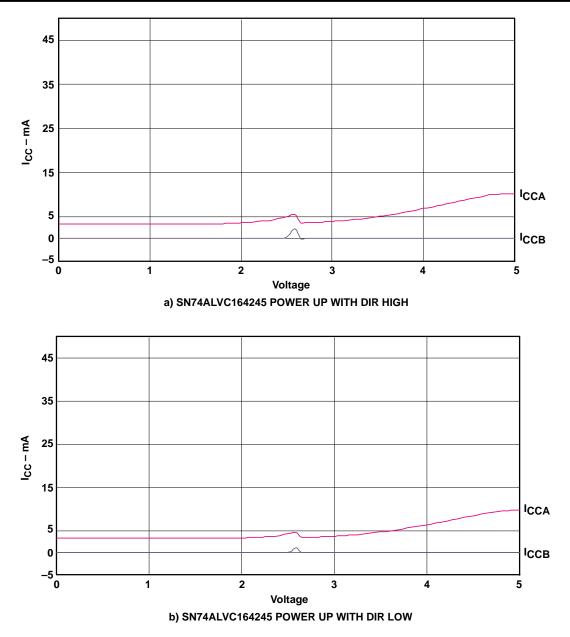

The power-up sequence was tested in the laboratory for all four of these devices. Figures 7–10 show the I<sub>CCA</sub> and I<sub>CCB</sub> for the SN74LVC4245A, SN74LVCC4245A, SN74LVCC3245A, and SN74ALVC164245 devices during power up. V<sub>CCA</sub> was powered up first, then V<sub>CCB</sub> was applied.  $\overline{OE}$  was tied to V<sub>CCA</sub> with a 1-k $\Omega$  pullup resistor. Figures 7(a)–10(a) show the I<sub>CC</sub> with DIR high, and Figures 7(b)–10(b) show the I<sub>CC</sub> with DIR low. If the device is powered up in the correct manner, it draws a reasonable amount of current and ensures the proper functioning of the device.

Figure 8. SN74LVCC4245A  $I_{CCA}$  and  $I_{CCB}$

Figure 9. SN74LVCC3245A ICCA and ICCB

Figure 10. SN74ALVC164245 I<sub>CCA</sub> and I<sub>CCB</sub>

# Conclusion

Texas Instruments offers four split-rail devices, SN74LVC4245A, SN74LVCC4245A, SN74LVCC3245A, and SN74ALVC164245 that can be used for 3.3-V to 5-V, 2.5-V to 3.3-V, and 2.5-V to 5-V translation, and vice versa. These devices are available in octal and Widebus™ configurations, which give the opportunity for designers to choose the optimal part for their applications. These devices have strict power-sequencing requirements that prevent excessive current flow or possible damage to the devices. These stringent requirements sometimes are difficult to meet from a system timing standpoint and may offer little flexibility for partial system power down or other advanced power-saving design techniques. Careful selection of these devices and adoption of an appropriate power-up sequencing technique can lead to a successful mixed-voltage design.

# Glossary

| CMOS            | Complementary metal-oxide semiconductor                   |

|-----------------|-----------------------------------------------------------|

| LVCMOS          | Low-voltage CMOS                                          |

| LVTTL           | Low-voltage TTL (3.3-V power supply and interface levels) |

| V <sub>CC</sub> | Supply voltage                                            |

| $V_{\text{IH}}$ | High-level input voltage                                  |

| $V_{IL}$        | Low-level input voltage                                   |

| V <sub>OH</sub> | High-level output voltage                                 |

| V <sub>OL</sub> | Low-level output voltage                                  |

| Vt              | Threshold voltage                                         |

Widebus is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated