# UCC3819 250-W Power Factor Corrected (PFC) Boost Follower Preregulator Design

Michael O'Loughlin

System Power

#### ABSTRACT

This paper reviews the benefits of a boost follower topology and the design of a 250-W PFC boost follower preregulator.

#### Contents

| 1 | Introduction                                                     | 1 |

|---|------------------------------------------------------------------|---|

| 2 | Power Stage Design                                               | 2 |

| 3 | VAI Output Sensing Circuit with Clamp                            | 9 |

| 4 | Slower Voltage Loop Small Signal Transient Response at High Line | 1 |

| 5 | Reference Design Performance Curves1                             | 3 |

| 6 | References1                                                      | 5 |

### 1 Introduction

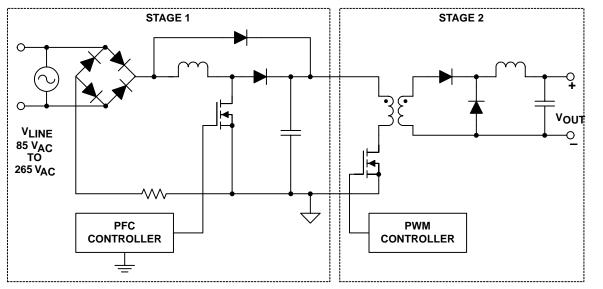

Conventionally PFC off-line power converters are designed with two power stages. The first stage is typically a boost converter. This is because the boost converter topology has continuous input current that can be shaped through the use of a multiplier and average current mode control to achieve near-unity power factor (PF). However the boost converter requires a higher output voltage than the input and requires a second converter to step this voltage down to a useable level.

The boost converter is traditionally designed to have a fixed output voltage greater than the maximum peak line voltage. However, the boost voltage does not have to be well regulated or fixed because the step down converter can be designed to handle the variations in voltage. As long as the boost voltage is above the peak input voltage the converter will regulate properly. There are actually some benefits that can be gained by having the boost voltage vary with variations in peak line voltage (i.e. boost follower preregulator). One is reduced inductor size and the other is lower switch loss at low line operation. This paper reviews the benefits of a boost follower topology and the design of a 250-W PFC boost follower preregulator.

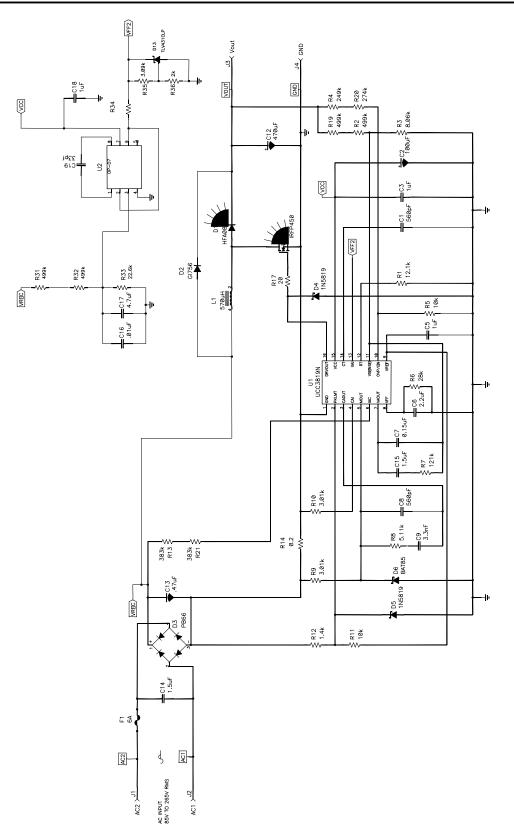

**NOTE:** The reference design was generated using typical parameters rather than worst-case values. Please refer to the table in Figure 1 and Figure 2 for design specifications and component placement. Refer to Table 1 for all variable definitions.

Trademarks are the property of their respective owners.

UDG-02075

|                     | PARAMETER                                | TEST CONDITIONS                                                   | MIN   | TYP   | MAX   | UNITS |

|---------------------|------------------------------------------|-------------------------------------------------------------------|-------|-------|-------|-------|

| VIN                 | Input offset voltage                     |                                                                   | 85    |       | 265   | VRMS  |

| fIN                 | Input frequency                          |                                                                   |       | 60    |       | Hz    |

|                     |                                          | V <sub>IN</sub> = 85 V <sub>RMS</sub>                             | 195   | 205   | 215   |       |

| VOUT dc             | Output voltage                           | $V_{IN} = 265 V_{RMS}$                                            | 370   | 390   | 410   | V     |

| POUT                | Output power                             |                                                                   | 0     |       | 250   | W     |

| VRIPPLE             | Output voltage ripple                    | V <sub>IN</sub> = 85 V <sub>RMS</sub>                             |       |       | 3%    |       |

| η                   | Efficiency                               | P <sub>OUT</sub> = 250 W                                          | 93%   |       |       |       |

| TUD                 |                                          | V <sub>IN</sub> = 85 V <sub>RMS</sub> , P <sub>OUT</sub> = 250 W  |       |       | 5%    |       |

| THD                 | Total harmonic distortion                | V <sub>IN</sub> = 265 V <sub>RMS</sub> , P <sub>OUT</sub> = 250 W |       |       | 7%    |       |

| fosc                | Operating frequency                      |                                                                   |       | 100   |       | kHz   |

| <sup>t</sup> HOLDUP | Hold-up time                             |                                                                   | 16.7  |       |       | ms    |

| VOVP                | Overvoltage protection threshold voltage | V <sub>OUT</sub> = 400 V                                          | 409   | 416   | 422   | V     |

| PLIM                | Power limit                              | VIN = 85 VRMS                                                     | 275   | 360   | 385   | W     |

| ILIM                | Peak current limit                       |                                                                   | 5.335 | 5.500 | 5.665 | А     |

#### Table 1. Design Specifications

Figure 2. Reference Design Schematic

### Table 2. Variable Definitions

| VARIABLE                                                                           | DEFINITIONS                                                                |  |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| CDIODE                                                                             | Boost diode capacitance                                                    |  |

| COSS                                                                               | FET Drain to source capacitance                                            |  |

| GVEA                                                                               | Gain of the voltage amplifier                                              |  |

| D                                                                                  | Duty cycle                                                                 |  |

| fS                                                                                 | PWM switching frequency                                                    |  |

| GPID Control to output gain of the current loop at the desired crossover frequency |                                                                            |  |

| G <sub>PID</sub> (f)                                                               | Control to output gain of the current loop                                 |  |

| G <sub>PS</sub> (f)                                                                | Voltage loop control to output gain                                        |  |

| IMO_MAX(high_line)                                                                 | Peak I <sub>MO</sub> current at high-line input                            |  |

| IRMS_DIODE                                                                         | Boost diode current                                                        |  |

| IRMS_FET                                                                           | RMS current in the FET                                                     |  |

| IRMS_L                                                                             | RMS inductor current                                                       |  |

| Osc_Amplitude                                                                      | Typical oscillator ramp amplitude                                          |  |

| PSEMI                                                                              | Power dissipated by a semiconductor device                                 |  |

| PCON_FET                                                                           | Conduction losses in the FET                                               |  |

| PCOND_DIODE                                                                        | Diode conduction losses                                                    |  |

| PCOSS                                                                              | Power dissipated by the FET's drain to source capacitance                  |  |

| PDIODE                                                                             | Total loss in the boost diode                                              |  |

| PDIODE_CAP                                                                         | Loss due to boost diode capacitance                                        |  |

| PDIODE_TR                                                                          | Boost diode transition loss                                                |  |

| PFET_TR                                                                            | FET transition losses                                                      |  |

| PGATE                                                                              | Power dissipated by the FET gate                                           |  |

| POUT                                                                               | Maximum output power                                                       |  |

| P <sub>Q1</sub>                                                                    | Total FET losses                                                           |  |

| Q <sub>GATE</sub>                                                                  | FET gate charge                                                            |  |

| R <sub>DS(on)</sub>                                                                |                                                                            |  |

| R <sub>θ</sub> CS                                                                  | Thermal impedance case to sink                                             |  |

| RθJC                                                                               | Thermal impedance junction to case                                         |  |

| Rθ <sub>SA</sub>                                                                   | Thermal impedance sink to air                                              |  |

| Тд                                                                                 | Ambient temperature                                                        |  |

| <sup>t</sup> HOLDUP                                                                | Boost capacitor holdup time                                                |  |

| T <sub>J(max)</sub>                                                                | Maximum semiconductor temperature                                          |  |

| <sup>t</sup> F                                                                     | FET fall time                                                              |  |

| <sup>t</sup> R                                                                     | FET rise time                                                              |  |

| <sup>t</sup> RR                                                                    | Reverse recover time for a boost diode                                     |  |

| T <sub>S(f)</sub>                                                                  | Voltage loop frequency response                                            |  |

| V <sub>AI(max)</sub>                                                               | Maximum voltage amplifier reference                                        |  |

| V <sub>AI(min)</sub>                                                               | Minimum voltage amplifier reference voltage                                |  |

| VCLAMP                                                                             | Voltage reference clamp to ensure the boost voltage is not exceeded        |  |

| VEA(max)                                                                           | Maximum voltage amplifier output.                                          |  |

| VEA(min)                                                                           | Minimum voltage amplifier output                                           |  |

| VGATE                                                                              | Gate drive voltage                                                         |  |

| VDROP                                                                              | Amount of voltage the boost capacitor is allowed to drop during holdup.    |  |

| VDROP                                                                              | Trandult of Voltage the boost deputitor is allowed to allop during holdap. |  |

| VARIABLE              | DEFINITIONS                                       |

|-----------------------|---------------------------------------------------|

| V <sub>IN(min)</sub>  | Minimum RMS input voltage                         |

| V <sub>OUT(max)</sub> | Maximum dc output voltage                         |

| VOUT(min)             | Minimum dc output voltage                         |

| VPP                   | Output peak-to-peak ripple voltage                |

| VREF_TL431            | Reference voltage of the TL431                    |

| ΔΙ                    | Change in boost inductor ripple current           |

| η                     | Efficiency                                        |

| %THD                  | Percentage of allowable total harmonic distortion |

## 2 Power Stage Design

#### 2.1 Inductor Selection

The boost inductor is selected based on the maximum allowed ripple current at maximum duty cycle at the peak of minimum line voltage. The following equations can be used to calculate the required inductor for the power stage with ripple current that is 20% of the peak input current. The calculated inductance for this design was roughly 570  $\mu$ H. In traditional application the boost voltage (V<sub>OUT(min)</sub>) would be fixed at roughly 390 V. For the same power levels and input conditions for the traditional boost converter would require and inductance of roughly 1 mH. To make the design process easier the inductor was designed by Cooper Electronics.

$$\Delta I = \frac{P_{OUT} \times \sqrt{2} \times 0.2}{V_{IN (min)}}$$

(1)

$$D = 1 - \frac{V_{OUT (min)} - V_{IN (min)} \times \sqrt{2}}{V_{OUT (min)}}$$

(2)

$$L1 = \frac{V_{IN (min)} \times \sqrt{2} \times D}{\Delta I \times f_{S}}$$

(3)

### 2.2 Boost Switch Selection (D1) and Boost Diode Selection (Q1)

To properly select D1 and Q1 a power budget is generally set for these devices to maintain the desired efficiency goal. Equations (4), (5), and (6) are used to estimate power loss in the switching devices. To meet the power budget for this design an IRFP450 HEX FET and HFA08TB60 fast recovery diode from International Rectifier were chosen for this design to meet the power constraints.

To calculate the loss in Q1:

$$I_{\text{RMS}\_\text{FET}} = \frac{P_{\text{OUT}}}{V_{\text{IN}(\text{min})} \times \sqrt{2}} \times \sqrt{2 - \frac{16 \times V_{\text{IN}(\text{min})} \times \sqrt{2}}{3 \times \pi \times V_{\text{OUT}(\text{min})}}} \qquad I_{\text{RMS}\_L} = \frac{P_{\text{OUT}}}{V_{\text{OUT}(\text{min})}}$$

(4)

$$P_{GATE} = Q_{GATE} \times V_{GATE} \times f_{S}$$

(5)

$$P_{COSS} = \frac{1}{2}C_{OSS} \times \left(V_{OUT(min)}\right)^2 \times f_S$$

(6)

$$P_{COND\_FET} = R_{DS(on)} \times \left(I_{RMS\_FET}\right)^2$$

(7)

$$P_{\text{FET}_{\text{TR}}} = \frac{1}{2} V_{\text{OUT(min)}} \times I_{\text{RMS}_{\text{L}}} \times 0.9 \times (t_{\text{R}} + t_{\text{F}}) \times f_{\text{S}}$$

(8)

$$P_{Q1} = P_{GATE} + P_{COSS} + P_{COND\_FET} + P_{FET\_TR}$$

(9)

To calculate the loss in D1:

$$I_{\text{RMS}\_\text{DIODE}} = \frac{P_{\text{OUT}}}{V_{\text{OUT (min)}}} \times \sqrt{\frac{16 \times V_{\text{OUT (min)}}}{3 \times \pi \times V_{\text{IN(min)}} \times \sqrt{2}}}$$

(10)

$P_{COND\_DIODE} = V_{F} \times I_{RMS\_DIODE}$ (11)

$$P_{DIODE\_CAP} = \frac{C_{DIODE}}{2} \times \left( V_{OUT(min)} \right)^2 \times f_S$$

(12)

$$P_{\text{DIODE}_\text{TR}} = \frac{1}{2} V_{\text{OUT(min)}} \times I_{\text{RMS}_\text{DIODE}} \times (t_{\text{RR}}) \times f_{\text{S}}$$

(13)

$$P_{\text{DIODE}} = P_{\text{COND}_{\text{DIODE}}} + P_{\text{DIODE}_{\text{CAP}}} + P_{\text{COND}_{\text{TR}}}$$

(14)

#### 2.3 Benefits of the Boost Follower Topology on the Power Stage at Low-Line

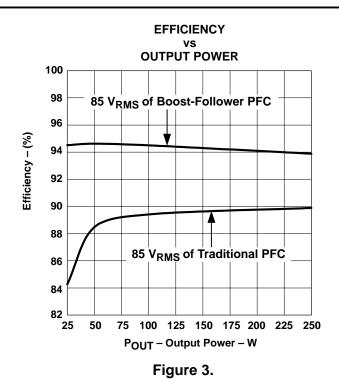

The more traditional PFC preregulator topology has a fixed output voltage that is greater than the peak line voltage. The fixed boost voltage for a universal input is typically set at 390 V. The boost follower is designed so that the output voltage is greater than the peak input voltage. For this design the output tracks the input from 206 V to 390 V. From the equations for transition loss and capacitance loss for the boost switch (Q1), it can be observed that these losses should be less at lower line voltages for the boost follower topology as compared to the traditional preregulator. The calculated losses for Q1 and D1 in the traditional topology were approximately 25 W and the calculated losses for switch and diode for the boost follower was approximately 17.4 W. The boost follower topology should be at least 3% more efficient at low line than the traditional topology. When compared to that of a traditional converter with the same power levels, the finished converter's low-line efficiency is approximately 5% more efficient. (See Figure 3.)

#### 2.4 Heat Sinks

Equation (15) calculates the minimum required thermal impedances of the heat sinks ( $R\theta_{SA}$ ) required for this design. The heat sinks are designed to ensure that the junction tempature stays below 75% of the rated maximum. The heat sinks require a fan capable of forcing 40°C air at 150 LFPM. The heat sink required for Q1 using the traditional topology required an AVVID heat sink part number 53002 that is approximately 4.125 cubic inches. The heat sink for the boost follower topology required an AVVID heat sink part number 531202 of approximately 1.38 cubic inches which is about 66% smaller than the heat sink used in the traditional design.

$$R\theta_{SA} = \frac{T_{J(max)} - T_{A} - P_{SEMI} \times (R\theta_{CS} + R\theta_{JC})}{P_{SEMI}}$$

(15)

### 2.5 Holdup Capacitor Selection

Equation (16) is used to estimate the size of the hold-up capacitor and the maximum allowable RMS current through the boost capacitor. The hold-up capacitor was designed for 16.7 ms of holdup time ( $t_{HOLDUP}$ ) allowing the output 85 V of drop ( $V_{DROP}$ ). For this design the calculated minimum hold-up capacitance was approximately 330  $\mu$ F requiring roughly 1.7 A of RMS current at low-line operation. This minimum calculated capacitance value is roughly double of what is required in the traditional design. This is one of the negative aspects of using a boost follower topology.

$$C12 \ge 2 \times P_{OUT} \times \frac{t_{HOLDUP}}{\left[V_{OUT(min)}\right]^{2} - \left[V_{OUT(min)} - V_{DROP}\right]^{2}}$$

(16)

TEXAS INSTRUMENTS

$$I_{\text{RMS}\_\text{C12}} = \frac{P_{\text{OUT}}}{V_{\text{OUT (min)}}} \times \sqrt{\frac{16 \times V_{\text{OUT (min)}}}{3 \times \pi \times V_{\text{IN(min)}} \times \sqrt{2}} - 1}$$

(17)

#### 2.6 Multiplier Setup

The multiplier is used to shape the input current waveform and must be set up correctly to get proper PFC. Equations (18) and (19) are used to set up the multiplier.

R13 + R21 =

$$\frac{V_{IN(max)} \times \sqrt{2}}{500 \,\mu A}$$

(18)

$$R6 = \frac{1.4 \text{ V}}{\frac{\text{V}_{\text{IN(min)}}}{(\text{R13} + \text{R21}) \times 2} \times 0.9}$$

(19)

Three voltage signals in this circuit, having a 120-Hz ripple component, contribute to input current total harmonic distortion (THD). The voltage feedforward (VFF) of the multiplier is one that contribute to THD. To meet the design goal of less than 5% THD, each signal is allowed to contribute only 1.5% allowable 120-Hz distortion (%THD). To meet the current THD requirements, C6 is set to attenuate the 120-Hz voltage ripple present on the VFF input of the multiplier to 1.5% (%THD) of the VFF pin's voltage range.

$$C6 = \frac{1}{2 \times \pi \times \frac{\% \text{THD}}{66\%} \times 120 \text{ Hz} \times \text{R6}}$$

(20)

#### 2.7 Peak Current Limit

The UCC3819 has a peak current limit comparator that can be set up with a voltage divider using the VREF pin of the PWM controller. R14, R12 and R11 are selected to have the peak limit comparator trip at 110% of the maximum output power to protect Q1. This comparator limits only the current through the switch and not the current drawn by the output.

### 2.8 Power Limiting

Resistor R9 is selected to achieve soft power limiting at maximum output power<sup>[1]</sup>.

$$R9 = \frac{\frac{P_{OUT} \times \sqrt{2}}{\eta \times V_{IN(max)}} \times R14}{I_{MO MAX(high line)}}, \qquad R9 = R10$$

(21)

#### 2.9 Current Amplifier

Equations (22) and (23) are used to compensate the current loop with a desired crossover frequency at 1/10 of the switching frequency. Resistor R8 and capacitor C9 form a zero at the desired crossover frequency that gives an added 45 degrees of phase margin for circuit stability. Capacitor C8 and and resistor R8 form a high-frequency pole to attenuate any high-frequency noise that may be present in the system.

$$G_{\text{PID}} = \frac{V_{\text{OUT(max)}} \times \text{R14}}{2 \times \pi \times \left(\frac{f_{\text{S}}}{10}\right) \times \text{L1} \times \text{Osc}_{\text{Amplitude}}}$$

(22)

$$R8 = \frac{1}{1} \cdot C9 = \frac{1}{1} \cdot C8 = \frac{1}{1} \cdot$$

$$R8 = \frac{1}{G_{\text{PID}}}, C9 = \frac{1}{2 \times \pi \times \left(\frac{f_{\text{S}}}{10}\right) \times R8}, C8 = \frac{1}{2 \times \pi \times \left(\frac{f_{\text{S}}}{2}\right) \times R8}$$

(23)

## 3 VAI Input Sensing Circuit with Clamp

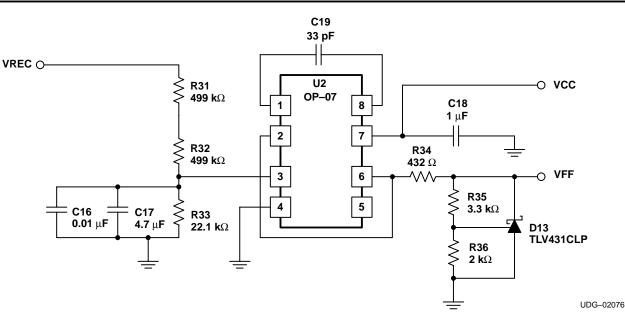

The UCC3819 PWM controller allows the user to set the reference voltage (VAI) externally. It is this feature that allows the designer to use an integrated PWM controller with a boost follower topology. With a few external components, a circuit can be constructed that sets VAI proportional to the input voltage. This reference voltage is then used to make the output voltage track the input voltage. Figure 4 shows the external components that are required to generate the VAI voltage.

Figure 4. VAI Output Sensing Schematic

R31, R32, R33 and C17 form a voltage divider with a single-pole filter that is used to monitor the line voltage. R35, R36, and D13 form a VAI clamp to ensure the boost voltage does not exceed the design specification of 390 V. Equations (24) and (25) can be used to select the proper components for the circuit.

$$V_{AI(min)} = \frac{V_{AI(max)}}{2}$$

(24)

$$R33 = \frac{V_{Al(min)} \times (R31 + R32)}{V_{IN(min)} \times (0.9 - V_{Al(min)})}$$

(25)

The VAI signal includes a 120-Hz component that can contribute to THD. Capacitor C17 is selected to keep its contribution to less than 1.5% THD.

$$C17 = \frac{1}{2 \times \pi \times \frac{V_{AI(max)} \times \% THD}{V_{IN(max)} \times \sqrt{2} \times 66\%} \times 120 \text{ Hz} \times R33}}$$

(26)

Setting up the clamp voltage requires that the divider to the VSENSE pin be set up first.

$$R3 = \frac{V_{AI(min)} \times (R19 + R2)}{V_{OUT(min)} - V_{AI(min)}}$$

(27)

$$V_{\text{CLAMP}} = \frac{V_{\text{OUT(max)}} \times \text{R3}}{\text{R19} + \text{R29} + \text{R3}}$$

(28)

$$R35 = \frac{\left(V_{CLAMP} - V_{REF_{TL431}}\right) \times R36}{V_{REF_{TL431}}}$$

(29)

#### SLUA269

#### 3.1 Voltage Amplifier

The voltage amplifier is compensated to attenuate the 120-Hz boost-ripple voltage ( $V_{PP}$ ) in order to reduce it's contribution to THD.

$$V_{PP} = \frac{\frac{P_{OUT}}{\eta}}{\pi \times 120 \text{ Hz} \times \text{C12} \times \text{V}_{OUT(min)}}$$

(30)

$$G_{VEA} = \frac{\% THD \times \left( V_{EA(max)} - V_{EA(min)} \right)}{V_{PP} \times 100}$$

(31)

$$C8 = \frac{1}{2 \times \pi \times 120 \text{ Hz} \times \text{G}_{\text{VEA}} \times \text{R9}}$$

(32)

$$f_{C} = \sqrt{\frac{P_{OUT}}{\left(V_{EA(max)} - V_{EA(min)}\right) \times \left(V_{OUT(min)}\right) \times 2 \times \pi \times C12}} \times \frac{1}{2 \times \pi \times R9 \times C8}$$

(33)

$$R8 = \frac{1}{2 \times \pi \times \left(\frac{f_{S}}{10}\right) \times C8}$$

(34)

### 4 Slower Voltage Loop Small Signal Transient Response at High Line

Another drawback to using a boost follower topology is the small signal transient response is slower at lower line voltages. Equations (35) through (38) model the voltage loop frequency response of both a boost follower and traditional PFC offline voltage regulator. These equations describe the power stage gain ( $G_{PS(f)}$ ) as inversely proportional to output voltage. In the boost-follower topology the voltage loop is compensated when the boost voltage is at its lowest to ensure circuit stability. As the input voltage increases,  $V_{OUT}$  increases, which decreases the overall loop gain ( $T_{S(f)}$ ). As  $T_{S(f)}$  decreases the loop crosses over at a lower  $f_C$ , resulting in slower transient response. The traditional topology has a fixed output voltage and a fixed  $T_{S(f)}$ , which results in a fixed transient response, independent of line voltage.

$$\mathbf{s}(\mathbf{f}) = \mathbf{j} \times \mathbf{2} \times \mathbf{\pi} \times \mathbf{f} \tag{35}$$

$$G_{PS(f)} = \frac{P_{OUT}}{\left(V_{EA(max)} - V_{EA(min)}\right) \times V_{OUT} \times s(f) \times C12}$$

(36)

$$G_{EA(f)} = \frac{(s(f) \times R8 \times C9 + 1)}{S(f) \times R9 \times (C9 + C8) \times \left[S(f) \times R8 \times \frac{(C9 \times C8)}{(C9 + C8)} + 1\right]}$$

(37)

$$\mathsf{T}_{\mathsf{s}(\mathsf{f})} = -\mathsf{G}_{\mathsf{PS}(\mathsf{f})} \times \mathsf{G}_{\mathsf{EA}(\mathsf{f})}$$

(38)

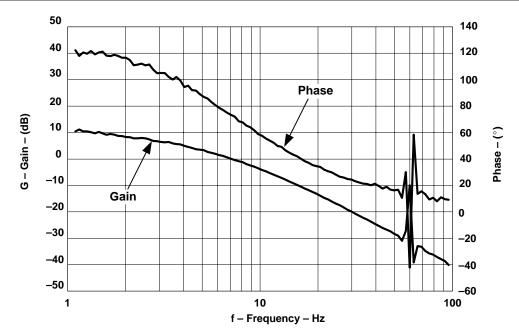

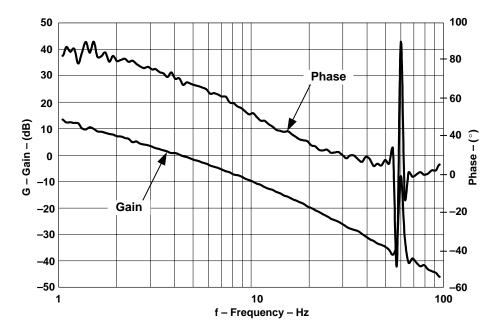

Figures 5 and 6 show the measured voltage loop small-signal frequency response. The small signal transient response at low line is roughly twice as fast as it is at high line.

Figure 5. Voltage Loop Low-Line Frequency Response at Maximum Load

Figure 6. Voltage Loop High-Line Frequency Response at Maximum Load

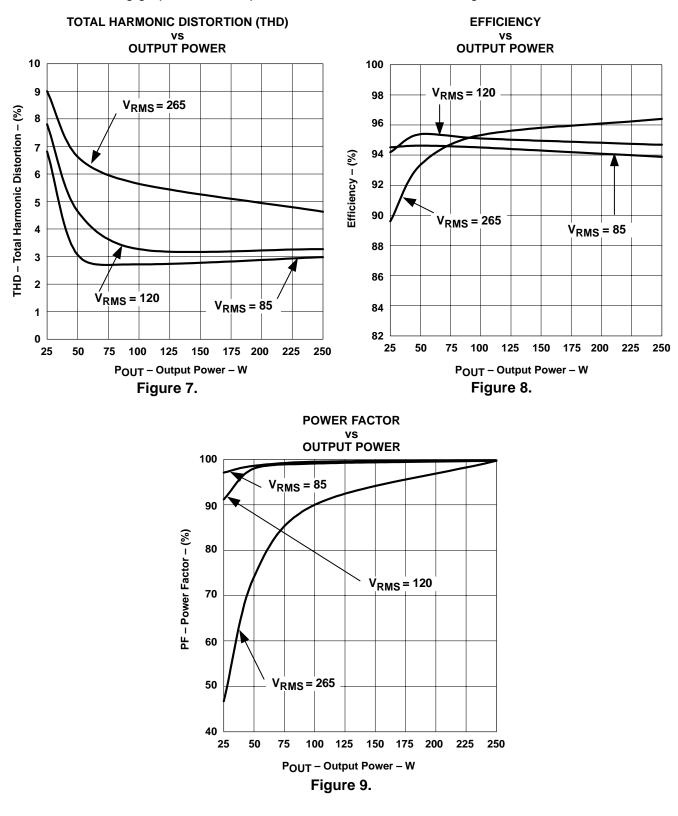

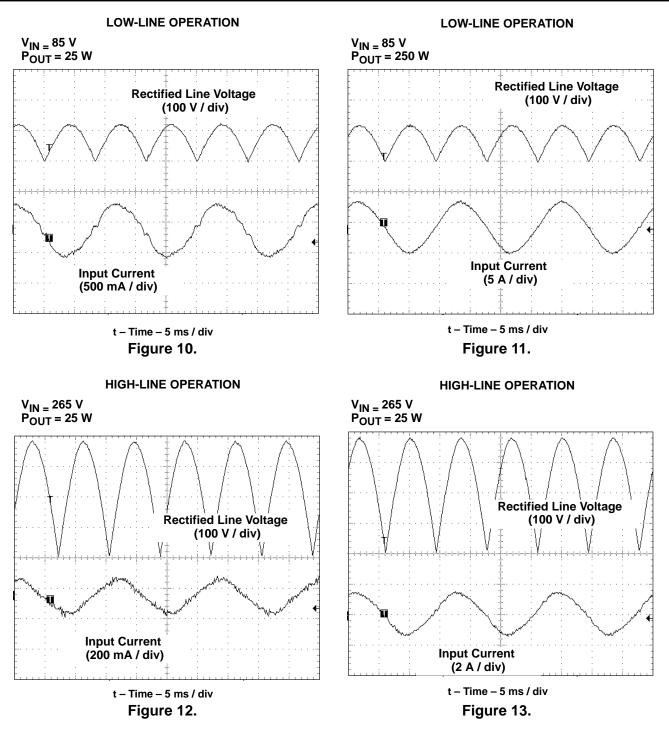

## 5 Reference Design Performance Curves

The following graphs show the performance of the reference design.

#### SLUA269

## 6 References

- 1. Laszlo Balogh, "UCC3854A/B and UCC3855A/B Provide Power Limiting With Sinusoidal Input Current," Texas Instruments Literature No. SLUA196.

- 2. Lloyd Dixon, "*High Power Factor Switching Prergulator Design Optimization*, " Unitrode Power Supply Design Seminar SEM–700, 1990, Topic 7, Texas Instruments Literature No. SLUP093.

- 3. POWER CONVERSION, September 1992 Proceedings, (LIST PUBLICATION HERE) p. 67

- 4. *Practical Considerations in Current Mode Power Supplies*, Application Note, Texas Instruments Literature No. SLUA110.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated