# UCC3895 OUTC/OUTD Asymmetric Duty Cycle Operation

Steve Mappus

System Power

#### ABSTRACT

A small number of current-mode applications using non–synchronous output stages have experienced asymmetric pulse widths on the OUTC and OUTD outputs of the UCC3895. Applications using synchronous rectification and/or voltage mode control typically do not experience this anomaly. For the cost of a single resistor, a simple fix allows reliable and stable operation of the UCC3895.

#### Contents

| 1 | Problem Description | 1 |

|---|---------------------|---|

| 2 | Solution            | 2 |

| 3 | Test Results        | 3 |

| 4 | Summary             | 4 |

Trademarks are the property of their respective owners.

## **1 Problem Description**

In certain applications, asymmetric duty cycle operation can be observed between the OUTC and OUTD outputs of the UCC3895. The asymmetry generally occurs when the UCC3895 is configured for current-mode operation at very light load or start-up conditions. When the output of the UCC3895 error amplifier is approximately 0.875 V, the PWM comparator output can vary in response to a shallow ramp signal sensed at the ramp pin. The current-sense signal plus any slope compensation are summed at the ramp pin of the UCC3895 and can become very shallow during minimum output load current.

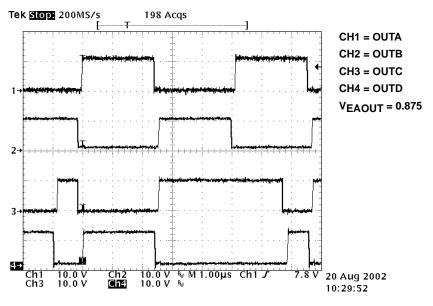

Since there is very little slope definition during light-load operation, the ramp valley can hover near 0 V for a longer period. This results in approximately 0.8 V seen at the inverting input of the PWM comparator. Likewise, since the output of the error amplifier is fed directly to the non-inverting input of the PWM comparator, an error amplifier output of approximately 0.8 V places near equal voltages at both PWM comparator inputs, resulting in non-hysteretic output switching of the PWM comparator. This erratic switching behavior is then passed onto the drive logic for OUTC and OUTD and ultimately can manifest itself as asymmetrical output pulses between OUTC and OUTD. Additionally, since OUTA and OUTB are driven directly from the internal UCC3895 clock, this leg is not subject to asymmetric pulse errors resulting from a shallow ramp signal, as shown in Figure 1. When operating in this mode, typical output waveforms look similar to those shown in Figure 1.

Figure 1. UCC3895 Output Waveforms

### 2 Solution

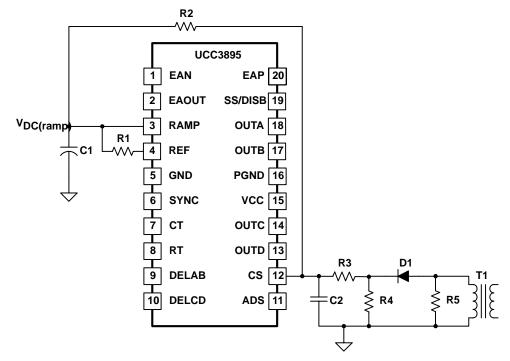

Figure 2. Peak Current Mode Control (slope compensation not shown)

T1 is a current sense transformer operating with D1 and R4 to produce a voltage representation of the current to be sensed. R3 and C2 form a leading edge filter network at pin 12 of the UCC3895. Most UCC3895 current mode applications, including the UCC3895EVM–001 available from Texas Instruments, include these components or similar circuitry.

The UCC3895 contains an internal pull-down MOSFET pulling the RAMP input (pin 3) down to GND. (See block diagram on page 7 of the UCC3895 data sheet, TI Literature No. SLUS157) The gate signal of this MOSFET is derived from the SYNC signal (pin 6) of the UCC3895. By adding a dc offset voltage, V<sub>DC(ramp)</sub>, to the ramp signal at pin 3, a dc voltage is consequently seen at the drain of the internal MOSFET. During the period of time where the ramp valley was shallow at approximately 0 V, there is now some dc voltage for the internal FET to pull down to ground. The action of pulling down the ramp combined with the charging and discharging of C1 produce a more defined ramp signal during start-up and also at minimum output load operation.

1 V of dc offset should be sufficient and can be added by choosing R1 according to equation (1).

$$R1 = \left(\frac{V_{REF}}{V_{DC(ramp)}} - 1\right) \times (R2 + R3 + R4)$$

(1)

This equation is valid for using a current sense transformer configured as shown in Figure 2. For variations on the type of current sensing circuit used, equation (1) would have to be modified accordingly.

#### 3 Test Results

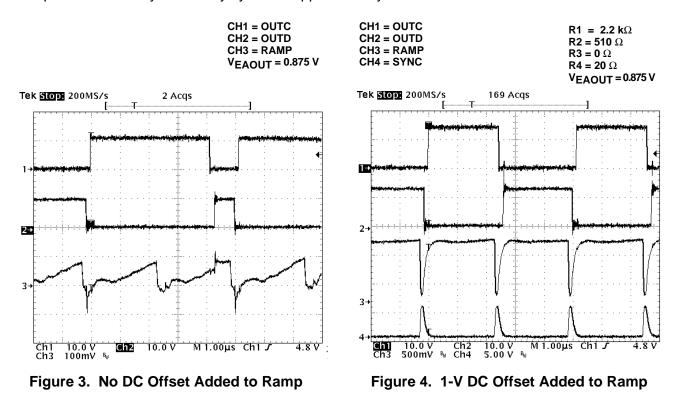

For the circuit shown in Figure 2, a 2.2-k $\Omega$  resistor was added for R1 with C1 equal to 100 pF. As shown in Figure 3, the ramp signal is disturbed during the asymmetric pulse operation of OUTC and OUTD. With the addition of R1, Figure 4 shows the ramp signal with approximately 1 V of dc offset added. The ramp signal is shown being pulled down by the UCC3895 internal MOSFET with each synchronous pulse, and then charging back up through C1. Though not clearly visible, the original ramp signal still exists atop the dc offset voltage. OUTC and OUTD are also shown in stable operation and very small duty cycles of approximately 5% are attainable.

## 4 Summary

The UCC3895 configured in voltage mode does not experience OUTC and OUTD asymmetric output pulses. Also, when using synchronous rectifiers in current mode operation this problem does not typically exist due to the additional reflected secondary current added to the primary side current sense. A small number of current mode applications running at very small duty cycles have experienced asymmetric OUTC and OUTD output pulses. However, for the cost of one resistor, a simple fix allows reliable and stable operation of the UCC3895.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated