# HIGH-SPEED DIFFERENTIAL RECEIVERS

#### **FEATURES**

- Meets or Exceeds the Requirements of ANSI EIA/TIA-644 Standard for Signaling Rates (1) up to 400 Mbps

- Operates With a Single 3.3-V Supply

- -2-V to 4.4-V Common-Mode Input Voltage Range

- Differential Input Thresholds <50 mV With 50 mV of Hysteresis Over Entire Common-Mode Input Voltage Range

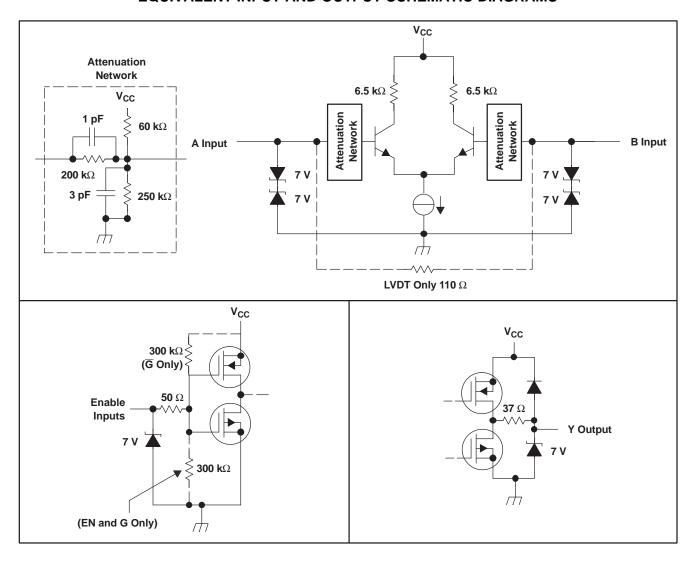

- Integrated 110- $\Omega$  Line Termination Resistors Offered With the LVDT Series

- Propagation Delay Times 4 ns (typ)

- Active Fail Safe Assures a High-Level Output With No Input

- Bus-Pin ESD Protection Exceeds 15 kV HBM

- Inputs Remain High-Impedance on Power Down

- Recommended Maximum Parallel Rate of 200 M-Transfer/s

- Available in Small-Outline Package With 1,27-mm Terminal Pitch

- Pin-Compatible With the AM26LS32, MC3486, or µA9637

#### **DESCRIPTION**

This family of differential line receivers offers improved performance and features that implement the electrical characteristics of low-voltage differential signaling (LVDS). LVDS is defined in the TIA/EIA-644 standard. This improved performance represents the second generation of receiver products for this standard, providing a better overall solution for the cabled environment. This generation of products is an extension to TI's overall product portfolio and is not necessarily a replacement for older LVDS receivers.

Signaling rate, 1/t, where t is the minimum unit interval and is expressed in the units bit/s (bits per second).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **DESCRIPTION (CONTINUED)**

Improved features include an input common-mode voltage range 2 V wider than the minimum required by the standard. This will allow longer cable lengths by tripling the allowable ground noise tolerance to 3 V between a driver and receiver. TI has additionally introduced an even wider input common-mode voltage range of –4 to 5 V in their SN65LVDS/T33 and SN65LVDS/T34.

Precise control of the differential input voltage thresholds now allows for inclusion of 50 mV of input voltage hysteresis to improve noise rejection on slowly changing input signals. The input thresholds are still no more than ±50 mV over the full input common-mode voltage range.

The high-speed switching of LVDS signals almost always necessitates the use of a line impedance matching resistor at the receiving-end of the cable or transmission media. The SN65LVDT series of receivers eliminates this external resistor by integrating it with the receiver. The non-terminated SN65LVDS series is also available for multidrop or other termination circuits.

The receivers can withstand ±15-kV human-body model (HBM) and ±600 V-machine model (MM) electrostatic discharges to the receiver input pins with respect to ground without damage. This provides reliability in cabled and other connections where potentially damaging noise is always a threat.

The receivers also include a (patent pending) fail-safe circuit that will provide a high-level output within 600 ns after loss of the input signal. The most common causes of signal loss are disconnected cables, shorted lines, or powered-down transmitters. This prevents noise from being received as valid data under these fault conditions. This feature may also be used for wired-OR bus signaling.

The intended application of these devices and signaling technique is for point-to-point baseband data transmission over controlled impedance media of approximately 100  $\Omega$ . The transmission media may be printed-circuit board traces, backplanes, or cables. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling to the environment.

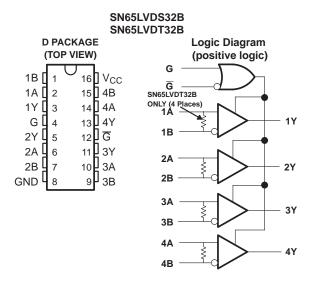

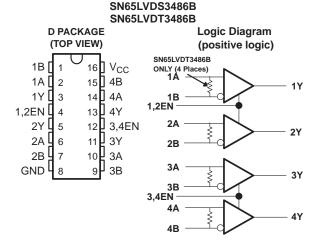

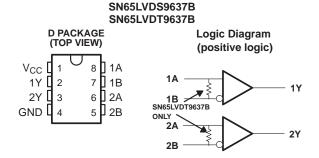

The SN65LVDS32B, SN65LVDT32B, SN65LVDS3486B, SN65LVDT3486B, SN65LVDS9637B, and SN65LVDT9637B are characterized for operation from -40°C to 85°C.

#### **AVAILABLE OPTIONS**

| PART NUMBER <sup>(1)</sup> | NUMBER OF<br>RECEIVERS | TERMINATION<br>RESISTOR | SYMBOLIZATION |

|----------------------------|------------------------|-------------------------|---------------|

| SN65LVDS32BD               | 4                      | No                      | LVDS32B       |

| SN65LVDT32BD               | 4                      | Yes                     | LVDT32B       |

| SN65LVDS3486BD             | 4                      | No                      | LVDS3486      |

| SN65LVDT3486BD             | 4                      | Yes                     | LVDT3486      |

| SN65LVDS9637BD             | 2                      | No                      | DK637B        |

| SN65LVDT9637BD             | 2                      | Yes                     | DR637B        |

(1) Add the suffix R for taped and reeled carrier.

# **FUNCTION TABLES**

#### SN65LVDS32B and SN65LVDT32B

| DIFFERENTIAL INPUT                                   | ENAB   | OUTPUT <sup>(1)</sup> |        |

|------------------------------------------------------|--------|-----------------------|--------|

| A-B                                                  | G      | G                     | Υ      |

| $V_{ID} \ge -32 \text{ mV}$                          | H<br>X | X<br>L                | H<br>H |

| $-100 \text{ mV} < V_{\text{ID}} \le -32 \text{ mV}$ | H<br>X | X<br>L                | ?      |

| V <sub>ID</sub> ≤ −100 mV                            | H<br>X | X<br>L                | L<br>L |

| X                                                    | L      | Н                     | Z      |

| Open                                                 | H<br>X | X<br>L                | H<br>H |

(1) H = high level, L = low level, X = irrelevant, Z = high impedance (off), ? = indeterminate

# SN65LVDS3486B and SN65LVDT3486B

| DIFFERENTIAL INPUT                                   | ENABLES <sup>(1)</sup> | OUTPUT <sup>(1)</sup> |

|------------------------------------------------------|------------------------|-----------------------|

| A-B                                                  | EN                     | Υ                     |

| V <sub>ID</sub> ≥ −32 mV                             | Н                      | Н                     |

| $-100 \text{ mV} < V_{\text{ID}} \le -32 \text{ mV}$ | Н                      | ?                     |

| $V_{ID} \le -100 \text{ mV}$                         | Н                      | L                     |

| X                                                    | L                      | Z                     |

| Open                                                 | Н                      | Н                     |

(1) H = high level, L = low level, X = irrelevant, Z = high impedance (off), ? = indeterminate

#### SN65LVDS9637B and SN65LVDT9637B

| DIFFERENTIAL INPUT                 | OUTPUT <sup>(1)</sup> |

|------------------------------------|-----------------------|

| A-B                                | Y                     |

| V <sub>ID</sub> ≥ -32 mV           | Н                     |

| -100 mV < V <sub>ID</sub> ≤ -32 mV | ?                     |

| V <sub>ID</sub> ≤ -100 mV          | L                     |

| Open                               | Н                     |

(1) H = high level, L = low level, ? = indeterminate

# **EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS**

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)(1)

|                           |                         |                                          | UNIT                            |

|---------------------------|-------------------------|------------------------------------------|---------------------------------|

| V <sub>CC</sub>           | Supply voltage range(2  |                                          | −0.5 V to 4 V                   |

|                           |                         | Enables or Y                             | -0.5 V to V <sub>CC</sub> + 3 V |

|                           | Voltage range           | A or B                                   | -4 V to 6 V                     |

|                           |                         | V <sub>A</sub> - V <sub>B</sub>   (LVDT) | 1 V                             |

|                           | Electrostatic discharge | : A, B, and GND <sup>(3)</sup>           | Class 3, A: 15 kV, B: 600 V     |

|                           | Continuous power diss   | ipation                                  | See Dissipation Rating Table    |

| Storage temperature range |                         | ange                                     | −65°C to 150°C                  |

|                           | Lead temperature 1,6 r  | mm (1/16 inch) from case for 10 seconds  | 260°C                           |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | OPERATING FACTOR <sup>(1)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|---------------------------------------|----------------------------------------------------------------|---------------------------------------|

| D8      | 725 mW                                | 5.8 mW/°C                                                      | 377 mW                                |

| D16     | 950 mW                                | 7.6 mW/°C                                                      | 494 mW                                |

<sup>(1)</sup> This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

#### RECOMMENDED OPERATING CONDITIONS

|                                   |                                            |                 | MIN | NOM | MAX | UNIT |

|-----------------------------------|--------------------------------------------|-----------------|-----|-----|-----|------|

| V <sub>CC</sub>                   | Supply voltage                             |                 | 3   | 3.3 | 3.6 | V    |

| V <sub>IH</sub>                   | High-level input voltage                   | Enables         | 2   |     |     | V    |

| V <sub>IL</sub>                   | Low-level input voltage                    | Enables         |     |     | 8.0 | V    |

| 1.77                              | Name is also as differential in a standard | LVDS            | 0.1 |     | 3   | V    |

| V <sub>ID</sub>                   |                                            | LVDT            |     |     | 0.8 | V    |

| V <sub>I</sub> or V <sub>IC</sub> | Voltage at any bus terminal (separately    | or common-mode) | -2  |     | 4.4 | V    |

| T <sub>A</sub>                    | Operating free-air temperature             |                 | -40 |     | 85  | °C   |

<sup>(2)</sup> All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

<sup>(3)</sup> Tested in accordance with MIL-STD-883C Method 3015.7.

# **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

| PARAMETER                            |                                                                 | TEST CONDITIONS                          | MIN                                                          | TYP <sup>(1)</sup> | MAX | UNIT |      |  |

|--------------------------------------|-----------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------|--------------------|-----|------|------|--|

| V <sub>IT1</sub>                     | Positive-going differential input v                             | oltage threshold                         | V <sub>IB</sub> = -2 V or 4.4 V,                             |                    |     | 50   | >/   |  |

| V <sub>IT2</sub>                     | Negative-going differential input                               | voltage threshold                        | See Figure 1 and Figure 2                                    | -50                |     |      | mV   |  |

| V <sub>IT3</sub>                     | V <sub>IT3</sub> Differential input fail-safe voltage threshold |                                          | See Table 1 and Figure 5                                     | -32                |     | -100 | mV   |  |

| V <sub>ID(HYS)</sub>                 | Differential input voltage hysteres                             | sis, V <sub>IT1</sub> – V <sub>IT2</sub> |                                                              |                    | 50  |      | mV   |  |

| V <sub>OH</sub>                      | High-level output voltage                                       |                                          | I <sub>OH</sub> = -4 mA                                      | 2.4                |     |      | V    |  |

| V <sub>OL</sub>                      | Low-level output voltage                                        |                                          | I <sub>OL</sub> = 4 mA                                       |                    |     | 0.4  | V    |  |

|                                      |                                                                 | 120D 1240CD                              | G or EN at V <sub>CC</sub> , No load, Steady-state           |                    | 16  | 23   |      |  |

| I <sub>CC</sub>                      | Supply current                                                  | '32B or '3486B                           | G or EN at GND                                               |                    | 1.1 | 5    | mA   |  |

|                                      | '9637B                                                          | No load, Steady-state                    |                                                              | 8                  | 12  |      |      |  |

|                                      |                                                                 | V <sub>I</sub> = 0 V, Other input open   |                                                              |                    | ±20 |      |      |  |

|                                      |                                                                 | CNCCLVDC                                 | V <sub>I</sub> = 2.4 V, Other input open                     |                    |     | ±20  | ) µA |  |

|                                      |                                                                 | SN65LVDS                                 | V <sub>I</sub> = −2 V, Other input open                      |                    |     | ±40  |      |  |

| I and a series of (A and B is not a) | land conset (A as D insute)                                     |                                          | V <sub>I</sub> = 4.4 V, Other input open                     |                    |     | ±40  |      |  |

| I <sub>I</sub>                       | Input current (A or B inputs)                                   |                                          | V <sub>I</sub> = 0 V, Other input open                       | ±4                 |     | ±40  |      |  |

|                                      |                                                                 | SN65LVDT                                 | V <sub>I</sub> = 2.4 V, Other input open                     |                    |     | ±40  |      |  |

|                                      |                                                                 | SINDSEVIDI                               | V <sub>I</sub> = −2 V, Other input open                      | ±80                |     | μA   |      |  |

|                                      |                                                                 |                                          | V <sub>I</sub> = 4.4 V, Other input open                     |                    |     | ±80  |      |  |

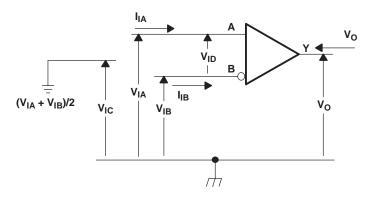

| I <sub>ID</sub>                      | Differential input current                                      | SN65LVDS                                 | $V_{ID}$ = 100 mV, $V_{IC}$ = -2 V or 4.4 V,<br>See Figure 1 |                    |     | ±3   | μΑ   |  |

| 15                                   | (I <sub>IA</sub> - I <sub>IB</sub> )                            | SN65LVDT                                 | V <sub>ID</sub> = 0.2 V, V <sub>IC</sub> = -2 V or 4.4 V     | 1.55               |     | 2.22 | mA   |  |

|                                      |                                                                 | SN65LVDS                                 | $V_A$ or $V_B = 0$ V or 2.4 V, $V_{CC} = 0$ V                |                    |     | ±20  |      |  |

|                                      | Power-off input current                                         | SINDSLVDS                                | $V_A$ or $V_B = -2$ V or 4.4 V, $V_{CC} = 0$ V               |                    |     | ±35  |      |  |

| I <sub>I(OFF)</sub> (A or B inputs)  | (A or B inputs)                                                 | CNCCLVDT                                 | $V_A$ or $V_B = 0$ V or 2.4 V, $V_{CC} = 0$ V                |                    |     | ±30  | μΑ   |  |

|                                      |                                                                 | SN65LVDT                                 | $V_A$ or $V_B = -2$ V or 4.4 V, $V_{CC} = 0$ V               | ±50                |     |      |      |  |

| I <sub>IH</sub>                      | High-level input current (enables                               | )                                        | V <sub>IH</sub> = 2 V                                        |                    |     | 10   | μΑ   |  |

| I <sub>IL</sub>                      | Low-level input current (enables)                               |                                          | V <sub>IL</sub> = 0.8 V                                      |                    |     | 10   | μΑ   |  |

| I <sub>OZ</sub>                      | High-impedance output current                                   |                                          |                                                              |                    |     | ±10  | μA   |  |

| Cı                                   | Input capacitance, A or B input to                              | GND                                      | V <sub>I</sub> = 0.4 sin (4E6πt) + 0.5 V                     |                    | 5   |      | pF   |  |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3 V supply.

# **SWITCHING CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                    | TEST CONDITIONS                      | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|---------------------|--------------------------------------------------------------|--------------------------------------|-----|--------------------|-----|------|

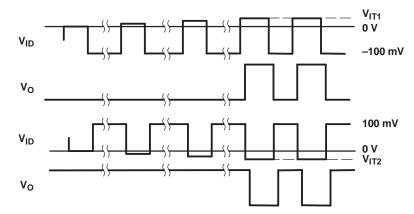

| t <sub>PLH</sub>    | Propagation delay time, low-to-high-level output             | Con Figure 2                         | 2.5 | 4                  | 6   | ns   |

| t <sub>PHL</sub>    | Propagation delay time, high-to-low-level output             | See Figure 3                         | 2.5 | 4                  | 6   | ns   |

| t <sub>d1</sub>     | Delay time, fail-safe deactivate time                        | See Figure 3 and                     |     |                    | 9   | ns   |

| t <sub>d2</sub>     | Delay time, fail-safe activate time                          | Figure 6                             | 0.3 |                    | 1.5 | μs   |

| t <sub>sk(p)</sub>  | Pulse skew ( t <sub>PHL1</sub> - t <sub>PLH1</sub>  )        |                                      |     | 200                |     | ps   |

| t <sub>sk(o)</sub>  | Output skew <sup>(2)</sup>                                   |                                      |     | 150                |     | ps   |

| t <sub>sk(pp)</sub> | Part-to-part skew <sup>(3)</sup>                             | C <sub>L</sub> = 10 pF, See Figure 3 |     |                    | 1   | ns   |

| t <sub>r</sub>      | Output signal rise time                                      |                                      |     | 0.8                |     | ns   |

| t <sub>f</sub>      | Output signal fall time                                      |                                      |     | 0.8                |     | ns   |

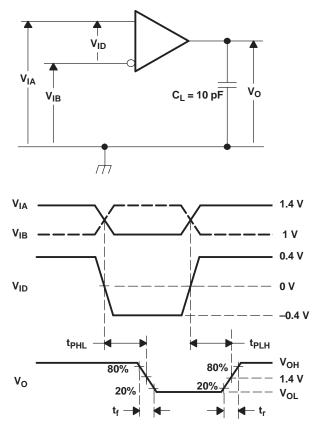

| $t_{PHZ}$           | Propagation delay time, high-level-to-high-impedance output  |                                      |     | 5.5                | 9   | ns   |

| $t_{PLZ}$           | Propagation delay time, low-level-to-high-impedance output   | Con Figure 4                         |     | 4.4                | 9   | ns   |

| t <sub>PZH</sub>    | Propagation delay time, high-impedance -to-high-level output | See Figure 4                         |     | 3.8                | 9   | ns   |

| t <sub>PZL</sub>    | Propagation delay time, high-impedance-to-low-level output   | =                                    |     | 7                  | 9   | ns   |

- (1) All typical values are at 25°C and with a 3.3-V supply.

(2) t<sub>sk(o)</sub> is the magnitude of the time difference between the t<sub>PLH</sub> or t<sub>PHL</sub> of all receivers of a single device with all of their inputs driven together.

- $t_{sk(pp)}$  is the magnitude of the time difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

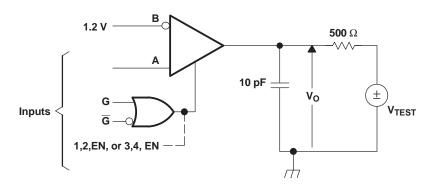

# PARAMETER MEASUREMENT INFORMATION

Figure 1. Voltage and Current Definitions

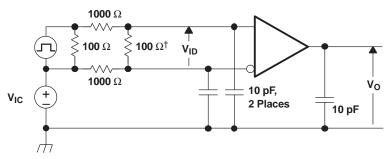

† Removed for testing the LVDT device

NOTE: Input signal of 3 Mpps, duration of 167 ns, and transition time of <1 ns.

Figure 2.  $V_{\text{IT1}}$  and  $V_{\text{IT2}}$  Input Voltage Threshold Test Circuit and Definitions

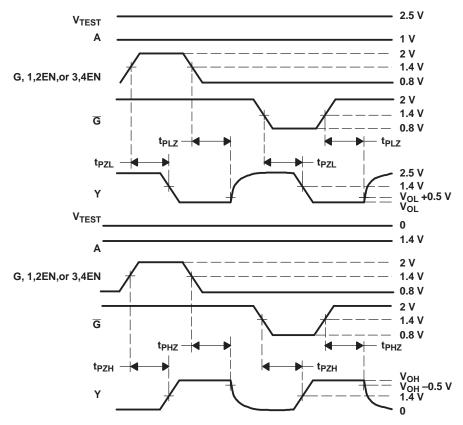

# PARAMETER MEASUREMENT INFORMATION (continued)

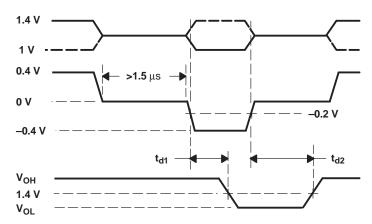

A. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_r \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, Pulsewidth = 10 ±0.2 ns .  $C_L$  includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T.

Figure 3. Timing Test Circuit and Waveforms

# PARAMETER MEASUREMENT INFORMATION (continued)

NOTE: All input pulses are supplied by a generator having the following characteristics:  $t_f$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 0.5 Mpps, Pulsewidth = 500  $\pm 10$  ns .  $C_L$  includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T.

Figure 4. Enable/Disable Time Test Circuit and Waveforms

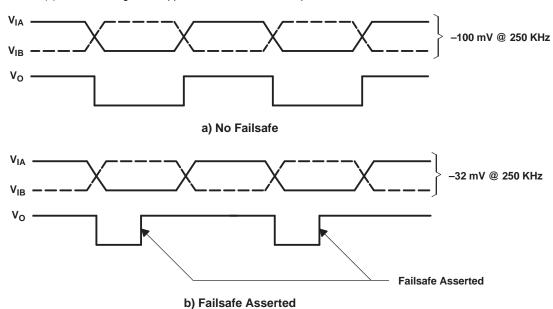

Table 1. Receiver Minimum and Maximum  $V_{\text{IT3}}$  Input Threshold Test Voltages

| APPLIED \            | OLTAGES <sup>(1)</sup> | RESULTANT INPUTS     |                      |        |  |  |  |

|----------------------|------------------------|----------------------|----------------------|--------|--|--|--|

| V <sub>IA</sub> (mV) | V <sub>IB</sub> (mV)   | V <sub>ID</sub> (mV) | V <sub>IC</sub> (mV) | Output |  |  |  |

| -2000                | -1900                  | -100                 | -1950                | L      |  |  |  |

| -2000                | -1968                  | -32                  | -1984                | Н      |  |  |  |

| 4300                 | 4400                   | -100                 | 4350                 | L      |  |  |  |

| 4368                 | 4400                   | -32                  | 4384                 | Н      |  |  |  |

(1) These voltages are applied for a minimum of 1.5  $\mu$ s.

Figure 5.  $V_{\text{IT3}}$  Failsafe Threshold Test

Figure 6. Waveforms for Failsafe Activate and Deactivate

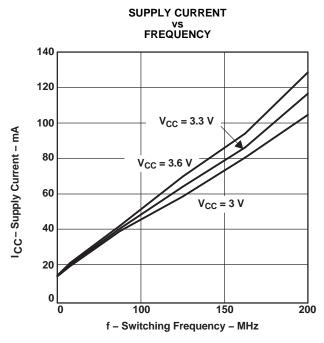

# TYPICAL CHARACTERISTICS

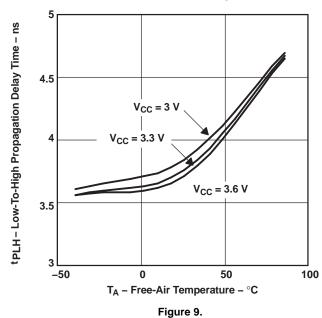

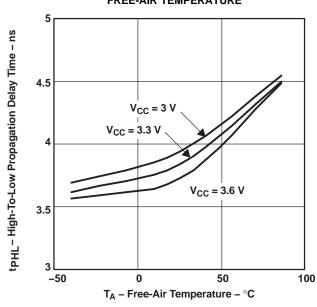

# LOW-TO-HIGH PROPAGATION DELAY TIME vs FREE-AIR TEMPERATURE

Figure 7.

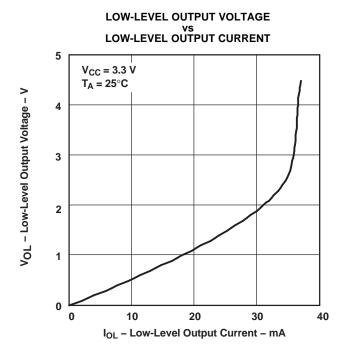

# HIGH-LEVEL OUTPUT VOLTAGE VS HIGH-LEVEL OUTPUT CURRENT

#### HIGH-TO-LOW PROPAGATION DELAY TIME vs FREE-AIR TEMPERATURE

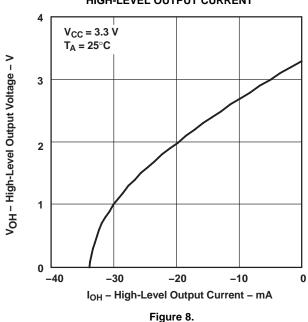

# **TYPICAL CHARACTERISTICS (continued)**

Figure 11.

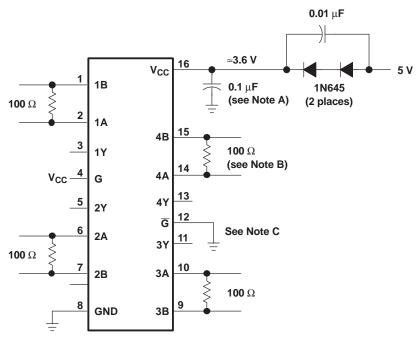

#### APPLICATION INFORMATION

- A. Place a 0.1-µF Z5U ceramic, mica or polystyrene dielectric, 0805 size, chip capacitor between V<sub>CC</sub> and the ground plane. The capacitor should be located as close as possible to the device terminals.

- B. The termination resistance value should match the nominal characteristic impedance of the transmission media with ±10%.

- Unused enable inputs should be tied to V<sub>CC</sub> or GND as appropriate.

Figure 12. Operation with 5-V Supply

#### **RELATED INFORMATION**

IBIS modeling is available for this device. contact the local TI sales office or the TI Web site at www.ti.com for more information.

For more application guidelines, see the following documents:

- Low-Voltage Differential Signaling Design Notes (SLLA014)

- Interface Circuits for TIA/EIA-644 (LVDS) (SLLA038)

- Reducing EMI With LVDS (SLLA030)

- Slew Rate Control of LVDS Circuits (SLLA034)

- Using an LVDS Receiver With RS-422 Data (SLLA031)

- Evaluating the LVDS EVM (SLLA033)

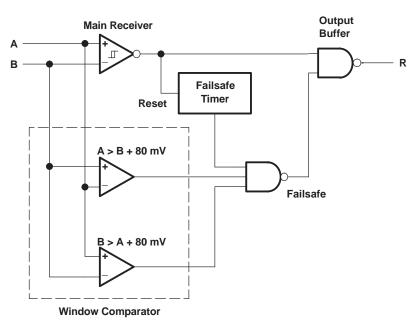

#### **TERMINATED FAILSAFE**

A differential line receiver commonly has a fail-safe circuit to prevent it from switching on input noise. Current LVDS fail-safe solutions require either external components with subsequent reduction in signal quality or integrated solutions with limited application. This family of receivers has a new integrated fail-safe that solves the limitations seen in present solutions. A detailed theory of operation is presented in application note *The Active Fail-Safe Feature of the SN65LVDS32A* (SLLA082).

Figure 13 shows one receiver channel with active fail-safe. It consists of a main receiver that can respond to a high-speed input differential signal. Also connected to the input pair are two fail-safe receivers that form a window comparator. The window comparator has a much slower response than the main receiver and detects when the input differential falls below 80 mV. A 600-ns fail-safe timer filters the window comparator outputs. When fail-safe is asserted, the fail-safe logic drives the main receiver output to logic high.

#### **APPLICATION INFORMATION (continued)**

Figure 13. Receiver With Terminated Failsafe

#### ECL/PECL-to-LVTTL CONVERSION WITH TI'S LVDS RECEIVER

The various versions of emitter-coupled logic (i.e., ECL, PECL and LVPECL) are often the physical layer of choice for system designers. Designers know of the established technology and that it is capable of high-speed data transmission. In the past, system requirements often forced the selection of ECL. Now technologies like LVDS provide designers with another alternative. While the total exchange of ECL for LVDS may not be a design option, designers have been able to take advantage of LVDS by implementing a small resistor divider network at the input of the LVDS receiver. TI has taken the next step by introducing a wide common-mode LVDS receiver (no divider network required) which can be connected directly to an ECL driver with only the termination bias voltage required for ECL termination ( $V_{\rm CC}$  2 V).

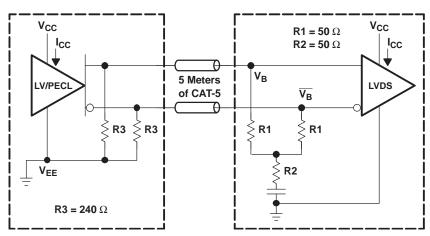

Figure 14 and Figure 15 show the use of an LV/PECL driver driving 5 meters of CAT-5 cable and being received by Tl's wide common-mode receiver and the resulting eye pattern. The values for R3 are required in order to provide a resistor path to ground for the LV/PECL driver. With no resistor divider, R1 simply needs to match the characteristic load impedance of 50  $\Omega$ . The R2 resistor is a small value and is intended to minimize any possible common-mode current reflections.

Figure 14. LVPECL or PECL to Remote Wide Common-Mode LVDS Receiver

# **APPLICATION INFORMATION (continued)**

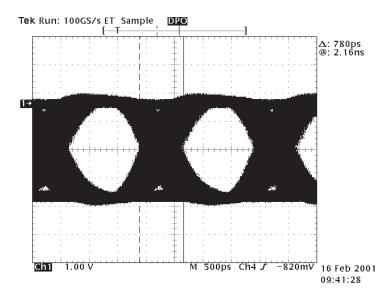

Figure 15. LV/PECL to Remote SN65LVDS32B at 500 Mbps Receiver Output (CH1)

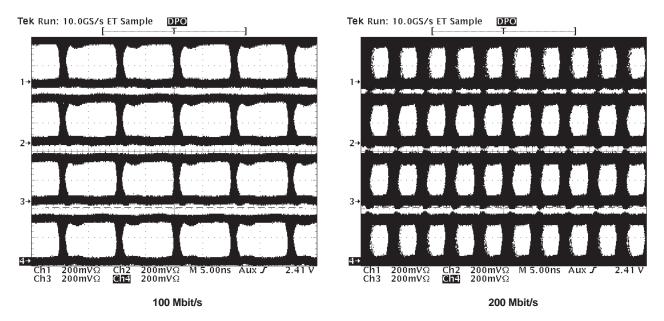

#### **TEST CONDITIONS**

- V<sub>CC</sub> = 3.3 V

- T<sub>A</sub> = 25°C (ambient temperature)

- All four channels switching simultaneously with NRZ data. Scope is pulse-triggered simultaneously with NRZ data.

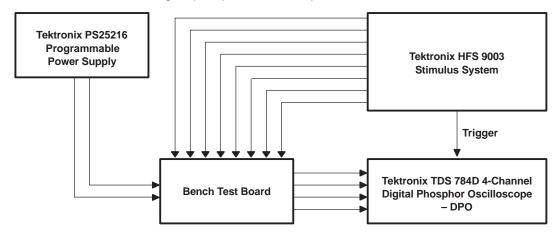

#### **EQUIPMENT**

- Tektronix PS25216 programmable power supply

- Tektronix HFS 9003 stimulus system

- Tektronix TDS 784D 4-channel digital phosphor oscilloscope DPO

Figure 16. Equipment Setup

# **APPLICATION INFORMATION (continued)**

Figure 17. Typical Eye Pattern SN65LVDS32B

www.ti.com 14-Oct-2022

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

| SN65LVDS32BD     | ACTIVE     | SOIC         | D                  | 16   | 40             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | LVDS32B              | Samples |

| SN65LVDS32BDR    | ACTIVE     | SOIC         | D                  | 16   | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | LVDS32B              | Samples |

| SN65LVDS3486BD   | ACTIVE     | SOIC         | D                  | 16   | 40             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | LVDS3486B            | Samples |

| SN65LVDS3486BDR  | ACTIVE     | SOIC         | D                  | 16   | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | LVDS3486B            | Samples |

| SN65LVDS9637BD   | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | DK637B               | Samples |

| SN65LVDS9637BDR  | ACTIVE     | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | DK637B               | Samples |

| SN65LVDT32BD     | ACTIVE     | SOIC         | D                  | 16   | 40             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | LVDT32B              | Samples |

| SN65LVDT32BDR    | ACTIVE     | SOIC         | D                  | 16   | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | LVDT32B              | Samples |

| SN65LVDT3486BD   | ACTIVE     | SOIC         | D                  | 16   | 40             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | LVDT3486B            | Samples |

| SN65LVDT3486BDR  | ACTIVE     | SOIC         | D                  | 16   | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | LVDT3486B            | Samples |

| SN65LVDT9637BD   | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | DR637B               | Samples |

| SN65LVDT9637BDG4 | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | DR637B               | Samples |

| SN65LVDT9637BDR  | ACTIVE     | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | DR637B               | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

# PACKAGE OPTION ADDENDUM

www.ti.com 14-Oct-2022

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 1-May-2024

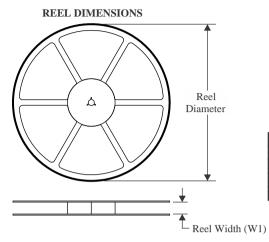

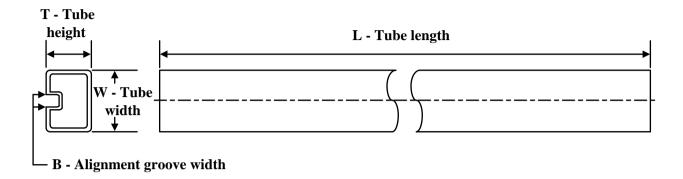

# TAPE AND REEL INFORMATION

# TAPE DIMENSIONS KO P1 BO W Cavity A0

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

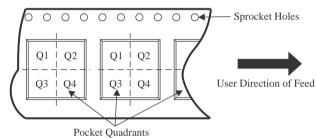

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65LVDS32BDR   | SOIC            | D                  | 16 | 2500 | 330.0                    | 16.4                     | 6.5        | 10.3       | 2.1        | 8.0        | 16.0      | Q1               |

| SN65LVDS3486BDR | SOIC            | D                  | 16 | 2500 | 330.0                    | 16.4                     | 6.5        | 10.3       | 2.1        | 8.0        | 16.0      | Q1               |

| SN65LVDS9637BDR | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| SN65LVDT32BDR   | SOIC            | D                  | 16 | 2500 | 330.0                    | 16.4                     | 6.5        | 10.3       | 2.1        | 8.0        | 16.0      | Q1               |

| SN65LVDT3486BDR | SOIC            | D                  | 16 | 2500 | 330.0                    | 16.4                     | 6.5        | 10.3       | 2.1        | 8.0        | 16.0      | Q1               |

| SN65LVDT9637BDR | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 1-May-2024

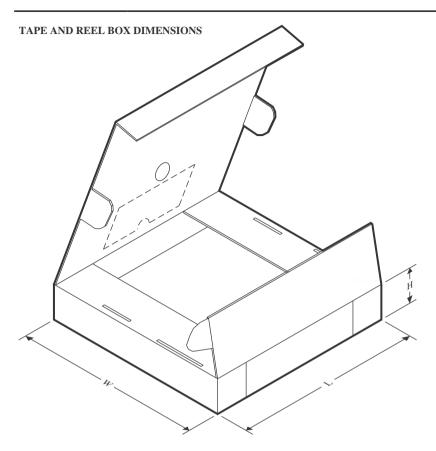

# \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65LVDS32BDR   | SOIC         | D               | 16   | 2500 | 340.5       | 336.1      | 32.0        |

| SN65LVDS3486BDR | SOIC         | D               | 16   | 2500 | 350.0       | 350.0      | 43.0        |

| SN65LVDS9637BDR | SOIC         | D               | 8    | 2500 | 340.5       | 336.1      | 25.0        |

| SN65LVDT32BDR   | SOIC         | D               | 16   | 2500 | 350.0       | 350.0      | 43.0        |

| SN65LVDT3486BDR | SOIC         | D               | 16   | 2500 | 350.0       | 350.0      | 43.0        |

| SN65LVDT9637BDR | SOIC         | D               | 8    | 2500 | 340.5       | 336.1      | 25.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 1-May-2024

# **TUBE**

\*All dimensions are nominal

| Device           | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| SN65LVDS32BD     | D            | SOIC         | 16   | 40  | 507    | 8      | 3940   | 4.32   |

| SN65LVDS3486BD   | D            | SOIC         | 16   | 40  | 505.46 | 6.76   | 3810   | 4      |

| SN65LVDS9637BD   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| SN65LVDS9637BD   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| SN65LVDT32BD     | D            | SOIC         | 16   | 40  | 505.46 | 6.76   | 3810   | 4      |

| SN65LVDT3486BD   | D            | SOIC         | 16   | 40  | 505.46 | 6.76   | 3810   | 4      |

| SN65LVDT9637BD   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| SN65LVDT9637BD   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| SN65LVDT9637BDG4 | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| SN65LVDT9637BDG4 | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

# **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated