SPRS038 – JANUARY 1996

- Highest Performance Floating-Point Digital Signal Processor (DSP)

- 320C40-60:

33-ns Instruction Cycle Time,

330 MOPS, 60 MFLOPS,

30 MIPS, 384M Bytes/s

- '320C40-50: 40-ns Instruction Cycle Time

- '320C40-40:

- 50-ns Instruction Cycle Time

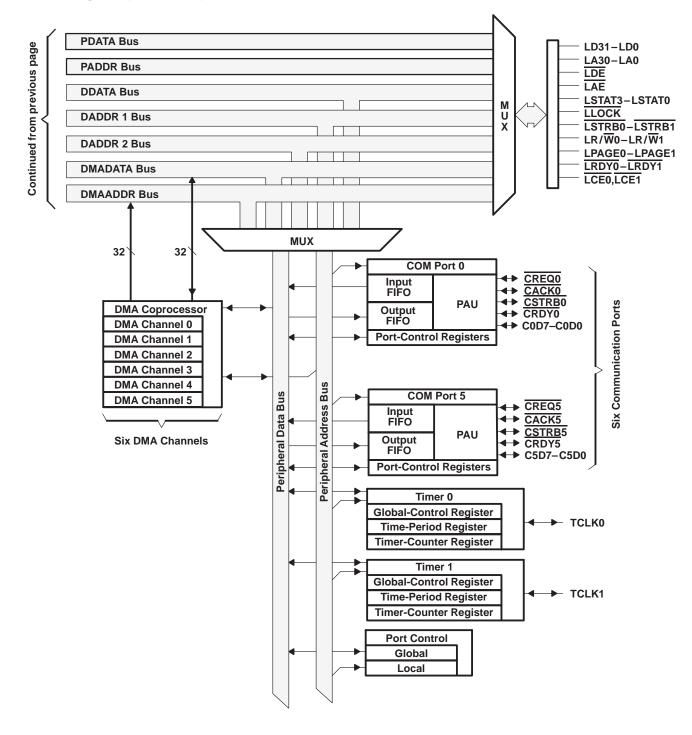

- Six Communications Ports

- Six-Channel Direct Memory Access (DMA) Coprocessor

- Single-Cycle Conversion to and From IEEE-754 Floating-Point Format

- Single Cycle, 1/x,  $1/\sqrt{x}$

- Source-Code Compatible With TMS320C3x

- Single-Cycle 40-Bit Floating-Point, 32-Bit Integer Multipliers

- Twelve 40-Bit Registers, Eight Auxiliary Registers, 14 Control Registers, and Two Timers

- IEEE 1149.1<sup>†</sup> (JTAG) Boundary Scan Compatible

- Two Identical External Data and Address Buses Supporting Shared Memory Systems and High Data-Rate, Single-Cycle Transfers:

- High Port-Data Rate of 120M Bytes/s ('C40-60) (Each Bus)

- 16G-Byte Continuous Program/Data/Peripheral Address Space

- Memory-Access Request for Fast, Intelligent Bus Arbitration

- Separate Address-Bus, Data-Bus, and Control-Enable Pins

- Four Sets of Memory-Control Signals Support Different Speed Memories in Hardware

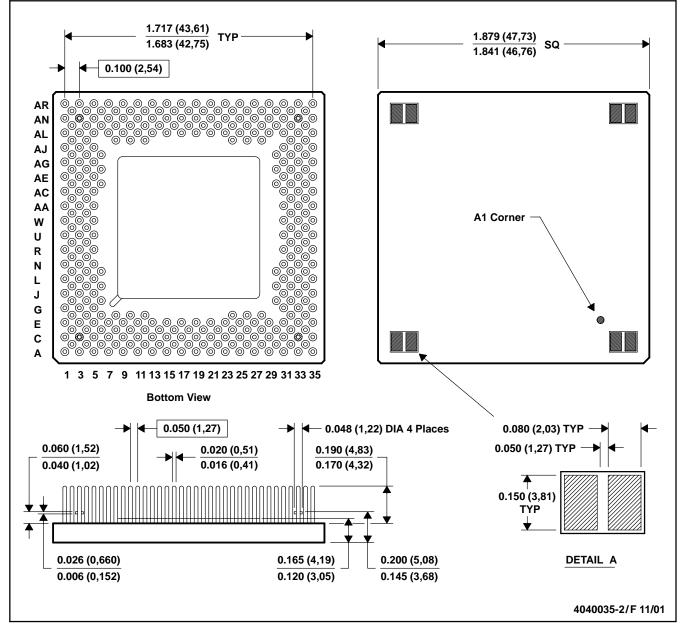

- 325-Pin Ceramic Grid Array (GF Suffix)

- Fabricated Using 0.72-µm Enhanced Performance Implanted CMOS (EPIC™) Technology by Texas Instruments (TI™)

- Software-Communication-Port Reset

- NMI With Bus-Grant Feature

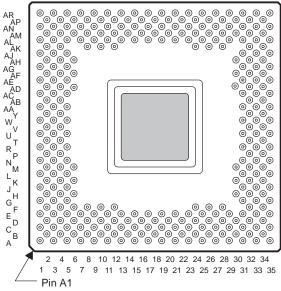

325-PIN GF GRID ARRAY PACKAGE (BOTTOM VIEW)<sup>‡</sup>

<sup>‡</sup> See Pin Assignments table and Pin Functions table for location and description of all pins.

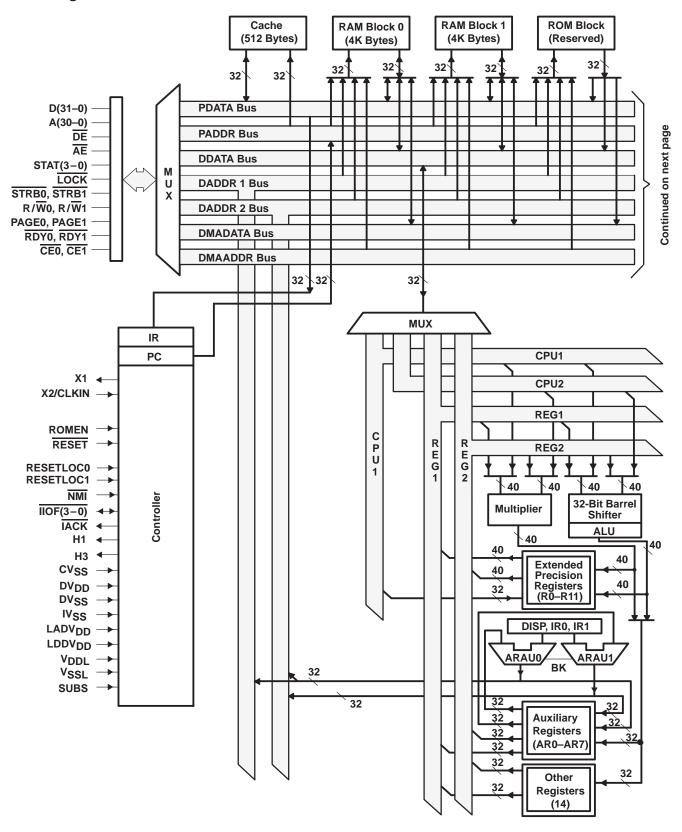

- Separate Internal Program, Data, and DMA Coprocessor Buses for Support of Massive Concurrent Input/Output (I/O) of Program and Data Throughput, Maximizing Sustained Central Processing Unit (CPU) Performance

- On-Chip Program Cache and Dual-Access/Single-Cycle RAM for Increased Memory-Access Performance

- 512-Byte Instruction Cache

- 8K Bytes of Single-Cycle Dual-Access Program or Data RAM

- ROM-Based Boot Loader Supports Program Bootup Using 8-, 16-, or 32-Bit Memories or One of the Communication Ports

- IDLE2 Clock-Stop Power-Down Mode

- 5-V Operation

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>†</sup> IEEE Standard 1149.1–1990 Standard Test-Access Port and Boundary-Scan Architecture EPIC and TI are trademarks of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1996, Texas Instruments Incorporated

SPRS038 – JANUARY 1996

#### block diagram

SPRS038 - JANUARY 1996

#### block diagram (continued)

SPRS038 – JANUARY 1996

#### functions

This section lists signal descriptions for the '320C40 device. The '320C40 pin functions table lists each signal, number of pins, operating mode(s) (that is, input, output, or high-impedance state as indicated by I, O, or Z, respectively), and function. The signals are grouped according to function.

**Pin Functions**

| NAME                | NO. OF<br>PINS                          | TYPE <sup>†</sup> | DESCRIPTION                                                                                        |  |  |  |  |  |

|---------------------|-----------------------------------------|-------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                     | GLOBAL-BUS EXTERNAL INTERFACE (80 PINS) |                   |                                                                                                    |  |  |  |  |  |

| D31-D0              | 32                                      | I/O/Z             | 32-bit data port of the global-bus external interface                                              |  |  |  |  |  |

| DE                  | 1                                       | I                 | Data-bus-enable signal for the global-bus external interface                                       |  |  |  |  |  |

| A30-A0              | 31                                      | O/Z               | 31-bit address port of the global-bus external interface                                           |  |  |  |  |  |

| AE                  | 1                                       | I                 | Address-bus-enable signal for the global-bus external interface                                    |  |  |  |  |  |

| STAT3-STAT0         | 4                                       | 0                 | Status signals for the global-bus external interface                                               |  |  |  |  |  |

| LOCK                | 1                                       | 0                 | Lock signal for the global-bus external interface                                                  |  |  |  |  |  |

| STRB0 <sup>‡</sup>  | 1                                       | O/Z               | Access strobe 0 for the global-bus external interface                                              |  |  |  |  |  |

| R/W0 <sup>‡</sup>   | 1                                       | O/Z               | Read/write signal for STRB0 accesses                                                               |  |  |  |  |  |

| PAGE0 <sup>‡</sup>  | 1                                       | O/Z               | Page signal for STRB0 accesses                                                                     |  |  |  |  |  |

| RDY0 <sup>‡</sup>   | 1                                       | I                 | Ready signal for STRB0 accesses                                                                    |  |  |  |  |  |

| CE0 <sup>‡</sup>    | 1                                       | I                 | Control enable for the STRB0, PAGE0, and R/W0 signals                                              |  |  |  |  |  |

| STRB1 <sup>‡</sup>  | 1                                       | O/Z               | Access strobe 1 for the global-bus external interface                                              |  |  |  |  |  |

| R/W1‡               | 1                                       | O/Z               | Read/write signal for STRB1 accesses                                                               |  |  |  |  |  |

| PAGE1 <sup>‡</sup>  | 1                                       | O/Z               | Page signal for STRB1 accesses                                                                     |  |  |  |  |  |

| RDY1 <sup>‡</sup>   | 1                                       | I                 | Ready signal for STRB1 accesses                                                                    |  |  |  |  |  |

| CE1 <sup>‡</sup>    | 1                                       | I                 | Control enable for the STRB1, PAGE1, and R/W1 signals                                              |  |  |  |  |  |

|                     |                                         |                   | LOCAL-BUS EXTERNAL INTERFACE (80 PINS)                                                             |  |  |  |  |  |

| LD31-LD0            | 32                                      | I/O/Z             | 32-bit data port of the local-bus external interface                                               |  |  |  |  |  |

| LDE                 | 1                                       | I                 | Data-bus-enable signal for the local-bus external interface                                        |  |  |  |  |  |

| LA30-LA0            | 31                                      | O/Z               | 31-bit address port of the local-bus external interface                                            |  |  |  |  |  |

| LAE                 | 1                                       | I                 | Address-bus-enable signal for the local-bus external interface                                     |  |  |  |  |  |

| LSTAT3-LSTAT0       | 4                                       | 0                 | Status signals for the local-bus external interface                                                |  |  |  |  |  |

| LLOCK               | 1                                       | 0                 | Lock signal for the local-bus external interface                                                   |  |  |  |  |  |

| LSTRB0 <sup>‡</sup> | 1                                       | O/Z               | Access strobe 0 for the local-bus external interface                                               |  |  |  |  |  |

| LR/W0               | 1                                       | O/Z               | Read/write signal for LSTRB0 accesses                                                              |  |  |  |  |  |

| LPAGE0              | 1                                       | O/Z               | Page signal for LSTRB0 accesses                                                                    |  |  |  |  |  |

| LRDY0               | 1                                       | I                 | Ready signal for LSTRB0 accesses                                                                   |  |  |  |  |  |

| LCE0                | 1                                       | I                 | Control enable for the $\overline{\text{LSTRB0}}$ , LPAGE0, and LR/ $\overline{\text{W0}}$ signals |  |  |  |  |  |

| LSTRB1 <sup>‡</sup> | 1                                       | O/Z               | Access strobe 1 for the local-bus external interface                                               |  |  |  |  |  |

| LR/W1               | 1                                       | O/Z               | Read/write signal for LSTRB1 accesses                                                              |  |  |  |  |  |

| LPAGE1              | 1                                       | O/Z               | Page signal for LSTRB1 accesses                                                                    |  |  |  |  |  |

| LRDY1               | 1                                       | I                 | Ready signal for LSTRB1 accesses                                                                   |  |  |  |  |  |

| LCE1                | 1                                       | I                 | Control enable for the LSTRB1, LPAGE1, and LR/W1 signals                                           |  |  |  |  |  |

† I = input, O = output, Z = high impedance

<sup>‡</sup> Signal's effective address range is defined by the local/global STRB ACTIVE bits.

SPRS038 – JANUARY 1996

| NAME                                          | NO. OF<br>PINS | TYPE <sup>†</sup> | DESCRIPTION                                           |  |  |  |

|-----------------------------------------------|----------------|-------------------|-------------------------------------------------------|--|--|--|

|                                               |                | (                 | I<br>COMMUNICATION PORT 0 INTERFACE (12 PINS)         |  |  |  |

| C0D7-C0D0 8 I/O Communication port 0 data bus |                |                   |                                                       |  |  |  |

| CREQ0                                         |                |                   |                                                       |  |  |  |

| CACKO                                         | 1              | 1/0               | Communication port 0 token-request-acknowledge signal |  |  |  |

| CSTRB0                                        | 1              | 1/0               | Communication port 0 data-strobe signal               |  |  |  |

| CRDY0                                         | 1              | 1/0               | Communication port 0 data-ready signal                |  |  |  |

|                                               |                |                   | COMMUNICATION PORT 1 INTERFACE (12 PINS)              |  |  |  |

| C1D7-C1D0                                     | 8              | I/O               | Communication port 1 data bus                         |  |  |  |

| CREQ1                                         | 1              | 1/0               | Communication port 1 token-request signal             |  |  |  |

| CACK1                                         | 1              | 1/0               | Communication port 1 token-request-acknowledge signal |  |  |  |

| CSTRB1                                        | 1              | 1/0               | Communication port 1 data-strobe signal               |  |  |  |

| CRDY1                                         | 1              | 1/0               | Communication port 1 data-ready signal                |  |  |  |

|                                               |                |                   | COMMUNICATION PORT 2 INTERFACE (12 PINS)              |  |  |  |

| C2D7-C2D0                                     | 8              | I/O               | Communication port 2 data bus                         |  |  |  |

| CREQ2                                         | 1              | 1/0               | Communication port 2 token-request signal             |  |  |  |

| CACK2                                         | 1              | 1/0               | Communication port 2 token-request-acknowledge signal |  |  |  |

| CSTRB2                                        | 1              | 1/0               | Communication port 2 data-strobe signal               |  |  |  |

| CRDY2                                         | 1              | I/O               | Communication port 2 data-ready signal                |  |  |  |

|                                               |                | (                 | COMMUNICATION PORT 3 INTERFACE (12 PINS)              |  |  |  |

| C3D7-C3D0                                     | 8              | I/O               | Communication port 3 data bus                         |  |  |  |

| CREQ3                                         | 1              | I/O               | Communication port 3 token-request signal             |  |  |  |

| CACK3                                         | 1              | I/O               | Communication port 3 token-request-acknowledge signal |  |  |  |

| CSTRB3                                        | 1              | I/O               | Communication port 3 data-strobe signal               |  |  |  |

| CRDY3                                         | 1              | I/O               | Communication port 3 data-ready signal                |  |  |  |

|                                               |                | (                 | COMMUNICATION PORT 4 INTERFACE (12 PINS)              |  |  |  |

| C4D7-C4D0                                     | 8              | I/O               | Communication port 4 data bus                         |  |  |  |

| CREQ4                                         | 1              | I/O               | Communication port 4 token-request signal             |  |  |  |

| CACK4                                         | 1              | I/O               | Communication port 4 token-request-acknowledge signal |  |  |  |

| CSTRB4                                        | 1              | I/O               | Communication port 4 data-strobe signal               |  |  |  |

| CRDY4                                         | 1              | I/O               | Communication port 4 data-ready signal                |  |  |  |

|                                               |                | (                 | COMMUNICATION PORT 5 INTERFACE (12 PINS)              |  |  |  |

| C5D7-C5D0                                     | 8              | I/O               | Communication port 5 data bus                         |  |  |  |

| CREQ5                                         | 1              | I/O               | Communication port 5 token-request signal             |  |  |  |

| CACK5                                         | 1              | I/O               | Communication port 5 token-request-acknowledge signal |  |  |  |

| CSTRB5                                        | 1              | I/O               | Communication port 5 data-strobe signal               |  |  |  |

| CRDY5                                         | 1              | I/O               | Communication port 5 data-ready signal                |  |  |  |

$\dagger I = input, O = output, Z = high impedance$

SPRS038 – JANUARY 1996

#### **Pin Functions (Continued)**

| NAME                    | NO. OF<br>PINS | TYPE <sup>†</sup> | DESCRIPTION                                                  |

|-------------------------|----------------|-------------------|--------------------------------------------------------------|

|                         |                | IN                | ITERRUPTS, I/O FLAGS, RESET, TIMER (12 PINS)                 |

| IIOF3-IIOF0             | 4              | I/O               | Interrupt and I/O flags                                      |

| NMI                     | 1              | I                 | Nonmaskable interrupt. NMI is sensitive to a low-going edge. |

| IACK                    | 1              | 0                 | Interrupt acknowledge                                        |

| RESET                   | 1              | Ι                 | Reset signal                                                 |

| RESETLOC1-<br>RESETLOC0 | 2              | Ι                 | Reset-vector location pins                                   |

| ROMEN                   | 1              | I                 | On-chip ROM enable (0 = disable, 1 = enable)                 |

| TCLK0                   | 1              | I/O               | Timer 0 pin                                                  |

| TCLK1                   | 1              | I/O               | Timer 1 pin                                                  |

|                         |                |                   | CLOCK (4 PINS)                                               |

| X1                      | 1              | 0                 | Crystal pin                                                  |

| X2/CLKIN                | 1              | I                 | Crystal/oscillator pin                                       |

| H1                      | 1              | 0                 | H1 clock                                                     |

| H3                      | 1              | 0                 | H3 clock                                                     |

|                         |                |                   | POWER (70 PINS)                                              |

| CV <sub>SS</sub>        | 15             | I                 | Ground pins                                                  |

| DVSS                    | 15             | I                 | Ground pins                                                  |

| IV <sub>SS</sub>        | 6              | I                 | Ground pins                                                  |

| DVDD                    | 13             | I                 | 5-V <sub>DC</sub> supply pins                                |

| GADV <sub>DD</sub>      | 3              | I                 | 5-V <sub>DC</sub> supply pins                                |

| GDDV <sub>DD</sub>      | 3              | I                 | 5-V <sub>DC</sub> supply pins                                |

| LADV <sub>DD</sub>      | 3              | I                 | 5-V <sub>DC</sub> supply pins                                |

| LDDV <sub>DD</sub>      | 3              | I                 | 5-V <sub>DC</sub> supply pins                                |

| SUBS                    | 1              | I                 | Substrate pin (tie to ground)                                |

| V <sub>DDL</sub>        | 4              | I                 | 5-V <sub>DC</sub> supply pins                                |

| VSSL                    | 4              | I                 | Ground pins                                                  |

|                         |                |                   | EMULATION (7 PINS)                                           |

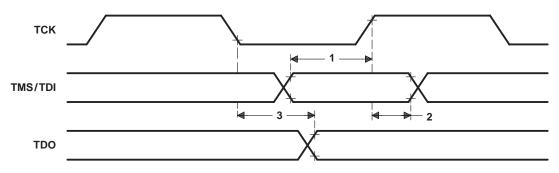

| TCK                     | 1              | I                 | IEEE 1149.1 test port clock                                  |

| TDO                     | 1              | O/Z               | IEEE 1149.1 test port data out                               |

| TDI                     | 1              | Ι                 | IEEE 1149.1 test port data in                                |

| TMS                     | 1              | Ι                 | IEEE 1149.1 test port mode select                            |

| TRST                    | 1              | Ι                 | IEEE 1149.1 test port reset                                  |

| EMU0                    | 1              | I/O               | Emulation pin 0                                              |

| EMU1                    | 1              | I/O               | Emulation pin 1                                              |

$\dagger I = input$ , O = output, Z = high impedance

SPRS038 – JANUARY 1996

| PIN  |      | P    | N    | PI               | N    | P                | N    | PIN                |      |

|------|------|------|------|------------------|------|------------------|------|--------------------|------|

| NAME | NO.  | NAME | NO.  | NAME             | NO.  | NAME             | NO.  | NAME               | NO.  |

| A0   | D32  | C0D6 | AN7  | C5D4             | AM30 | CVSS             | E35  | D31                | F32  |

| A1   | B32  | C0D7 | AK8  | C5D5             | AP32 | CVSS             | AR25 | DE                 | AA31 |

| A2   | D30  | C1D0 | AL7  | C5D6             | AM32 | CVSS             | AE1  | DVDD               | AR11 |

| A3   | C29  | C1D1 | AP8  | C5D7             | AL31 | CV <sub>SS</sub> | AR13 | DV <sub>DD</sub>   | AR29 |

| A4   | B30  | C1D2 | AM8  | CACK0            | AN11 | CVSS             | A19  | DVDD               | A13  |

| A5   | F28  | C1D3 | AK12 | CACK1            | AN13 | CVSS             | R35  | DVDD               | A7   |

| A6   | F24  | C1D4 | AK10 | CACK2            | AM14 | CVSS             | AL1  | DVDD               | A17  |

| A7   | E29  | C1D5 | AN9  | CACK3            | AM16 | D0               | U33  | DVDD               | L35  |

| A8   | C27  | C1D6 | AL9  | CACK4            | AK32 | D1               | V32  | DVDD               | AR23 |

| A9   | D28  | C1D7 | AP10 | CACK5            | AJ31 | D2               | T34  | DVDD               | A29  |

| A10  | B28  | C2D0 | AM18 | CE0              | AA33 | D3               | U31  | DV <sub>DD</sub>   | L1   |

| A11  | F26  | C2D1 | AN19 | CE1              | V34  | D4               | R33  | DVDD               | AC1  |

| A12  | C25  | C2D2 | AL19 | CRDY0            | AP12 | D5               | P34  | DVDD               | AR17 |

| A13  | E27  | C2D3 | AP20 | CRDY1            | AP14 | D6               | T32  | DVDD               | A23  |

| A14  | B26  | C2D4 | AM20 | CRDY2            | AL15 | D7               | N33  | DVDD               | AJ1  |

| A15  | D26  | C2D5 | AN21 | CRDY3            | AL17 | D8               | R31  | DVSS               | AJ35 |

| A16  | C23  | C2D6 | AL21 | CRDY4            | AH30 | D9               | M34  | DVSS               | A21  |

| A17  | B24  | C2D7 | AP22 | CRDY5            | AH32 | D10              | P32  | DVSS               | A25  |

| A18  | E25  | C3D0 | AM22 | CREQ0            | AM10 | D11              | L33  | DVSS               | G35  |

| A19  | C21  | C3D1 | AN23 | CREQ1            | AM12 | D12              | N31  | DVSS               | A11  |

| A20  | D24  | C3D2 | AL23 | CREQ2            | AN15 | D13              | K34  | DVSS               | AG1  |

| A21  | B22  | C3D3 | AP24 | CREQ3            | AN17 | D14              | M32  | DVSS               | AM2  |

| A22  | E23  | C3D4 | AM24 | CREQ4            | AN33 | D15              | J33  | DVSS               | R1   |

| A23  | C19  | C3D5 | AN25 | CREQ5            | AL33 | D16              | L31  | DVSS               | AR21 |

| A24  | D22  | C3D6 | AL25 | CSTRB0           | AL11 | D17              | M30  | DVSS               | AR15 |

| A25  | B20  | C3D7 | AP26 | CSTRB1           | AL13 | D18              | K32  | DVSS               | A15  |

| A26  | E21  | C4D0 | AN27 | CSTRB2           | AP16 | D19              | H34  | DVSS               | AR27 |

| A27  | B18  | C4D1 | AM26 | CSTRB3           | AP18 | D20              | J31  | DVSS               | G1   |

| A28  | C17  | C4D2 | AK24 | CSTRB4           | AM34 | D21              | G33  | DVSS               | N35  |

| A29  | D20  | C4D3 | AL27 | CSTRB5           | AK34 | D22              | K30  | DVSS               | AR9  |

| A30  | B16  | C4D4 | AP28 | CVSS             | AR19 | D23              | F34  | EMU0               | AA35 |

| AE   | AG31 | C4D5 | AK26 | CVSS             | AR7  | D24              | H32  | EMU1               | AD34 |

| C0D0 | AP4  | C4D6 | AN29 | CVSS             | N1   | D25              | E33  | GADV <sub>DD</sub> | B2   |

| C0D1 | AL5  | C4D7 | AM28 | CVSS             | AL35 | D26              | D34  | GADV <sub>DD</sub> | AR1  |

| C0D2 | AN5  | C5D0 | AL29 | CVSS             | A27  | D27              | G31  | GADV <sub>DD</sub> | U35  |

| C0D3 | AM4  | C5D1 | AP30 | CVSS             | A9   | D28              | C33  | GDDV <sub>DD</sub> | V2   |

| C0D4 | AP6  | C5D2 | AK28 | CV <sub>SS</sub> | E1   | D29              | H30  | GDDV <sub>DD</sub> | A35  |

| C0D5 | AM6  | C5D3 | AN31 | CVSS             | J35  | D30              | E31  | GDDV <sub>DD</sub> | A1   |

#### GF Package Pin Assignments — Alphabetical Listing

SPRS038 – JANUARY 1996

#### GF Package Pin Assignments — Alphabetical Listing (Continued)

| PI               | N    | PI                 | N    | PIN                | 1    | PIN              |      |  |

|------------------|------|--------------------|------|--------------------|------|------------------|------|--|

| NAME             | NO.  | NAME               | NO.  | NAME               | NO.  | NAME             | NO.  |  |

| H1               | AC3  | LA25               | R5   | LD26               | B4   | STAT0            | AD32 |  |

| H3               | AC5  | LA26               | T2   | LD27               | F8   | STAT1            | AE33 |  |

| IACK             | W3   | LA27               | U3   | LD28               | D6   | STAT2            | AF34 |  |

| IIOF0            | AN3  | LA28               | T4   | LD29               | C3   | STAT3            | AE31 |  |

| IIOF1            | AL3  | LA29               | V4   | LD30               | E5   | STRB0            | AD30 |  |

| IIOF2            | AH6  | LA30               | U5   | LD31               | F6   | STRB1            | AC33 |  |

| IIOF3            | AK2  | LADVDD             | B34  | LDDV <sub>DD</sub> | AR35 | SUBS             | C31  |  |

| IVSS             | AR5  | LADVDD             | AB2  | LDDV <sub>DD</sub> | AP2  | тск              | Y34  |  |

| IVSS             | AR31 | LADV <sub>DD</sub> | AP34 | LDDV <sub>DD</sub> | U1   | TCLK0            | AE3  |  |

| IVSS             | AG35 | LAE                | AB4  | LDE                | AD4  | TCLK1            | AD2  |  |

| IV <sub>SS</sub> | A31  | LCE0               | AG5  | LLOCK              | AA5  | TDO              | AB34 |  |

| IVSS             | J1   | LCE1               | AF2  | LOCK               | W33  | TDI              | AC35 |  |

| IVSS             | A5   | LD0                | E19  | LPAGE0             | AH2  | TMS              | W35  |  |

| LAO              | D2   | LD1                | C15  | LPAGE1             | AG3  | TRST             | AE35 |  |

| LA1              | D4   | LD2                | D18  | LRDY0              | AF6  | VDDL             | AN1  |  |

| LA2              | E3   | LD3                | B14  | LRDY1              | AE5  | VDDL             | AN35 |  |

| LA3              | F4   | LD4                | E17  | LR/W0              | AH4  | V <sub>DDL</sub> | C35  |  |

| LA4              | H6   | LD5                | D16  | LR/W1              | AF4  | V <sub>DDL</sub> | C1   |  |

| LA5              | F2   | LD6                | C13  | LSTAT0             | AA3  | VSSL             | A3   |  |

| LA6              | G5   | LD7                | E15  | LSTAT1             | Y4   | VSSL             | AR3  |  |

| LA7              | G3   | LD8                | B12  | LSTAT2             | Y2   | VSSL             | AR33 |  |

| LA8              | H4   | LD9                | D14  | LSTAT3             | W5   | VSSL             | A33  |  |

| LA9              | H2   | LD10               | C11  | LSTRB0             | AJ3  | X1               | W1   |  |

| LA10             | K6   | LD11               | E13  | LSTRB1             | AD6  | X2/CLKIN         | AA1  |  |

| LA11             | M6   | LD12               | B10  | NMI                | AJ5  | 1                |      |  |

| LA12             | J5   | LD13               | D12  | PAGE0              | AG33 | 1                |      |  |

| LA13             | J3   | LD14               | C9   | PAGE1              | AB32 | 1                |      |  |

| LA14             | K4   | LD15               | E11  | RDY0               | Y32  | 1                |      |  |

| LA15             | K2   | LD16               | F12  | RDY1               | W31  | 1                |      |  |

| LA16             | L3   | LD17               | D10  | RESETLOC0          | AF30 | 1                |      |  |

| LA17             | L5   | LD18               | B8   | RESETLOC1          | AH34 | 1                |      |  |

| LA18             | M2   | LD19               | E9   | RESET              | AJ33 | 1                |      |  |

| LA19             | M4   | LD20               | C7   | ROMEN              | AK4  | 1                |      |  |

| LA20             | N3   | LD21               | F10  | R/W0               | AF32 | 1                |      |  |

| LA21             | N5   | LD22               | B6   | R/W1               | AC31 | 1                |      |  |

| LA22             | P2   | LD23               | D8   |                    |      | 1                |      |  |

| LA23             | P4   | LD24               | C5   |                    |      |                  |      |  |

| LA24             | R3   | LD25               | E7   | 1                  |      |                  |      |  |

SPRS038 – JANUARY 1996

|      | PIN                |      | PIN              | F    | PIN              | F    | PIN              |

|------|--------------------|------|------------------|------|------------------|------|------------------|

| NO.  | NAME               | NO.  | NAME             | NO.  | NAME             | NO.  | NAME             |

| A1   | GDDV <sub>DD</sub> | AD30 | STRB0            | AK24 | C4D2             | AM30 | C5D4             |

| A3   | VSSL               | AD32 | STAT0            | AK26 | C4D5             | AM32 | C5D6             |

| A5   | IVSS               | AD34 | EMU1             | AK28 | C5D2             | AM34 | CSTRB4           |

| A7   | DV <sub>DD</sub>   | AE1  | CV <sub>SS</sub> | AK32 | CACK4            | AN1  | V <sub>DDL</sub> |

| A9   | CVSS               | AE3  | TCLK0            | AK34 | CSTRB5           | AN3  | IIOF0            |

| A11  | DVSS               | AE5  | LRDY1            | AL1  | CV <sub>SS</sub> | AN5  | C0D2             |

| A13  | DV <sub>DD</sub>   | AE31 | STAT3            | AL3  | IIOF1            | AN7  | C0D6             |

| A15  | DVSS               | AE33 | STAT1            | AL5  | C0D1             | AN9  | C1D5             |

| A17  | DV <sub>DD</sub>   | AE35 | TRST             | AL7  | C1D0             | AN11 | CACK0            |

| A19  | CVSS               | AF2  | LCE1             | AL9  | C1D6             | AN13 | CACK1            |

| A21  | DVSS               | AF4  | LR/W1            | AL11 | CSTRB0           | AN15 | CREQ2            |

| A23  | DV <sub>DD</sub>   | AF6  | LRDY0            | AL13 | CSTRB1           | AN17 | CREQ3            |

| A25  | DVSS               | AF30 | RESETLOC0        | AL15 | CRDY2            | AN19 | C2D1             |

| A27  | CVSS               | AF32 | R/W0             | AL17 | CRDY3            | AN21 | C2D5             |

| A29  | DV <sub>DD</sub>   | AF34 | STAT2            | AL19 | C2D2             | AN23 | C3D1             |

| A31  | IV <sub>SS</sub>   | AG1  | DVSS             | AL21 | C2D6             | AN25 | C3D5             |

| A33  | V <sub>SSL</sub>   | AG3  | LPAGE1           | AL23 | C3D2             | AN27 | C4D0             |

| A35  | GDDV <sub>DD</sub> | AG5  | LCE0             | AL25 | C3D6             | AN29 | C4D6             |

| AA1  | X2/CLKIN           | AG31 | AE               | AL27 | C4D3             | AN31 | C5D3             |

| AA3  | LSTAT0             | AG33 | PAGE0            | AL29 | C5D0             | AN33 | CREQ4            |

| AA5  | LLOCK              | AG35 | IV <sub>SS</sub> | AL31 | C5D7             | AN35 | VDDL             |

| AA31 | DE                 | AH2  | LPAGE0           | AL33 | CREQ5            | AP2  | LDDVDD           |

| AA33 | CE0                | AH4  | LR/W0            | AL35 | CV <sub>SS</sub> | AP4  | C0D0             |

| AA35 | EMU0               | AH6  | IIOF2            | AM2  | DV <sub>SS</sub> | AP6  | C0D4             |

| AB2  | LADV <sub>DD</sub> | AH30 | CRDY4            | AM4  | C0D3             | AP8  | C1D1             |

| AB4  | LAE                | AH32 | CRDY5            | AM6  | C0D5             | AP10 | C1D7             |

| AB32 | PAGE1              | AH34 | RESETLOC1        | AM8  | C1D2             | AP12 | CRDY0            |

| AB34 | TDO                | AJ1  | DVDD             | AM10 | CREQ0            | AP14 | CRDY1            |

| AC1  | DVDD               | AJ3  | LSTRB0           | AM12 | CREQ1            | AP16 | CSTRB2           |

| AC3  | H1                 | AJ5  | NMI              | AM14 | CACK2            | AP18 | CSTRB3           |

| AC5  | H3                 | AJ31 | CACK5            | AM16 | CACK3            | AP20 | C2D3             |

| AC31 | R/W1               | AJ33 | RESET            | AM18 | C2D0             | AP22 | C2D7             |

| AC33 | STRB1              | AJ35 | DVSS             | AM20 | C2D4             | AP24 | C3D3             |

| AC35 | TDI                | AK2  | IIOF3            | AM22 | C3D0             | AP26 | C3D7             |

| AD2  | TCLK1              | AK4  | ROMEN            | AM24 | C3D4             | AP28 | C4D4             |

| AD4  | LDE                | AK8  | C0D7             | AM26 | C4D1             | AP30 | C5D1             |

| AD6  | LSTRB1             | AK10 | C1D4             | AM28 | C4D7             | AP32 | C5D5             |

|      |                    | AK12 | C1D3             |      |                  | AP34 | LADVDD           |

#### GF Package Pin Assignments — Numerical Listing

SPRS038 – JANUARY 1996

#### GF Package Pin Assignments — Numerical Listing (Continued)

|      | PIN                | F   | PIN  | F   | PIN  | P   | IN               |     | PIN                |

|------|--------------------|-----|------|-----|------|-----|------------------|-----|--------------------|

| NO.  | NAME               | NO. | NAME | NO. | NAME | NO. | NAME             | NO. | NAME               |

| AR1  | GADV <sub>DD</sub> | C1  | VDDL | E1  | CVSS | H2  | LA9              | P2  | LA22               |

| AR3  | VSSL               | C3  | LD29 | E3  | LA2  | H4  | LA8              | P4  | LA23               |

| AR5  | IV <sub>SS</sub>   | C5  | LD24 | E5  | LD30 | H6  | LA4              | P32 | D10                |

| AR7  | CV <sub>SS</sub>   | C7  | LD20 | E7  | LD25 | H30 | D29              | P34 | D5                 |

| AR9  | DVSS               | C9  | LD14 | E9  | LD19 | H32 | D24              | R1  | DVSS               |

| AR11 | DVDD               | C11 | LD10 | E11 | LD15 | H34 | D19              | R3  | LA24               |

| AR13 | CVSS               | C13 | LD6  | E13 | LD11 | J1  | IV <sub>SS</sub> | R5  | LA25               |

| AR15 | DVSS               | C15 | LD1  | E15 | LD7  | J3  | LA13             | R31 | D8                 |

| AR17 | DVDD               | C17 | A28  | E17 | LD4  | J5  | LA12             | R33 | D4                 |

| AR19 | CVSS               | C19 | A23  | E19 | LD0  | J31 | D20              | R35 | CVSS               |

| AR21 | DVSS               | C21 | A19  | E21 | A26  | J33 | D15              | T2  | LA26               |

| AR23 | DVDD               | C23 | A16  | E23 | A22  | J35 | CVSS             | T4  | LA28               |

| AR25 | CVSS               | C25 | A12  | E25 | A18  | K2  | LA15             | T32 | D6                 |

| AR27 | DVSS               | C27 | A8   | E27 | A13  | K4  | LA14             | T34 | D2                 |

| AR29 | DVDD               | C29 | A3   | E29 | A7   | K6  | LA10             | U1  | LDDVDD             |

| AR31 | IVSS               | C31 | SUBS | E31 | D30  | K30 | D22              | U3  | LA27               |

| AR33 | V <sub>SSL</sub>   | C33 | D28  | E33 | D25  | K32 | D18              | U5  | LA30               |

| AR35 | LDDV <sub>DD</sub> | C35 | VDDL | E35 | CVSS | K34 | D13              | U31 | D3                 |

| B2   | GADV <sub>DD</sub> | D2  | LA0  | F2  | LA5  | L1  | DVDD             | U33 | D0                 |

| B4   | LD26               | D4  | LA1  | F4  | LA3  | L3  | LA16             | U35 | GADV <sub>DD</sub> |

| B6   | LD22               | D6  | LD28 | F6  | LD31 | L5  | LA17             | V2  | GDDV <sub>DD</sub> |

| B8   | LD18               | D8  | LD23 | F8  | LD27 | L31 | D16              | V4  | LA29               |

| B10  | LD12               | D10 | LD17 | F10 | LD21 | L33 | D11              | V32 | D1                 |

| B12  | LD8                | D12 | LD13 | F12 | LD16 | L35 | DVDD             | V34 | CE1                |

| B14  | LD3                | D14 | LD9  | F24 | A6   | M2  | LA18             | W1  | X1                 |

| B16  | A30                | D16 | LD5  | F26 | A11  | M4  | LA19             | W3  | IACK               |

| B18  | A27                | D18 | LD2  | F28 | A5   | M6  | LA11             | W5  | LSTAT3             |

| B20  | A25                | D20 | A29  | F32 | D31  | M30 | D17              | W31 | RDY1               |

| B22  | A21                | D22 | A24  | F34 | D23  | M32 | D14              | W33 | LOCK               |

| B24  | A17                | D24 | A20  | G1  | DVSS | M34 | D9               | W35 | TMS                |

| B26  | A14                | D26 | A15  | G3  | LA7  | N1  | CVSS             | Y2  | LSTAT2             |

| B28  | A10                | D28 | A9   | G5  | LA6  | N3  | LA20             | Y4  | LSTAT1             |

| B30  | A4                 | D30 | A2   | G31 | D27  | N5  | LA21             | Y32 | RDY0               |

| B32  | A1                 | D32 | A0   | G33 | D21  | N31 | D12              | Y34 | TCK                |

| B34  | LADV <sub>DD</sub> | D34 | D26  | G35 | DVSS | N33 | D7               |     |                    |

|      |                    |     |      |     |      | N35 | DVSS             |     |                    |

SPRS038 - JANUARY 1996

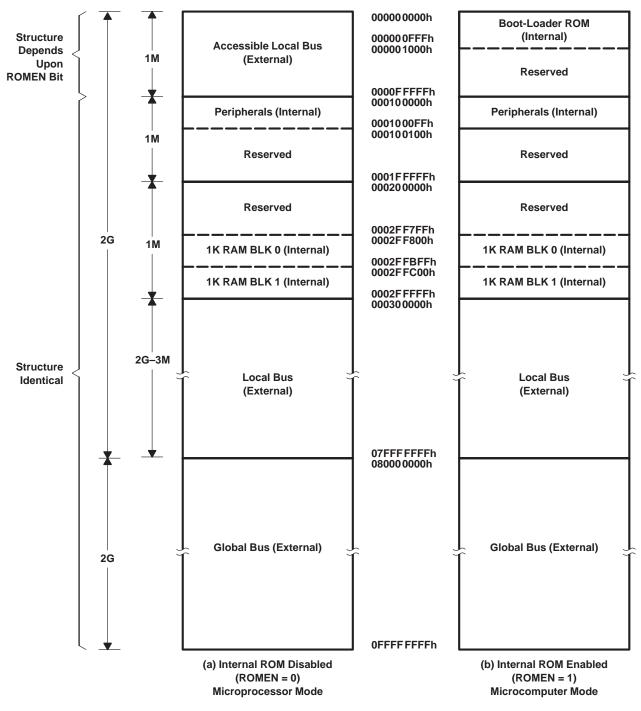

#### memory map

Figure 1 shows the memory map for the '320C40. Refer to the *TMS320C4x User's Guide* (literature number SPRU063B) for a detailed description of this memory mapping.

Figure 1. Memory Map for '320C40

#### SPRS038 – JANUARY 1996

#### description

The '320C40 digital signal processors (DSPs) are 32-bit, floating-point processors manufactured in 0.72-μm, double-level metal CMOS technology. The '320C40 is a part of the fourth generation of DSPs from Texas Instruments and is designed primarily for parallel processing.

#### operation

The '320C40 has six on-chip communication ports for processor-to-processor communication with no external hardware and simple communication software. This allows connectivity to other 'C4x processors with no external-glue logic. The communication ports remove input/output bottlenecks, and the independent smart DMA coprocessor is able to handle the CPU input/output burden.

#### central processing unit

The '320C40 CPU is configured for high-speed internal parallelism for the highest sustained performance. The key features of the CPU are:

- Eight operations/cycle:

- 40/32-bit floating-point/integer multiply

- 40/32-bit floating-point/integer ALU operation

- Two data accesses

- Two address register updates

- IEEE floating-point conversion

- Divide and square-root support

- 'C3x assembly language compatibility

- Byte and halfword accessibility

#### **DMA coprocessor**

The DMA coprocessor allows concurrent I/O and CPU processing for the highest sustained CPU performance. The key features of the DMA processor are:

- Link pointers allow DMA channels to auto-initialize without CPU intervention.

- Parallel CPU operation and DMA transfers

- Six DMA channels support memory-to-memory data transfers.

- Split-mode operation doubles the available DMA channel to 12 when data transfers to and from a communication port are required.

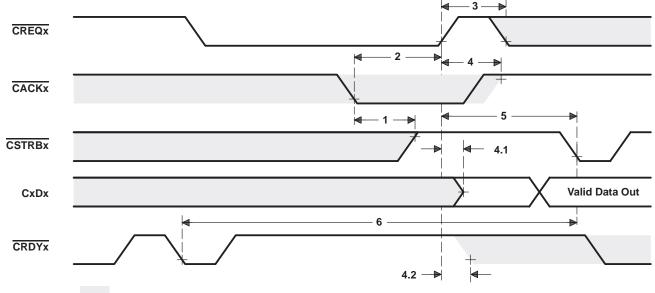

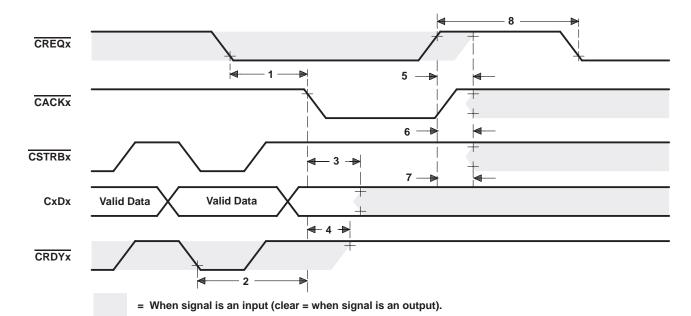

#### communication ports

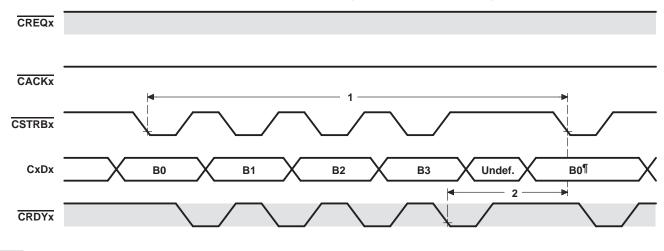

The '320C40 is the first DSP with on-chip communication ports for processor-to-processor communication with no external hardware and simple communication software. The features of the communication ports are:

- Direct interprocessor communication and processor I/O

- Six communication ports for direct interprocessor communication and processor I/O

- 20M-bytes/s bidirectional interface on each communication port for high-speed multiprocessor interface

- Separate input and output 8-word-deep FIFO buffers for processor-to-processor communication and I/O

- Automatic arbitration and handshaking for direct processor-to-processor connection

#### communication-port software reset ('C40 silicon revision $\ge$ 5.0)

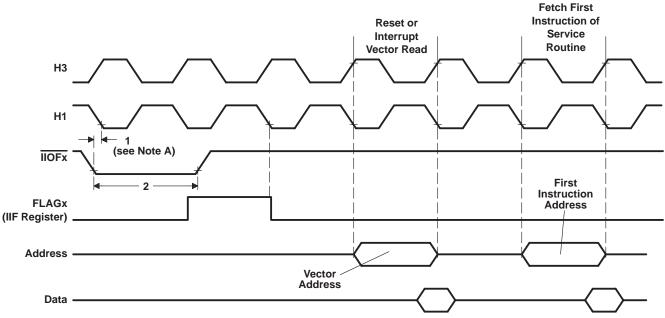

The input and output FIFO levels for a communication port can be flushed by writing at least two back-to-back values to its communication-port-software reset address as specified in Table 1. This feature is not present in 'C40 silicon revision <5.0. This software reset flushes any word or byte already present in the FIFOs but it does not affect the status of the communication-port pins. Figure 2 shows an example of communication-port-software reset.

| COMMUNICATION PORT | SOFTWARE RESET ADDRESS |

|--------------------|------------------------|

| 0                  | 0x0100043              |

| 1                  | 0x0100053              |

| 2                  | 0x0100063              |

| 3                  | 0x0100073              |

| 4                  | 0x0100083              |

| 5                  | 0x0100093              |

Table 1. Communication-Port Software-Reset Address

```

; _____;

; RESET1:Flush's FIFO data for communication port 1;

; -----;

RESET1 push AR0 ; Save registers

push R0

;

push RC

;

ldhi 010h,AR0 ; Set AR0 to base address of COM 1

or

050h,AR0

;

flush: rpts 1

; Flush FIFO data with back-to-back write

sti R0,*+AR0(3) ;

rpts 10

; Wait

nop

ldi

*+AR0(0),R0 ; Check for new data from other port

01FE0h,R0 ;

and

bnz

flush

;

pop

RC

; Restore registers

R0

pop

;

pop

ar0

;

; Return

rets

```

SPRS038 - JANUARY 1996

#### $\overline{\text{NMI}}$ with bus-grant feature ('C40 silicon revision $\geq$ 5.0)

The '320C40 devices have a software-configurable feature which allows forcing the internal-peripheral bus to ready when the  $\overline{\text{NMI}}$  signal is asserted. This feature is not present in 'C40 silicon revision < 5.0. The  $\overline{\text{NMI}}$  bus-grant feature is enabled when bits 19–18 of the status register (ST) are set to 10b. When enabled, a peripheral bus-grant signal is generated on the falling edge of  $\overline{\text{NMI}}$ . When  $\overline{\text{NMI}}$  is asserted and this feature is not enabled, the CPU stalls on access to the peripheral bus if it is not ready. A stall condition occurs when writing to a full FIFO or reading an empty FIFO. This feature is useful in correcting communication-port errors when used in conjunction with the communication-port software-reset feature.

#### IDLE2 clock-stop power-down mode ('C40 silicon revision $\ge$ 5.0)

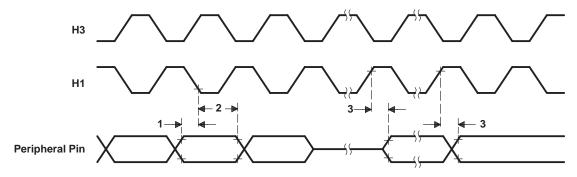

The '320C40 has a clock-stop mode or power-down mode (IDLE2) to achieve extremely low-power consumption. When an IDLE2 instruction is executed, the clocks are halted with H1 being held high. To exit IDLE2, assert one of the IIOF3–IIOF0 pins configured as an external interrupt instead of a general-purpose I/O. A macro showing how to generate the IDLE2 opcode is given in Figure 3. During this power-down mode:

- No instructions are executed.

- The CPU, peripherals, and internal memory retain their previous state.

- The external-bus outputs are idle. The address lines remain in their previous state, the data lines are in the high-impedance state, and the output-control signals are inactive.

```

; ------;

; IDLE2: Macro to generate idle2 opcode ;

; ------;

IDLE2 .macro

.word 06000001h

.endm

```

#### Figure 3. Example of Software Subroutine Using IDLE2

IDLE2 is exited when one of the five external interrupts ( $\overline{\text{NMI}}$  and  $\overline{\text{IIOF3}}$ – $\overline{\text{IIOF0}}$ ) is asserted low for at least four input clocks (two H1 cycles). The clocks then start after a delay of two input clocks (one H1 cycle). The clocks can start in the opposite phase; that is, H1 can be high when H3 was high before the clocks were stopped. However, the H1 and H3 clocks remain 180° out of phase with each other.

During IDLE2 operation, an external interrupt can be recognized and serviced by the CPU if it is enabled before entering IDLE2 and asserted for at least two H1 cycles. For the processor to recognize only one interrupt, the interrupt pin must be configured for edge-trigger mode or asserted less than three cycles in level-trigger mode. Any external interrupt pin can wake up the device from IDLE2, but for the CPU to recognize that interrupt, it must also be enabled. If an interrupt is recognized and executed by the CPU, the instruction following the IDLE2 instruction is not executed until after execution of a return opcode.

When the device is in emulation mode, the CPU executes an IDLE2 instruction as if it were an IDLE instruction. The clocks continue to run for correct operation of the emulator.

#### development tools

The 'C40 is supported by a host of parallel-processing development tools for developing and simulating code easily and for debugging parallel-processing systems. The code generation tools include:

- An ANSI C compiler optimized with a runtime support library that supports use of communication ports and DMA.

- Third party support for C, C++ and Ada compilers

- Several operating systems available for parallel-processing support, as well as DMA and communication port drivers

- An assembler and linker with support for mapping program and data to parallel processors

The simulation tools include:

- Parallel DSP system-level simulation with LAI hardware verification (HV) model and full function (FF) model.

- TI software simulator with high-level language debugger interface for simulating a single processor.

The hardware development and verification tools include:

- Parallel processor in-circuit emulator and high-level language debugger: XDS510.

- Parallel processor development system (PPDS) with four '320C40s, local and global memory, and communication port connections.

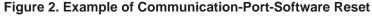

#### silicon revision identification

SPRS038 – JANUARY 1996

#### absolute maximum ratings over specified temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>DD</sub> (see Note 1) – 0.3 V to 7 V |

|-------------------------------------------------------------------|

| Voltage range on any pin – 0.3 V to 7 V                           |

| Output voltage range                                              |

| Operating case temperature range, T <sub>C</sub>                  |

| Storage temperature range, T <sub>stg</sub> – 55°C to 150°C       |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to V<sub>SS</sub>.

#### recommended operating conditions (see Note 2)

|                 |                                            |                |  | MIN  | TYP‡ | MAX                    | UNIT |  |

|-----------------|--------------------------------------------|----------------|--|------|------|------------------------|------|--|

| V <sub>DD</sub> | Supply voltages (DDV <sub>DD</sub> , etc.) |                |  | 4.75 | 5    | 5.25                   | V    |  |

|                 |                                            | X2/CLKIN       |  | 2.6  |      | V <sub>DD</sub> + 0.3§ | V    |  |

| VIH             | High-level input voltage                   | All other pins |  | 2    |      | V <sub>DD</sub> + 0.3§ | l v  |  |

| VIL             | Low-level input voltage                    |                |  |      |      | 0.8                    | V    |  |

| IOH             | High-level output current                  |                |  |      |      | - 300                  | μΑ   |  |

| IOL             | Low-level output current                   |                |  |      |      | 2                      | mA   |  |

| ТС              | Operating case temperature                 |                |  |      |      | 85                     | °C   |  |

<sup>‡</sup> All typical values are at  $V_{DD} = 5 V$ ,  $T_A$  (ambient air temperature)= 25°C.

§ This parameter is characterized but not tested.

NOTE 2: All input and output voltage levels are TTL compatible, except for CLKIN. CLKIN can be driven by CMOS clock.

## electrical characteristics over recommended ranges of supply voltage and operating case temperature (unless otherwise noted)

|                 | PARAMETER                    | TEST CONDITIONS                                                   |                          | MIN | TYP¶ | MAX             | UNIT |

|-----------------|------------------------------|-------------------------------------------------------------------|--------------------------|-----|------|-----------------|------|

| VOH             | High-level output voltage    | V <sub>DD</sub> = MIN, I <sub>OH</sub> = MAX                      |                          | 2.4 | 3    |                 | V    |

| VOL             | Low-level output voltage     | V <sub>DD</sub> = MIN, I <sub>OL</sub> = MAX                      |                          |     | 0.3  | 0.6             | V    |

| ΙZ              | Three-state current          | V <sub>DD</sub> = MAX                                             |                          | -20 |      | 20              | μA   |

| IIC             | Input current, X2/CLKIN only | $V_I = V_{SS}$ to $V_{DD}$                                        | - 30                     |     | 30   | μA              |      |

| I <sub>IP</sub> | Input current                | Inputs with internal pullups<br>(See Note 3)                      | -400                     |     | 20   | μA              |      |

| Ц               | Input current                | $V_{I} = V_{SS}$ to $V_{DD}$                                      | -                        | -10 |      | 10              | μΑ   |

| Icc             | Supply current               | $T_A = 25 \circ C$ , $V_{DD} = MAX$ , $f_X = MAX$<br>(See Note 4) | '320C40-40<br>'320C40-50 |     | 350  | 850             | mA   |

|                 |                              | · · · ·                                                           | '320C40-60               |     |      | 950             |      |

| Cl              | Input capacitance            |                                                                   |                          |     |      | 15 <sup>#</sup> | pF   |

| CO              | Output capacitance           |                                                                   |                          |     |      | 15 <sup>#</sup> | pF   |

¶ All typical values are at  $V_{DD}$  = 5 V, T<sub>A</sub> (ambient air temperature) = 25°C.

<sup>#</sup> This parameter is specified by design but not tested.

NOTES: 3. Pins with internal pullup devices: TDI, TCK, TMS. Pin with internal pulldown device: TRST.

4. f<sub>X</sub> is the input clock frequency. The maximum value (max) for the '320C40-40, '320C40-50, and '320C40-60 is 40, 50 and 60 MHz, respectively.

SPRS038 – JANUARY 1996

#### Figure 4. Test Load Circuit

#### signal transition levels

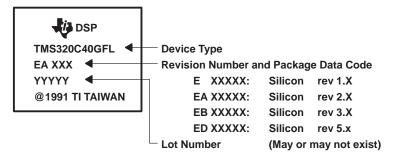

TTL-level outputs are driven to a minimum logic-high level of 2.4 V and to a maximum logic-low level of 0.6 V. Output transition times are specified as follows.

For a high-to-low transition on a TTL-compatible output signal, the level at which the output is said to be no longer high is 2 V and the level at which the output is said to be low is 1 V. For a low-to-high transition, the level at which the output is said to be no longer low is 1 V and the level at which the output is said to be high is 2 V. See Figure 5.

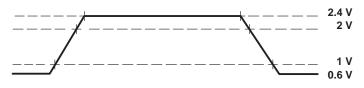

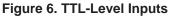

Figure 5. TTL-Level Outputs

Transition times for TTL-compatible inputs are specified as follows. For a high-to-low transition on an input signal, the level at which the input is said to be no longer high is 2 V and the level at which the input is said to be low is 0.8 V. For a low-to-high transition on an input signal, the level at which the input is said to be no longer low is 0.8 V and the level at which the input is said to be no longer low is 0.8 V. For a low-to-high transition on an input signal, the level at which the input is said to be no longer low is 0.8 V. For a low-to-high transition on an input signal, the level at which the input is said to be no longer low is 0.8 V. For a low-to-high transition on an input signal, the level at which the input is said to be no longer low is 0.8 V. For a low-to-high transition on an input signal, the level at which the input is said to be no longer low is 0.8 V. For a low-to-high transition on an input signal, the level at which the input is said to be no longer low is 0.8 V. For a low-to-high transition on an input signal, the level at which the input is said to be no longer low is 0.8 V. For a low-to-high transition on an input signal, the level at which the input is said to be high is 2 V. See Figure 6.

SPRS038 – JANUARY 1996

#### PARAMETER MEASUREMENT INFORMATION

#### timing parameter symbology

Timing parameter symbols used herein were created in accordance with JEDEC Standard 100-A. In order to shorten the symbols, pin names that have both global and local applications are generally represented with (L) immediately preceding the basic signal name (for example,  $\overline{(L)RDYx}$  represents both the global term  $\overline{RDYx}$  and local term  $\overline{LRDYx}$ ). Other pin names and related terminology have been abbreviated as follows, unless otherwise noted:

| А       | (L)A30-(L)A0 or (L)Ax                                  | IACK  | IACK                                                                      |

|---------|--------------------------------------------------------|-------|---------------------------------------------------------------------------|

| AE      | (L)AE                                                  | IF    | IIOF(3-0) or IIOFx                                                        |

| ASYNCH  | Asynchronous reset signals in the high-impedance state | liof  | IIOF(3–0) or IIOFx                                                        |

| BYTE    | Byte transfer                                          | LOCK  | L)LOCK                                                                    |

| CA      | $\overline{CACK(0-5)}$ or $\overline{CACKx}$           | Р     | <sup>t</sup> c(H)                                                         |

| CD      | C(0-5)D7-C(0-5)D0 or CxDx                              | PAGE  | (L)PAGE0 and (L)PAGE1 or (L)PAGEx                                         |

| CE      | (L)CE0, (L)CE1, or (L)CEx                              | RDY   | $\overline{(L)RDY0}, \overline{(L)RDY1}, \text{ or } \overline{(L)RDYx}$  |

| CI      | CLKIN                                                  | RESET | RESET                                                                     |

| COMM    | Asynchronous reset signals                             | RW    | (L)R/ $\overline{W}$ 0, (L)R/ $\overline{W}$ 1, or (L)R/ $\overline{W}$ x |

| CONTROL | Control signals                                        | S     | (L)STRB0, (L)STRB1 or (L)STRBx                                            |

| CRQ     | $\overline{CREQ(0-5)}$ or $\overline{CREQx}$           | ST    | (L)STAT3-(L)STAT0 or (L)STATx                                             |

| CRDY    | $\overline{CRDY(0-5)}$ or $\overline{CRDYx}$           | TCK   | ТСК                                                                       |

| CS      | CSTRB(0-5) or CSTRBx                                   | TCLK  | TCLK0, TCLK1, or TCLKx                                                    |

| D       | (L)D31-(L)D0 or (L)Dx                                  | TDO   | TDO                                                                       |

| DE      | (L)DE                                                  | TMS   | TMS/TDI                                                                   |

| Н       | H1, H3                                                 | WORD  | 32-bit word transfer                                                      |

SPRS038 - JANUARY 1996

| NO. |                       |                                                                | TMS320                | )C40-40               | TMS320                | C40-50                | TMS320                | C40-60                | UNIT |

|-----|-----------------------|----------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------|

| NO. |                       |                                                                | MIN                   | MAX                   | MIN                   | MAX                   | MIN                   | MAX                   | UNIT |

| 1   | <sup>t</sup> f(CI)    | Fall time, CLKIN                                               |                       | 5†                    |                       | 5†                    |                       | 5†                    | ns   |

| 2   | <sup>t</sup> w(CIL)   | Pulse duration, CLKIN low, $t_{C(CI)} = MIN$                   | 8                     |                       | 7                     |                       | 5                     |                       | ns   |

| 3   | <sup>t</sup> w(CIH)   | Pulse duration, CLKIN high, $t_{C(CI)} = MIN$                  | 8                     |                       | 7                     |                       | 5                     |                       | ns   |

| 4   | <sup>t</sup> r(CI)    | Rise time, CLKIN                                               |                       | 5†                    |                       | 5†                    |                       | 5†                    | ns   |

| 5   | <sup>t</sup> c(CI)    | Cycle time, CLKIN                                              | 25                    | 242.5                 | 20                    | 242.5                 | 16.67                 | 242.5                 | ns   |

| 6   | <sup>t</sup> f(H)     | Fall time, H1 and H3                                           |                       | 3                     |                       | 3                     |                       | 3                     | ns   |

| 7   | <sup>t</sup> w(HL)    | Pulse duration, H1 and H3 low                                  | t <sub>c(CI)</sub> -6 | t <sub>c(CI)</sub> +6 | t <sub>c(CI)</sub> -6 | t <sub>c(CI)</sub> +6 | t <sub>c(CI)</sub> -6 | t <sub>c(CI)</sub> +6 | ns   |

| 8   | <sup>t</sup> w(HH)    | Pulse duration, H1 and H3 high                                 | t <sub>c(CI)</sub> -6 | t <sub>c(CI)</sub> +6 | t <sub>c(CI)</sub> -6 | t <sub>c(CI)</sub> +6 | t <sub>c(CI)</sub> -6 | t <sub>c(CI)</sub> +6 | ns   |

| 9   | <sup>t</sup> r(H)     | Rise time, H1 and H3                                           |                       | 4                     |                       | 4                     |                       | 4                     | ns   |

| 9.1 | <sup>t</sup> d(HL-HH) | Delay time from H1 low to H3 high or<br>from H3 low to H1 high | -1                    | 4                     | -1                    | 4                     | -1                    | 4                     | ns   |

| 10  | <sup>t</sup> c(H)     | Cycle time, H1 and H3                                          | 50                    | 485                   | 40                    | 485                   | 33.3                  | 485                   | ns   |

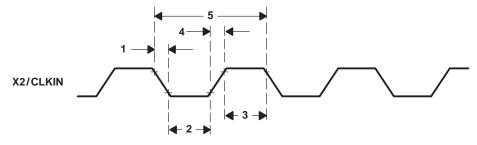

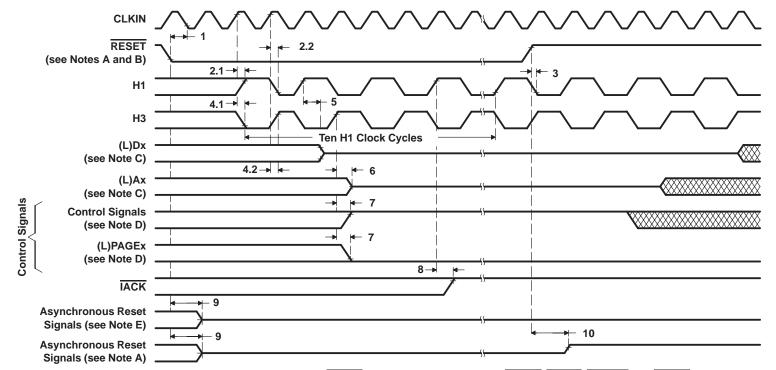

### timing for X2/CLKIN, H1, H3 (see Figure 7 and Figure 8)

<sup>†</sup> This value is specified by design but not tested.

#### Figure 7. X2/CLKIN Timing

#### Figure 8. H1 and H3 Timings

SPRS038 – JANUARY 1996

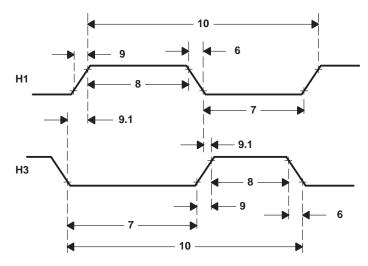

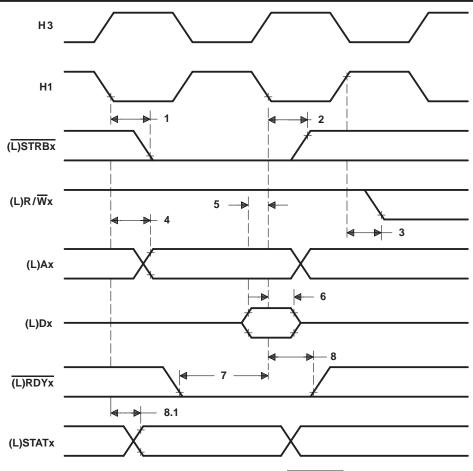

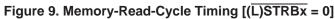

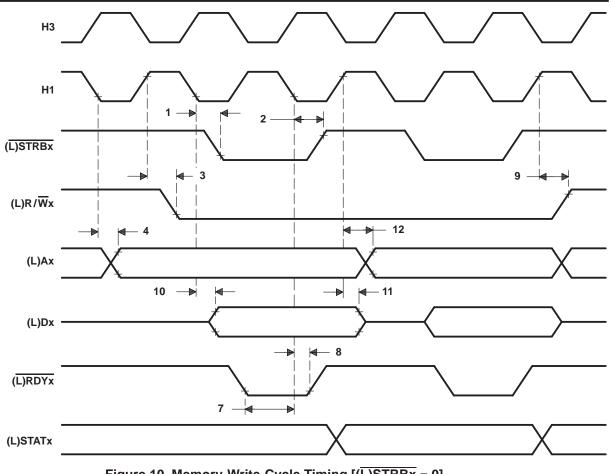

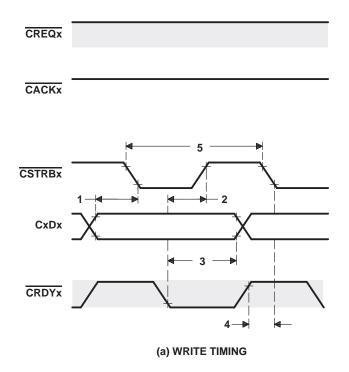

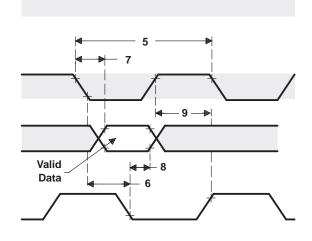

# memory-read-cycle and memory-write-cycle timing [(L)STRBx = 0] (see Note 5, Figure 9 and Figure 10)

| NO. |                           |                                                                       | TMS3200 | C40-40 | TMS3200 | 240-50 | TMS3200 | C40-60 | UNIT |

|-----|---------------------------|-----------------------------------------------------------------------|---------|--------|---------|--------|---------|--------|------|

| NO. |                           |                                                                       | MIN     | MAX    | MIN     | MAX    | MIN     | MAX    | UNIT |

| 1   | <sup>t</sup> d(H1L-SL)    | Delay time, H1 low to (L)STRBx low                                    | 0†      | 9      | 0†      | 9      | 0†      | 8      | ns   |

| 2   | <sup>t</sup> d(H1L-SH)    | Delay time, H1 low to (L)STRBx high                                   | 0†      | 9      | 0†      | 9      | 0†      | 8      | ns   |

| 3   | <sup>t</sup> d(H1H-RWL)   | Delay time, H1 high to (L)R/ $\overline{W}x$ low                      | 0†      | 9      | 0†      | 9      | 0†      | 8      | ns   |

| 4   | <sup>t</sup> d(H1L-A)     | Delay time, H1 low to (L)Ax valid                                     | 0†      | 9      | 0†      | 9      | 0†      | 8      | ns   |

| 5   | <sup>t</sup> su(D-H1L)R   | Setup time, (L)Dx valid before H1 low (read)                          | 15      |        | 10      |        | 9       |        | ns   |

| 6   | <sup>t</sup> h(H1L-D)R    | Hold time, (L)Dx after H1 low (read)                                  | 0       |        | 0       |        | 0       |        | ns   |

| 7   | t <sub>su</sub> (RDY-H1L) | Setup time, $(\overline{L})RDYx$ valid before H1 low                  | 25‡     |        | 20‡     |        | 18†     |        | ns   |

| 8   | <sup>t</sup> h(H1L-RDY)   | Hold time, $(\overline{L})RDYx$ after H1 low                          | 0       |        | 0       |        | 0       |        | ns   |

| 8.1 | <sup>t</sup> d(H1L-ST)    | Delay time, H1 low to (L)STAT3-(L)STAT0 valid                         |         | 9      |         | 8      |         | 8      | ns   |

| 9   | <sup>t</sup> d(H1H-RWH)W  | Delay time, H1 high to (L)R/ $\overline{W}x$ high (write)             | 0†      | 9      | 0†      | 9      | 0†      | 8      | ns   |

| 10  | <sup>t</sup> v(H1L-D)W    | Valid time, (L)Dx after H1 low (write)                                |         | 16     |         | 16     |         | 13     | ns   |

| 11  | <sup>t</sup> h(H1H-D)W    | Hold time, (L)Dx after H1 high (write)                                | 0       |        | 0       |        | 0       |        | ns   |

| 12  | <sup>t</sup> d(H1H-A)     | Delay time, H1 high to address valid on back-<br>to-back write cycles |         | 13     |         | 9      |         | 8      | ns   |

<sup>†</sup> This value is specified by design but not tested.

<sup>‡</sup> If this setup time is not met, the read/write operation is not assured.

NOTE 5: For consecutive reads, (L)R/Wx stays high and (L)STRBx stays low.

SPRS038 – JANUARY 1996

SPRS038 – JANUARY 1996

SPRS038 - JANUARY 1996

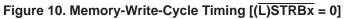

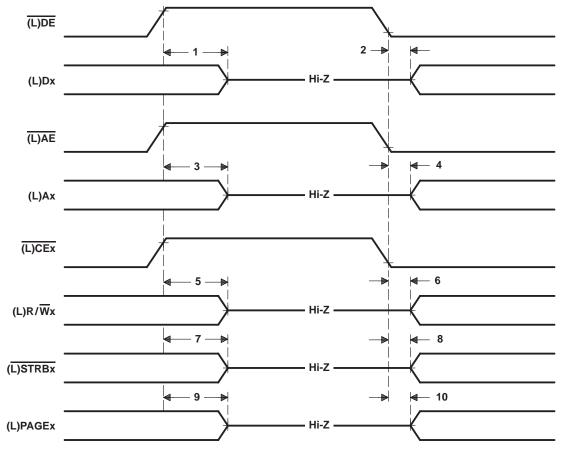

#### $\overline{(L)DE}$ -, $\overline{(L)AE}$ -, and $\overline{(L)CEx}$ -enable timing (see Figure 11)

| NO. |                           |                                                                                                                 | TMS320<br>TMS320 |     | TMS3200 | C40-60 |    |

|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|-----|---------|--------|----|

|     |                           |                                                                                                                 | MIN              | MAX | MIN     | MAX    |    |

| 1   | <sup>t</sup> d(DEH-DZ)    | Delay time, $\overline{(L)DE}$ high to (L)D0–(L)D31 in the high-impedance state                                 | 0†               | 15‡ | 0†      | 15‡    | ns |

| 2   | <sup>t</sup> d(DEL-DV)    | Delay time, (L)DE low to (L)D0-(L)D31 valid                                                                     | 0†               | 21  | 0†      | 16     | ns |

| 3   | <sup>t</sup> d(AEH-AZ)    | Delay time, $\overline{(L)AE}$ high to (L)A0–(L)A30 in the high-impedance state                                 | 0†               | 15‡ | 0†      | 15‡    | ns |

| 4   | <sup>t</sup> d(AEL-AV)    | Delay time, (L)AE low to (L)A0-(L)A30 valid                                                                     | 0†               | 18  | 0†      | 16     | ns |

| 5   | <sup>t</sup> d(CEH-RWZ)   | Delay time, $\overline{(L)CEx}$ high to $(L)R/\overline{W}0$ , $(L)R/\overline{W}1$ in the high-impedance state | 0†               | 15‡ | 0†      | 15‡    | ns |

| 6   | <sup>t</sup> d(CEL-RWV)   | Delay time, $\overline{(L)CEx}$ low to $(L)R/\overline{W}0$ , $(L)R/\overline{W}1$ valid                        | 0†               | 21  | 0†      | 16     | ns |

| 7   | <sup>t</sup> d(CEH-SZ)    | Delay time, (L)CEx high to (L)STRB0, (L)STRB1 in the high-impedance state                                       | 0†               | 15‡ | 0†      | 15‡    | ns |

| 8   | <sup>t</sup> d(CEL-SV)    | Delay time, (L)CEx low to (L)STRB0, (L)STRB1 valid                                                              | 0†               | 21  | 0†      | 16     | ns |

| 9   | <sup>t</sup> d(CEH-PAGEZ) | Delay time, (L)CEx high to (L)PAGE0, (L)PAGE1 in the high-impedance state                                       | 0†               | 15‡ | 0†      | 15‡    | ns |

| 10  | td(CEL-PAGEV)             | Delay time, (L)CEx low to (L)PAGE0, (L)PAGE1 valid                                                              | 0†               | 21  | 0†      | 16     | ns |

<sup>†</sup>This value is specified by design but not tested.

<sup>‡</sup>This value is characterized but not tested.

Figure 11.  $\overline{(L)DE}$ -,  $\overline{(L)AE}$ -, and  $\overline{(L)CEx}$ -Enable Timings

SPRS038 – JANUARY 1996

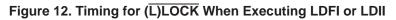

#### timing for ( $\overline{L}$ )LOCK when executing LDFI or LDII (see Figure 12)

|     |                                              |                  | TMS320 | C40-40             | TMS320           | C40-50   | TMS3200 | C40-60 | UNIT |

|-----|----------------------------------------------|------------------|--------|--------------------|------------------|----------|---------|--------|------|

| NO. |                                              |                  | MIN    | MAX                | MIN              | MAX      | MIN     | MAX    | UNIT |

| 1   | <sup>t</sup> d(H1L-LOCKL) Delay time, H1 lov | v to (L)LOCK low |        | 11                 |                  | 8        |         | 8      | ns   |

|     | H3                                           |                  |        | LDFI or<br>Externa | LDII<br>I Access | <u> </u> |         |        |      |

|     | H1                                           |                  |        | _/                 |                  |          |         |        |      |

|     | (L)STRBx                                     |                  | /      |                    |                  |          |         |        |      |

|     | (L)R/₩x                                      |                  |        |                    |                  |          |         |        |      |

|     | (L)Ax                                        |                  |        | $\times$           |                  |          |         |        |      |

|     | (L)Dx                                        |                  |        | <b>&gt;</b>        |                  |          |         |        |      |

|     | ( <mark>L)RDYx</mark>                        |                  | /      |                    |                  |          |         |        |      |

|     | (L)LOCK                                      |                  |        |                    |                  |          |         |        |      |

SPRS038 - JANUARY 1996

| NO.                                                             | TMS320 | C40-40 | TMS320 | C40-50 | TMS320 | C40-60 | UNIT |  |  |  |  |

|-----------------------------------------------------------------|--------|--------|--------|--------|--------|--------|------|--|--|--|--|

| NO.                                                             | MIN    | MAX    | MIN    | MAX    | MIN    | MAX    |      |  |  |  |  |

| 1 t <sub>d</sub> (H1L-LOCKH) Delay time, H1 low to (L)LOCK high |        | 11     |        | 8      |        | 8      | ns   |  |  |  |  |

#### timing for (L)LOCK when executing STFI or STII (see Figure 13)

Figure 13. Timing for  $\overline{(L)LOCK}$  When Executing STFI or STII

SPRS038 – JANUARY 1996

#### timing for $\overline{(L)LOCK}$ when executing SIGI (see Figure 14)

| NO.        |                                 |                              | TMS320 | C40-40 | TMS320    | C40-50   | TMS320 | C40-60 | UNIT |

|------------|---------------------------------|------------------------------|--------|--------|-----------|----------|--------|--------|------|

| <u>NO.</u> |                                 |                              | MIN    | MAX    | MIN       | MAX      | MIN    | MAX    | UNIT |

| 1          | t <sub>d(H1L-LOCKL)</sub> Delay | time, H1 low to (L)LOCK low  |        | 11     |           | 8        |        | 8      | ns   |

| 2          | <sup>t</sup> d(H1L-LOCKH) Delay | time, H1 low to (L)LOCK high |        | 11     |           | 8        |        | 8      |      |

|            | Н3                              |                              |        |        |           | <u> </u> |        |        |      |

|            | H1                              |                              |        | 2      |           |          |        |        |      |

|            | (L)LOCK                         |                              |        |        |           |          |        |        |      |

|            | (L)R/₩x                         |                              |        |        |           |          |        |        |      |

|            | (L)Ax                           |                              |        |        |           |          |        |        |      |

|            | (L)Dx                           |                              |        |        |           |          |        |        |      |

|            | (L)RDYx                         |                              |        |        |           |          |        |        |      |

|            | (L)STATx                        |                              |        |        |           |          |        |        |      |

|            |                                 | Figure 14. Timing for (L)LO  | K When | Execu  | iting SIC | از       |        |        |      |

SPRS038 - JANUARY 1996

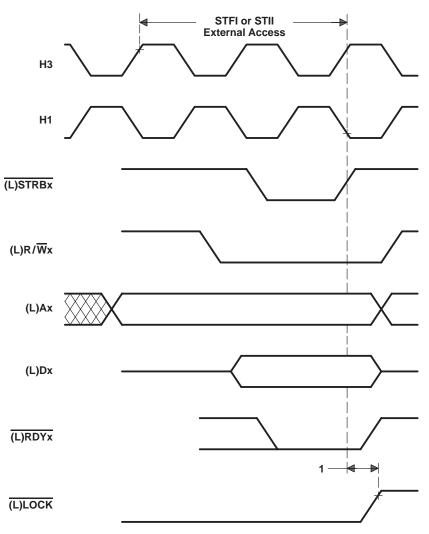

#### timing for (L)PAGE0, (L)PAGE1 during memory access to a different page (see Figure 15)

| NO. | NO.                       |                                                                  |     | C40-40<br>C40-50 | TMS3200 | UNIT |    |

|-----|---------------------------|------------------------------------------------------------------|-----|------------------|---------|------|----|

|     |                           |                                                                  | MIN | MAX              | MIN     | MAX  |    |

| 1   | <sup>t</sup> d(H1L-PAGEH) | Delay time, H1 low to (L)PAGEx high for access to different page | 0   | 9                | 0       | 8    | ns |

| 2   | <sup>t</sup> d(H1L-PAGEL) | Delay time, H1 low to (L)PAGEx low for access to different page  | 0   | 9                | 0       | 8    | ns |

Figure 15. (L)PAGE0, (L)PAGE1 Timing Cycle, Memory Access to a Different Page

SPRS038 – JANUARY 1996

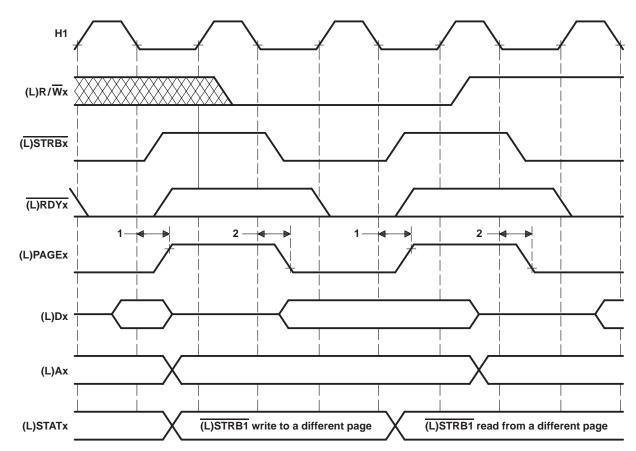

| NO.  |                         |        |                       |      |        |               | TMS3200 | 40-40 | TMS320 | C40-50  | TMS320   | C40-60        | UNIT |

|------|-------------------------|--------|-----------------------|------|--------|---------------|---------|-------|--------|---------|----------|---------------|------|

| NO.  |                         |        |                       |      |        |               | MIN     | MAX   | MIN    | MAX     | MIN      | MAX           | UNIT |

| 1    | <sup>t</sup> v(H1L-IIOF | H1 lov | / to IIOFx va         | alid |        |               |         | 16    |        | 14      |          | 14            | ns   |

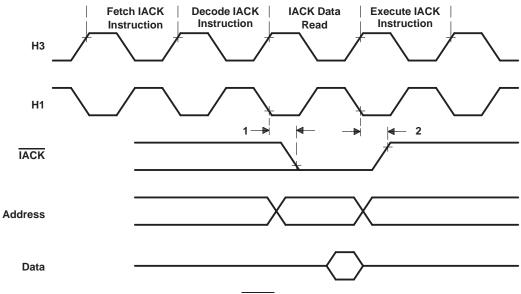

|      | н                       | 3      | Fetch Lo<br>Instructi |      | Decode |               | Re      | ead   | E      | Execute |          | ~             | -    |

|      | н                       | 1      |                       |      |        | $\overline{}$ | _/      |       |        |         | <u>\</u> |               | -    |

| FLAG | x (IIF Registe          | r)     |                       |      |        |               |         |       |        |         |          | 1 or 0<br>— 1 | -    |

|      | IIOFx Pin               | s      |                       |      |        |               |         |       |        |         |          | -             | -    |

#### timing for the IIOFx when configured as an output (see Figure 16)

SPRS038 – JANUARY 1996

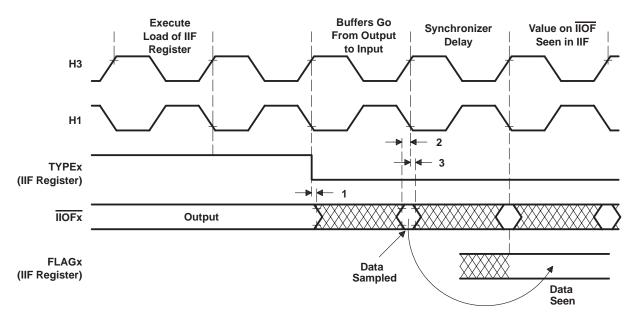

### timing of IIOFx changing from output to input mode (see Figure 17)

| NO. |                           |                                 |     | C40-40<br>C40-50 | TMS3200 | UNIT |    |

|-----|---------------------------|---------------------------------|-----|------------------|---------|------|----|

|     |                           |                                 | MIN | MAX              | MIN     | MAX  |    |

| 1   | <sup>t</sup> h(H1L-IIOF)  | Hold time, IIOFx after H1 low   |     | 14†              |         | 14†  | ns |

| 2   | <sup>t</sup> su(IIOF-H1L) | Setup time, IIOFx before H1 low | 11  |                  | 11      |      | ns |

| 3   | <sup>t</sup> h(H1L-IIOF)  | Hold time, IIOFx after H1 low   | 0   |                  | 0       |      | ns |

<sup>†</sup> This value is specified by design but not tested.

Figure 17. Change of IIOFx From Output to Input Mode

SPRS038 - JANUARY 1996

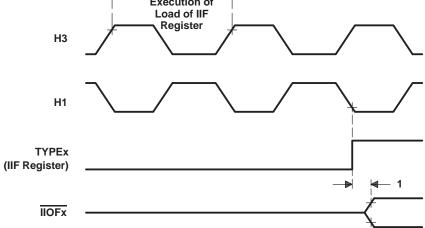

#### timing of IIOFx changing from input to output mode (see Figure 18)

| NO. |                          |                                                            |     |     | TMS3200 | C40-50 | TMS3200 | C40-60 | UNIT |