SLUS601-MAY 2005

# MIDRANGE INPUT SYNCHRONOUS BUCK CONTROLLER WITH ADVANCED SEQUENCING AND OUTPUT MARGINING

## **FEATURES**

- Operation over 4.5 V to 18 V Input Range

- Adjustable Frequency (Between 100 kHz and 600 kHz) Current Feedback Control

- Output Voltage Range From 0.7 V to 5.5 V

- Simultaneous, Ratiometric and Sequential Startup Sequencing

- Adaptive Gate Drive

- Remote Sensing (Via Separate GND/PGND)

- Internal Gate Drivers for N-channel MOSFETs

- Internal 5-V Regulator

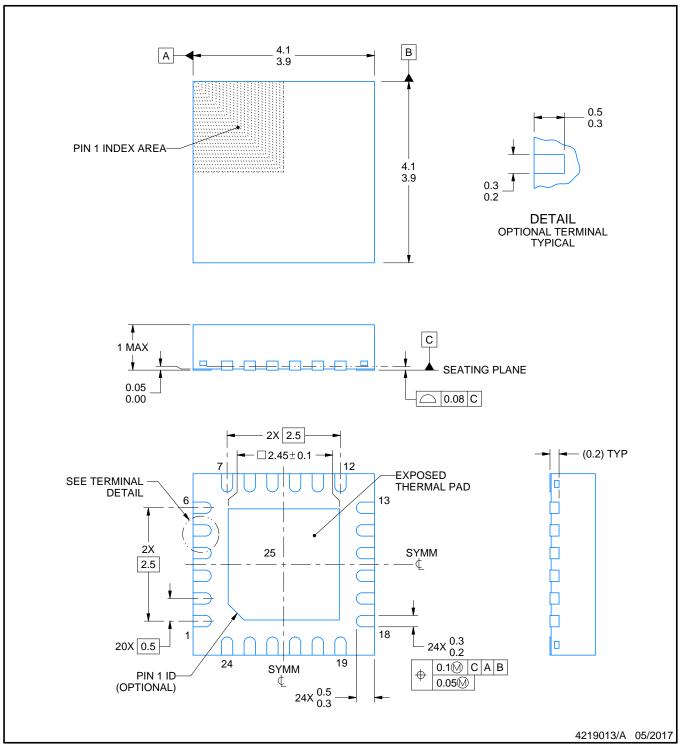

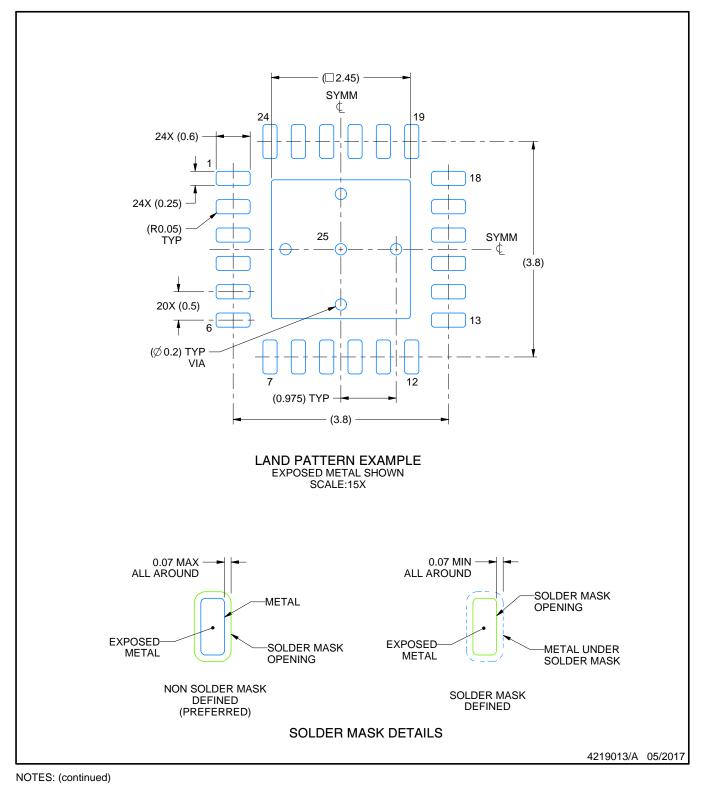

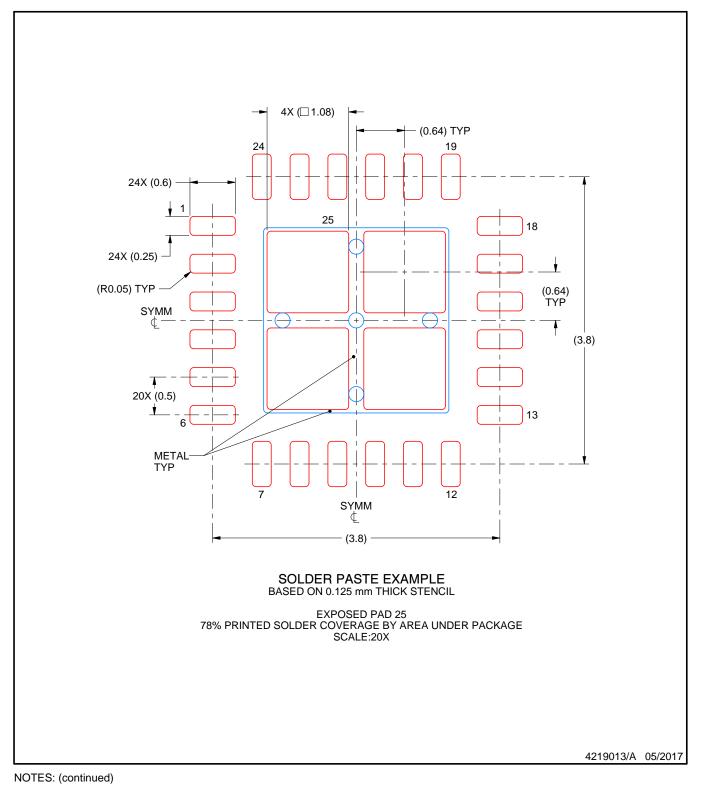

- 24-Pin QFN Package

- Thermal Shutdown

- Programmable Overcurrent Protection

- Power Good Indicator

- 1%, 690-mV Reference

- Output Margining, 3% and 5%

- Programmable UVLO (with Programmable Hysteresis)

- Frequency Synchronization

## APPLICATIONS

- Servers

- Networking Equipment

- Cable Modems and Routers

- XDSL Modems and Routers

- Set-Top Boxes

- Telecommunications Equipment

- Power Supply Modules

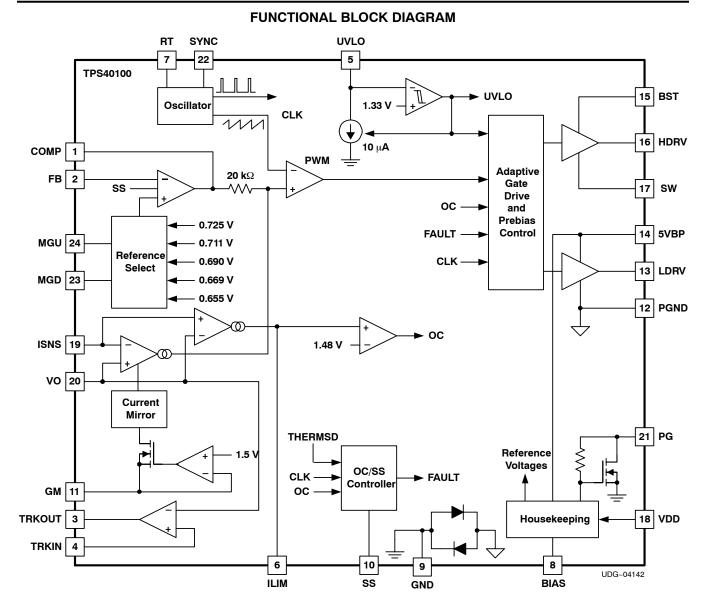

## DESCRIPTION

The TPS40100 is a mid voltage, wide-input (between 4.5 V and 18 V), synchronous, step-down controller. The TPS40100 offers programmable closed loop soft-start, programmable UVLO (with programmable hysteresis), programmable inductor sensed current limit and can be synchronized to other timebases. The TPS40100 incorporates MOSFET gate drivers for external N-channel high-side and synchronous rectifier (SR) MOSFET. Gate drive logic incorporates adaptive anti-cross conduction circuitry for improved efficiency, reducing both cross conduction and diode conduction in the rectifier MOSFET. The externally programmable current limit provides a hiccup overcurrent recovery characteristic.

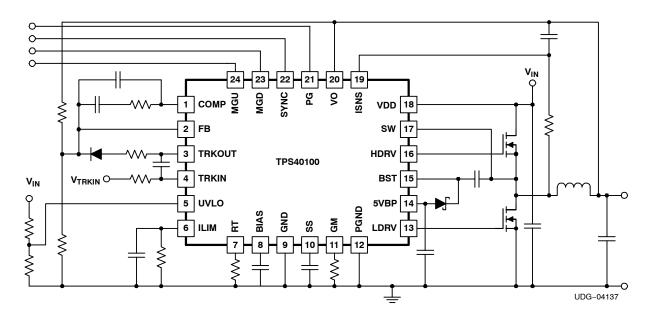

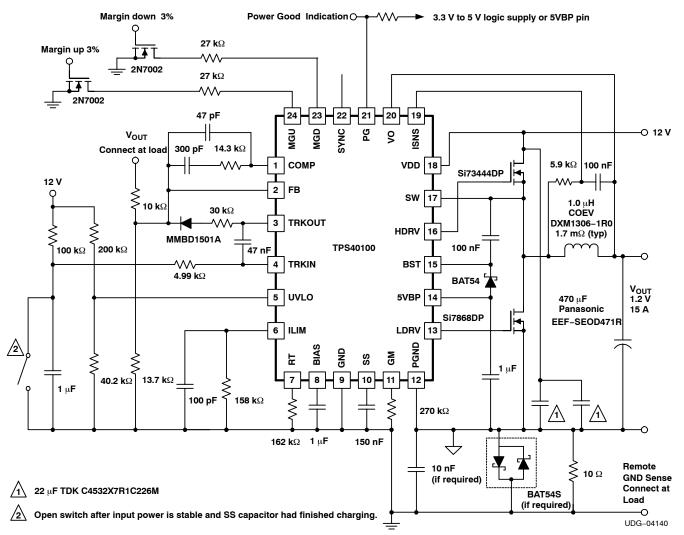

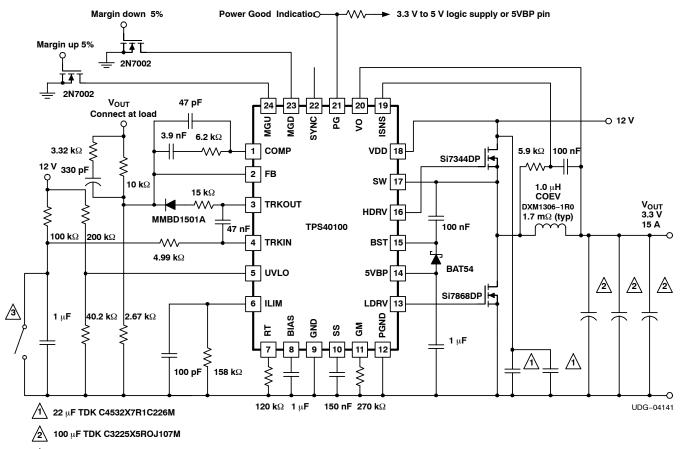

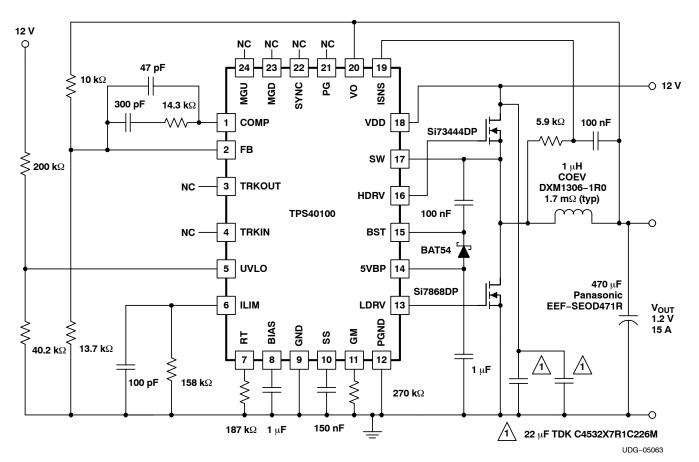

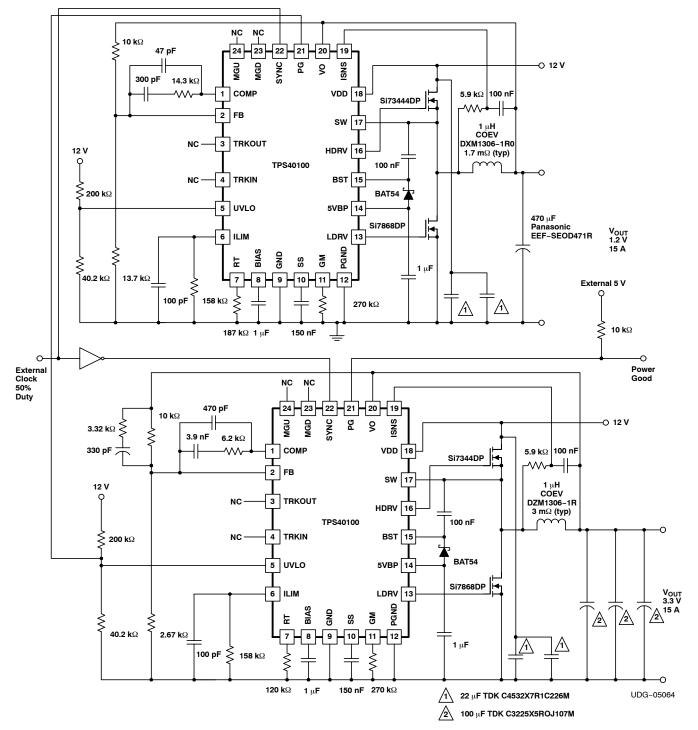

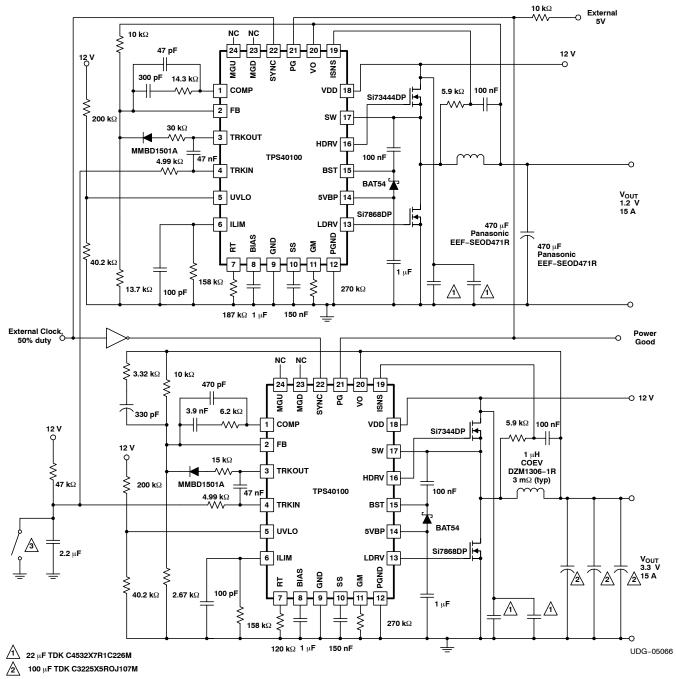

## TYPICAL APPLICATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

A

#### TEXAS INSTRUMENTS www.ti.com

#### **ORDERING INFORMATION**

| T <sub>A</sub> | PACKAGE | PART NUMBER <sup>(1)</sup> |  |  |

|----------------|---------|----------------------------|--|--|

| -40°C to 85°C  |         | TPS40100RGER               |  |  |

| -40 C 10 85 C  | QFN     | TPS40100RGET               |  |  |

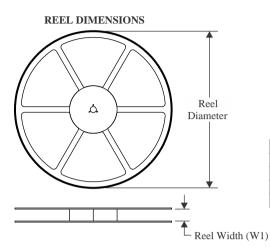

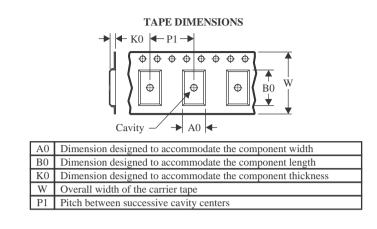

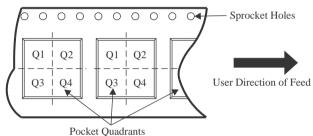

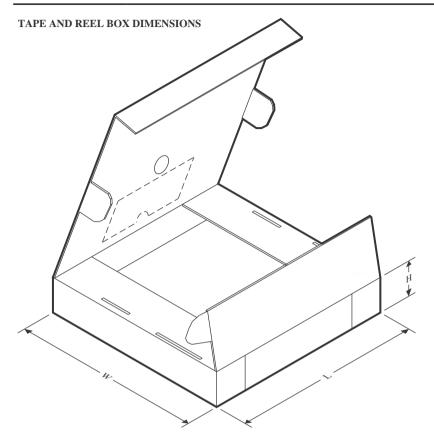

(1) The QFN package (RGE) is available taped and reeled only. Use large reel device type R (TPS40100RGER) to order quantities of 3,000 per reel. Use small reel device type T (TPS40100RGET) to order quantities of 250 per reel.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                  |                        |                                                                    | TPS40100                 | UNIT |

|------------------|------------------------|--------------------------------------------------------------------|--------------------------|------|

|                  |                        | VDD                                                                | -0.3 to 20               |      |

|                  |                        | 5VBP, BIAS, FB, ILIM, ISNS, LDRV, MGU, MGD, PG, SS, SYNC, UVLO, VO | -0.3 to 6                |      |

|                  |                        | BST to SW, HDRV to SW <sup>(2)</sup>                               | -0.3 to 6.0              |      |

| V <sub>IN</sub>  | Input voltage range    | SW                                                                 | -1.5 to V <sub>VIN</sub> | V    |

|                  |                        | SW (transient) < 100 ns                                            | -6 to 30                 |      |

|                  |                        | TRKIN                                                              | -0.3 to 20               |      |

|                  |                        | GND to PGND                                                        | -0.3 to 0.3              |      |

|                  |                        | TRKOUT                                                             | -0.3 to 8.0              |      |

|                  |                        | HDRV, LDRV (RMS)                                                   | 0.5                      |      |

|                  |                        | HDRV, LDRV (peak)                                                  | 2.0                      | — A  |

|                  |                        | FB, COMP, TRKOUT                                                   | 10 to -10                | mA   |

|                  |                        | SS                                                                 | 20 to -20                |      |

| IN               | Input current range    | PG                                                                 | 20                       |      |

|                  |                        | GM                                                                 | 1                        | mA   |

|                  |                        | RT                                                                 | 10                       |      |

|                  |                        | V5BP                                                               | 50 <sup>(3)</sup>        |      |

|                  |                        | RT source                                                          | 100                      | μA   |

| ΓJ               | Operating junction tem | -40 to 125                                                         |                          |      |

| T <sub>stg</sub> | Storage temperature    |                                                                    | -55 to 150               |      |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) BST to SW and HDRV to SW are relative measurements. BST and HDRV can be this amount of voltage above or below the voltage at SW.

(3) V5BP current includes gate drive current requirements. Observe maximum T<sub>J</sub> rating for the device.

## **ELECTRICAL CHARACTERISTICS**

$-40^{\circ}\text{C} \le \text{T}_{\text{A}} = \text{T}_{\text{J}} \le 85^{\circ}\text{C}, \text{ V}_{\text{VDD}} = 12 \text{ V}, \text{ R}_{\text{RT}} = 182 \text{ k}\Omega, \text{ R}_{\text{GM}} = 232 \text{ k}\Omega, \text{ R}_{\text{ILIM}} = 121 \text{ k}\Omega \text{ (unless otherwise noted)}$

|                      | PARAMETER                                           | TEST CONDITIONS                                                                                                                                          | MIN       | TYP  | MAX  | UNIT             |

|----------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|------------------|

| INPUT VO             | LTAGE                                               |                                                                                                                                                          |           |      |      |                  |

| V <sub>VDD</sub>     | Operating range                                     |                                                                                                                                                          | 4.5       |      | 18.0 | V                |

| OPERATIN             | IG CURRENT                                          |                                                                                                                                                          |           |      |      |                  |

| I <sub>DD</sub>      | Quiescent current                                   | V <sub>FB</sub> > 0.8 V, 0% duty cycle                                                                                                                   | 1.3       | 1.8  | 2.5  | mA               |

| I <sub>SD</sub>      | Shutdown current                                    | V <sub>UVLO</sub> < 1 V                                                                                                                                  |           | 500  |      | μA               |

| 5VPB                 |                                                     | · · ·                                                                                                                                                    |           |      |      |                  |

|                      |                                                     | $7 \text{ V} \le \text{V}_{\text{VDD}} \le 18 \text{ V}, 0 \text{ mA} \le \text{I}_{\text{LOAD}} \le 30 \text{ mA}$                                      | 4.7       | 5.0  | 5.3  |                  |

|                      | Internal regulator                                  | $4.5 \text{ V} \le \text{V}_{\text{VDD}} < 7 \text{ V}, 0 \text{ mA} \le \text{I}_{\text{LOAD}} \le 30 \text{ mA}$                                       | 4.3       | 5.0  | 5.3  | V                |

| OSCILLAT             | OR/RAMP GENERATOR                                   | · · · · ·                                                                                                                                                |           |      |      |                  |

| f <sub>SW</sub>      | Programmable oscillator frequency                   |                                                                                                                                                          | 100       |      | 600  |                  |

|                      | Oscillator frequency accuracy                       | $4.5 \text{ V} \le \text{V}_{\text{VDD}} < 18 \text{ V},$<br>$-40^{\circ}\text{C} \le \text{T}_{\text{A}} = \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ | 250       | 275  | 300  | kHz              |

| V <sub>RAMP</sub>    | Ramp amplitude <sup>(1)</sup>                       |                                                                                                                                                          |           | 0.5  |      | V <sub>P-P</sub> |

| t <sub>OFF</sub>     | Fixed off-time                                      |                                                                                                                                                          |           | 100  | 150  | ns               |

| D <sub>MIN</sub>     | Minimum duty cycle                                  |                                                                                                                                                          |           |      | 0%   |                  |

| t <sub>MIN</sub>     | Minimum controllable pulse width <sup>(1)</sup>     | C <sub>LOAD</sub> = 4.7 nF, -40°C ≤ T <sub>A</sub> = T <sub>J</sub> ≤ 125°C                                                                              |           |      | 175  | ns               |

| V <sub>VLY</sub>     | Valley voltage <sup>(1)</sup>                       |                                                                                                                                                          | 1.0       | 1.6  | 2.0  | V                |

|                      | CY SYNCHRONIZATION                                  |                                                                                                                                                          |           |      |      |                  |

| V <sub>IH</sub>      | High-level input voltage                            |                                                                                                                                                          | 2         |      |      |                  |

| VIL                  | Low-level input voltage                             |                                                                                                                                                          |           |      | 0.8  | V                |

| I <sub>SYNC</sub>    | Input current, SYNC                                 | V <sub>SYNC</sub> = 2.5 V                                                                                                                                | 4.0       | 5.5  | 10.0 | μA               |

| t <sub>SYNC</sub>    | Mimimum pulse width, SYNC                           |                                                                                                                                                          | 50        |      |      |                  |

| t <sub>SYNC SH</sub> | Minimum set-up/hold time, SYNC <sup>(2)</sup>       |                                                                                                                                                          | 100       |      |      | ns               |

|                      | RT AND FAULT IDLE                                   |                                                                                                                                                          |           |      |      |                  |

| I <sub>SS</sub>      | Soft-start source (charge) current                  |                                                                                                                                                          | 13        | 20   | 25   |                  |

| I <sub>SS SINK</sub> | Soft-start sink (discharge) current                 |                                                                                                                                                          | 3.4       | 5.0  | 6.6  | μA               |

| V <sub>SSC</sub>     | Soft-start completed voltage                        |                                                                                                                                                          | 3.25      | 3.40 | 3.75 |                  |

| V <sub>SSD</sub>     | Soft-start discharged voltage                       |                                                                                                                                                          | 0.15      | 0.20 | 0.25 | V                |

|                      | Retry interval time to SS time ratio <sup>(1)</sup> |                                                                                                                                                          | 16        |      |      |                  |

| V <sub>SSOS</sub>    | Offset from SS to error amplifier                   |                                                                                                                                                          | 300       | 500  | 800  | mV               |

| ERROR A              | MPLIFIER                                            |                                                                                                                                                          |           |      |      |                  |

| GBWP                 | Gain bandwidth product <sup>(1)</sup>               |                                                                                                                                                          | 3.5       | 5.0  |      | MHz              |

| AVOL                 | Open loop                                           |                                                                                                                                                          | 60        | 80   |      | dB               |

| I <sub>BIAS</sub>    | Input bias current, FB                              |                                                                                                                                                          |           | 50   | 200  | nA               |

| I <sub>OH</sub>      | High-level output current                           |                                                                                                                                                          | 2         | 3    |      |                  |

| I <sub>OL</sub>      | Low-level output current                            |                                                                                                                                                          | 2         | 3    |      | mA               |

|                      | Slew rate <sup>(1)</sup>                            |                                                                                                                                                          |           | 2.1  |      | V/µs             |

| FEEDBAC              | K REFERENCE                                         |                                                                                                                                                          |           |      |      |                  |

|                      |                                                     | T <sub>A</sub> =25°C                                                                                                                                     | 686 690 6 |      |      |                  |

| $V_{FB}$             | Feedback voltage reference                          | -40°C < T <sub>A</sub> = T <sub>J</sub> ≤ 125°C                                                                                                          | 683       |      | 697  | mV               |

(1) Ensured by design. Not production tested.

(2) To meet set up time requirements for the synchronization circuit, a negative logic pulse must be greater than 100 ns wide.

# **ELECTRICAL CHARACTERISTICS (continued)**

|                       | PARAMETER                                                    | TEST CONDITIONS                                               | MIN  | TYP   | MAX  | UNIT   |

|-----------------------|--------------------------------------------------------------|---------------------------------------------------------------|------|-------|------|--------|

| VOLTAGE N             | ARGINING                                                     |                                                               |      |       |      |        |

| .,                    | Feedback voltage margin 5% up                                | V <sub>MGU</sub> ≤ 500 mV                                     | 715  | 725   | 735  |        |

| V <sub>FBMGU</sub>    | Feedback voltage margin 3% up                                | 2 V ≤ V <sub>MGU</sub> ≤ 3 V                                  | 700  | 711   | 720  | mV     |

| I <sub>MGUP</sub>     | Margin-up bias current                                       |                                                               | 60   | 80    | 100  | μA     |

|                       | Feedback voltage margin 5% down                              | V <sub>MGD</sub> ≤ 500 mV                                     | 645  | 655   | 665  |        |

| V <sub>FBMGD</sub>    | Feedback voltage margin 3% down                              | $2 \text{ V} \le \text{V}_{MGD} \le 3 \text{ V}$              | 660  | 669   | 680  | mA     |

| I <sub>MGDN</sub>     | Margin-down bias current                                     |                                                               | 60   | 80    | 100  | μA     |

| t <sub>MGDLY</sub>    | Margining delay time <sup>(3)</sup>                          |                                                               |      | 12    | 30   |        |

| t <sub>MGTRAN</sub>   | Margining transition time                                    |                                                               | 1.5  | 7.0   |      | ms     |

|                       | SENSE AMPLIFIER                                              |                                                               |      |       |      |        |

| gm <sub>CSA</sub>     | Current sense amplifier gain                                 | T <sub>J</sub> =25°C                                          | 300  | 333   | 365  | μS     |

| TC <sub>GM</sub>      | Amplifier gain temperature coefficient                       |                                                               |      | -2000 |      | ppm/°C |

| V <sub>GMLIN</sub>    | Gm linear range voltage                                      | T <sub>J</sub> =25°C                                          | -50  |       | 50   | mV     |

| IISNS                 | Bias current at ISNS pin                                     | V <sub>VO</sub> = V <sub>ISNS</sub> = 3.3 V                   |      |       | 250  | nA     |

|                       | · · · · · · · · · · · · · · · · · · ·                        |                                                               | 0    |       | 6    |        |

| V <sub>GMCM</sub>     | Input voltage common mode                                    | $4.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$    | 0    |       | 3.6  | V      |

| CURRENT L             |                                                              |                                                               |      |       |      |        |

| V <sub>ILIM</sub>     | ILIM pin voltage to trip overcurrent                         |                                                               | 1.44 | 1.48  | 1.52 | V      |

|                       | Current limit comparator propagation delay                   | HDRV transition from on to off                                |      | 70    | 140  | ns     |

|                       | ECIFICATIONS                                                 |                                                               |      |       | 110  | 110    |

| t <sub>RHDRV</sub>    | HIgh-side driver rise time <sup>(4)</sup>                    | C <sub>LOAD</sub> = 4.7 nF                                    |      | 57    |      |        |

|                       | High-side driver fall time <sup>(4)</sup>                    | $C_{\text{LOAD}} = 4.7 \text{ nF}$                            |      | 47    |      | ns     |

| t <sub>FHDRV</sub>    | High-side driver peak source current <sup>(4)</sup>          | OLOAD - 4.7 m                                                 |      | 800   |      |        |

| HDRVSRPKS             | High-side driver source current at 2.5 $V^{(4)}$             | V <sub>HDRV</sub> - V <sub>SW</sub> = 2.5 V                   |      | 700   |      | mA     |

| HDRVSRMIL             | High-side driver peak sink current <sup>(4)</sup>            | $v_{HDRV} - v_{SW} = 2.5 v$                                   |      | 1.3   |      |        |

| I <sub>HSDVSNPK</sub> |                                                              |                                                               |      |       |      | А      |

| HDRVSNMIL             | High-side driver sink current at 2.5 V <sup>(4)</sup>        | $V_{HDRV} - V_{SW} = 2.5 V$                                   |      | 1.2   | 4.0  |        |

| R <sub>HDRVUP</sub>   | High-side driver pullup resistance                           | $I_{HDRV} = 300 \text{ mA}$                                   |      | 2.4   | 4.0  | Ω      |

| R <sub>HDRVDN</sub>   | High-side driver pulldown resistance                         | $I_{HDRV} = 300 \text{ mA}$                                   |      | 1.0   | 1.8  |        |

| t <sub>RLDRV</sub>    | Low-side driver rise time <sup>(4)</sup>                     | $C_{LOAD} = 4.7 \text{ nF}$                                   |      | 57    |      | ns     |

| t <sub>FLDRV</sub>    | Low-side driver fall time <sup>(4)</sup>                     | C <sub>LOAD</sub> = 4.7 nF                                    |      | 47    |      |        |

| LDRVSRPK              | Low-side driver peak source current <sup>(4)</sup>           |                                                               |      | 800   |      | mA     |

| LDRVSNMIL             | Low-side driver source current at 2.5 $V^{(4)}$              | V <sub>LDRV</sub> = 2.5 V                                     |      | 700   |      |        |

| ILSDVSNPK             | Low-side driver peak sink current <sup>(4)</sup>             |                                                               |      | 1.3   |      | А      |

|                       | Low-side driver sink current at 2.5 V <sup>(4)</sup>         | V <sub>LDRV</sub> = 2.5 V                                     |      | 1.2   |      |        |

| R <sub>LDRVUP</sub>   | Low-side driver pullup resistance                            | I <sub>LDRV</sub> = 300 mA                                    |      | 2.0   | 4.0  | Ω      |

| R <sub>LDRVDN</sub>   | Low-side driver pulldown resistance                          | I <sub>LDRV</sub> = 300 mA                                    |      | 0.8   | 1.5  |        |

| I <sub>SWLEAK</sub>   | Leakage current from SW pin                                  |                                                               | -1   |       | 1    | μΑ     |

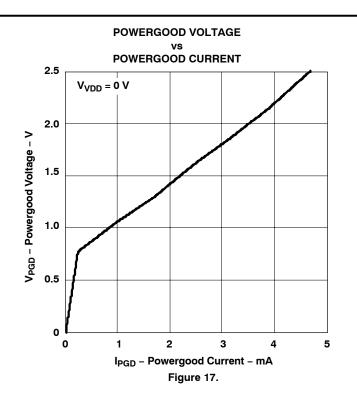

| POWERGO               | OD                                                           |                                                               | _    |       |      |        |

| V <sub>LPGD</sub>     | Powergood low voltage                                        | I <sub>PGD</sub> = 2 mA                                       |      | 30    | 100  | mV     |

| t <sub>PGD</sub>      | Powergood delay time                                         |                                                               | 15   | 25    | 35   | μs     |

| V <sub>LPGDNP</sub>   | Powergood low voltage , no device power                      | $V_{VDD}$ = OPEN, 10-k $\Omega$ pullup to external 5-V supply |      | 1.00  | 1.25 | V      |

| V <sub>OV</sub>       | Power good overvoltage threshold, $\mathrm{V}_{\mathrm{FB}}$ |                                                               |      | 765   |      | m\/    |

| V <sub>UV</sub>       | Power good undervoltage threshold, V <sub>FB</sub>           |                                                               |      | 615   |      | mV     |

Margining delay time is the time delay from an assertion of a margining command until the output voltage begins to transition to the (3) margined voltage. Ensured by design. Not production tested.

(4)

## ELECTRICAL CHARACTERISTICS (continued)

|                        | PARAMETER                                                | TEST CONDITIONS                                                                      | MIN   | TYP   | MAX   | UNIT |

|------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|------|

| TRACKING               | AMPLIFIER                                                |                                                                                      |       |       |       |      |

| V                      | Tracking amplifier input offset voltage                  | V <sub>TRKOS</sub> = V <sub>TRKIN</sub> - V <sub>O</sub> ; V <sub>VO</sub> ≤ 2 V     | 7     | 25    | 40    | mV   |

| V <sub>TRKOS</sub>     | Tracking amplifier input onset voltage                   | $V_{\text{TRKOS}} = V_{\text{TRKIN}} - V_{\text{O}}$ ; 2 V < $V_{\text{VO}} \le 6$ V | -5    | 25    | 40    | ШV   |

| V <sub>TRKCM</sub>     | Input common mode, active range                          |                                                                                      | 0     |       | 6     |      |

| V                      | Tracking amplifier voltage range                         | $4.5 \text{ V} \leq \text{V}_{\text{VDD}} \leq 5.5 \text{ V}$                        | 0     |       | 3.6   |      |

| V <sub>TRK</sub>       | Tracking amplifier voltage range                         | $5 \text{ V} < \text{V}_{\text{VDD}} \le 18 \text{ V}^{(5)}$                         | 0     |       | 6     | V    |

| V <sub>HTKBOUT</sub>   | High-level output voltage, TRKOUT                        | V <sub>VDD</sub> = 12 V                                                              | 5.0   | 6.5   | 8.0   | v    |

| ●HTKROUT               | Thigh-level output voltage, TAROOT                       | V <sub>VDD</sub> = 4.5 V                                                             | 3.2   | 3.6   |       |      |

| V <sub>LTKROUT</sub>   | Low-level output voltage, TRKOUT                         |                                                                                      | 0     |       | 0.5   |      |

| I <sub>SRCTRKOUT</sub> | Source current, TRKOUT                                   |                                                                                      | 0.65  | 2.00  |       | mA   |

| I <sub>SNKTRKOUT</sub> | Sink current, TRKOUT                                     |                                                                                      | 1     | 2     |       | ША   |

| V <sub>TRKDIF</sub>    | Differential voltage from TRKIN to VO                    |                                                                                      |       |       | 18    | V    |

| GBWP <sub>TRK</sub>    | Tracking amplifier gain bandwidth product <sup>(6)</sup> |                                                                                      | 1     |       |       | MHz  |

| AVOL <sub>TRK</sub>    | Tracking amplifier open loop DC gain <sup>(6)</sup>      |                                                                                      | 60    |       |       | dB   |

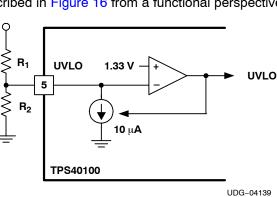

| PROGRAM                | MABLE UVLO                                               |                                                                                      |       |       |       |      |

| V <sub>UVLO</sub>      | Undervoltage lockout threshold                           |                                                                                      | 1.285 | 1.332 | 1.378 | V    |

| I <sub>UVLO</sub>      | Hysteresis current                                       |                                                                                      | 9.0   | 10.0  | 10.8  | μA   |

| INTERNALL              | Y FIXED UVLO                                             |                                                                                      |       |       |       |      |

| VUVLOFON               | Fixed UVLO turn-on voltage at VDD pin                    | -40°C ≤ T <sub>A</sub> < 125°C                                                       | 3.850 | 4.150 | 4.425 | V    |

| VUVLOFOFF              | Fixed UVLO turn-off voltage at VDD pin                   |                                                                                      | 3.75  | 4.06  | 4.35  | v    |

| VUVLOHYST              | UVLO hysteresis at VDD pin                               |                                                                                      |       | 85    |       | mV   |

| THERMAL S              | SHUTDOWN                                                 |                                                                                      |       |       |       |      |

| T <sub>SD</sub>        | Thermal shutdown temerature <sup>(6)</sup>               |                                                                                      | 130   | 165   |       | °C   |

| T <sub>SDHYST</sub>    | Hysteresis <sup>(6)</sup>                                |                                                                                      |       | 25    |       |      |

(5) Amplifier can track to the lesser of 6 V or  $(V_{DD} \times 0.95)$

(6) Ensured by design. Not production tested.

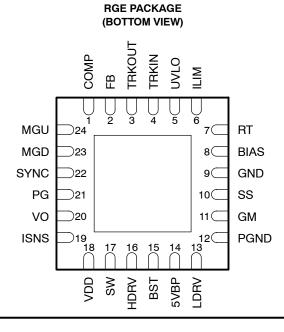

#### **DEVICE INFORMATION**

SLUS601-MAY 2005

# **DEVICE INFORMATION (continued)**

#### **TERMINAL FUNCTIONS**

TEXAS INSTRUMENTS www.ti.com

| TERMINAL |     | 1/0 | DECODIDION                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME     | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 5VBP     | 14  | 0   | Output of an internal 5-V regulator. A $1-\mu$ F bypass capacitor should be connected from this pin to PGND. Power for external circuitry may be drawn from this pin. The total gate drive current and external current draw should not cause the device to exceed thermal capabilities                                                                                                                                                  |  |  |  |  |  |

| BIAS     | 8   | 0   | The bypassed supply for internal device circuitry. Connect a $0.1-\mu$ F or greater ceramic capacitor from this pin to GND.                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| BST      | 15  | I   | Gate drive voltage for the high-side N-channel MOSFET. An external diode must be connected from 5VBP (A) to BST(K). A schottky diode is recommended for this purpose. A capacitor must be connected from this pin to the SW pin.                                                                                                                                                                                                         |  |  |  |  |  |

| COMP     | 1   | 0   | Output of the error amplifier. A feedback network is connected from this pin to the FB pin for control loop compensation.                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| FB       | 2   | I   | Inverting input to the error amplifier. In normal operation the voltage on this pin is equal to the internal reference voltage (approximately 690 mV).                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| GM       | 11  | I   | Connect a resistor from this pin to GND to set the gain of the current sense amplifier.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| GND      | 9   | -   | Low power or signal ground for the device. All <i>signal</i> level circuits should be referenced to this pin unless otherwise noted.                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| HDRV     | 16  | 0   | Floating gate drive for the high side N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| ILIM     | 6   | ο   | Current limit pin used to set the overcurrent threshold and transient ride out time. An internal current source that is proportional to the inductor current sets a voltage on a resistor connected from this pin to GND. When this voltage reaches 1.48 V, an overcurrent condition is declared by the device. Adding a capacitor in parallel with the resistor to GND sets a time delay that can be used to help avoid nuisance trips. |  |  |  |  |  |

| ISNS     | 19  | I   | Input from the inductor DCR sensing network. This input signal is one of the inputs to the current sense amplifier for current feedback control and overcurrent protection                                                                                                                                                                                                                                                               |  |  |  |  |  |

| LDRV     | 13  | 0   | Gate drive for the N-channel synchronous rectifier.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| MGD      | 23  | I   | Margin down pin used for load stress test. When this pin is pulled to GND through less than 10 k $\Omega$ , the output voltage is decreased by 5%. The 3% margin down at the output voltage is accommodated when this pin is connected to GND through a 30-k $\Omega$ resistor.                                                                                                                                                          |  |  |  |  |  |

| MGU      | 24  | I   | Margin up pin used for load stress test. When this pin is pulled to GND through less than 10 $k\Omega$ , the output voltage is increased by 5%. The 3% margin up at the output voltage is accommodated when this pin is connected to GND through a 30- $k\Omega$ resistor.                                                                                                                                                               |  |  |  |  |  |

| PG       | 21  | 0   | Open drain power good output for the device. This pin is pulled low when the voltage at the FB pin is more than 10% higher or lower than 690 mV, a UVLO condition exists, soft-start is active, tracking is active, an overcurrent condition exists or the die is over temperature.                                                                                                                                                      |  |  |  |  |  |

| PGND     | 12  | -   | Power ground for internal drivers                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| RT       | 7   | I   | A resistor connected from this pin to GND sets operating frequency.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| SS       | 10  | I   | Soft-start programming pin. A capacitor connected from this pin to ground programs the soft-start time. This pin is also used as a time out function during an overcurrent event.                                                                                                                                                                                                                                                        |  |  |  |  |  |

| sw       | 17  | I   | Connected to the switched node of the converter. This pin is the return line for the flying high side driver.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| SYNC     | 22  | I   | Rising edge triggered synchronization input for the device. This pin can be used to synchronize the oscillator frequency to an external master clock. This pin may be left floating or grounded if the function is not used.                                                                                                                                                                                                             |  |  |  |  |  |

| TRKIN    | 4   | I   | Control input allowing simultaneous startup of multiple controllers. The converter output tracks TRKIN voltage with a small controlled offset (typically 25 mV) when the tracking amplifier is used. See application section for more information.                                                                                                                                                                                       |  |  |  |  |  |

| TRKOUT   | 3   | 0   | Output of the tracking amplifier. If the tracking feature is used, this pin should be connected to FB pin through a resistor in series with a diode. The resistor value can be calculated from the equivalent impedance at the FB node. The diode should be a low leakage type to minimize errors due to diode reverse current. For further information on compensation of the tracking amplifier refer to the application information   |  |  |  |  |  |

| UVLO     | 5   | I   | Provides for programming the undervoltage lockout level and serves as a shutdown input for the device.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| VDD      | 18  | I   | Supply voltage for the device.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| VO       | 20  | I   | Output voltage. This is the reference input to the current sense amplifier for current mode control and overcurrent protection.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

SLUS601-MAY 2005

(1)

### **APPLICATION INFORMATION**

#### Introduction

The TPS40100 is a synchronous buck controller targeted at applications that require sequencing and output voltage margining features. This controller uses a current feedback mechanism to make loop compensation easier for loads that can have wide capacitance variations. Current sensing (for both current feedback and overcurrent) is true differential and can be done using the inductor DC resistance (with a R-C filter) or with a separate sense resistor in series with the inductor. The overcurrent level is programmable independently from the amount of current feedback providing greater application flexibility. Likewise, the overcurrent function has user programmable integration to eliminate nuisance tripping and allow the user to tailor the response to application requirements. The controller provides an integrated method to margin the output voltage to  $\pm$  3% and  $\pm$  5% of its nominal value by simply grounding one of two pins directly or through a resistance. Powergood and clock synchronization functions are provided on dedicated pins. Users can program operating frequency and the closed loop soft-start time by means of a resistor and capacitor to ground respectively. Output sequencing/tracking can be accomplished in one of three ways: sequential (one output comes up, then a second comes up), ratiometric (one or more outputs reach regulation at the same time — the voltages all follow a constant ration while starting) and simultaneous (one or more outputs track together on startup and reach regulation in order from lowest to highest).

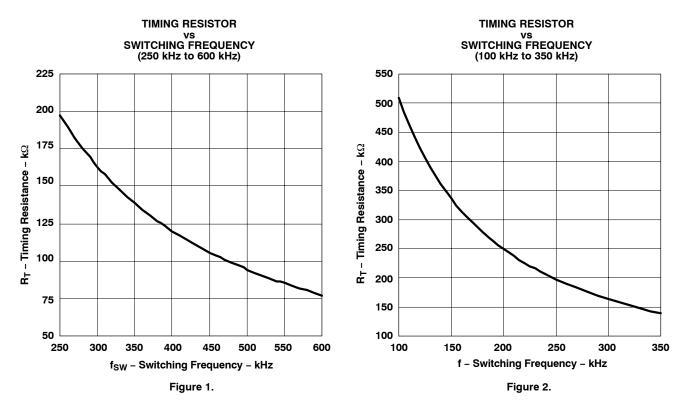

#### **Programming Operating Frequency**

Operating frequency is set by connecting a resistor to GND from the RT pin. The relationship is:

$$\mathsf{R}_{\mathsf{T}} = \left(\frac{-3.98 \times 10^4}{f_{\mathsf{SW}}^2}\right) + \left(\frac{5.14 \times 10^4}{f_{\mathsf{SW}}}\right) - 8.6 \; (\mathsf{k}\Omega)$$

where

• f<sub>SW</sub> is the switching frequency in kHz

•  $R_T$  is in  $k\Omega$

Figure 1 and Figure 2 show the relationship between the switching frequency and the  $R_T$  resistor as described in Equation 1. The scaling is different between them to allow the user a more accurate views at both high and low frequency.

#### **APPLICATION INFORMATION (continued)**

#### Selecting an Inductor Value

The inductor value determines the ripple current in the output capacitors and has an effect on the achievable transient response. A large inductance decreases ripple current and output voltage ripple, but is physically larger than a smaller inductance at the same current rating and limits output current slew rate more that a smaller inductance would. A lower inductance increases ripple current and output voltage ripple, but is physically smaller than a larger inductance at the same current rating. For most applications, a good compromise is selecting an inductance value that gives a ripple current between 20% and 30% of the full load current of the converter. The required inductance for a given ripple current can be found from:

$$L = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN} \times f_{SW} \times \Delta I} \quad (H)$$

where

- L is the inductance value (H)

- V<sub>IN</sub> is the input voltage to the converter (V)

- V<sub>OUT</sub> is the output voltage of the converter (V)

- f<sub>SW</sub> is the switching frequency chosen for the converter (Hz)

- $\Delta I$  is the peak-to-peak ripple current in the inductor (A)

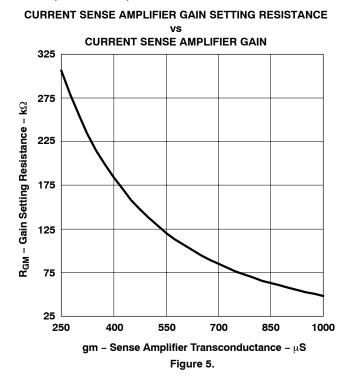

#### Selecting the Output Capacitance

The required value for the output capacitance depends on the output ripple voltage requirements and the ripple current in the inductor, as well as any load transient specifications that may exist.

The output voltage ripple depends directly on the ripple current and is affected by two parameters from the output capacitor: total capacitance and the capacitors equivalent series resistance (ESR). The output ripple voltage (worst case) can be found from:

(2)

Knowing the inductor ripple current, the switching frequency, the required load step and the allowable output voltage excursion allows calculation of the required output capacitance from a transient response perspective. The actual value and type of output capacitance is the one that satisfies both the ripple and transient specifications.

TPS40100

#### **APPLICATION INFORMATION (continued)**

$$\Delta V = \Delta I \times \left[ \text{ESR} + \left( \frac{1}{8 \times C_{\text{OUT}} \times f_{\text{SW}}} \right) \right] \quad (V)$$

where

- $\Delta V$  is the peak to peak output ripple voltage (V)

- $\Delta I$  is the peak-to-peak ripple current in the inductor (A)

- f<sub>SW</sub> is the switching frequency chosen for the converter (Hz)

- C<sub>OUT</sub> is the capacitance value of the output capacitor (F)

- ESR is the equivalent series resistance of the capacitor,  $C_{OUT}$  ( $\Omega$ )

For electrolytic capacitors, the output ripple voltage is almost entirely (90% or more) due to the ESR of the capacitor. When using ceramic output capacitors, the output ripple contribution from ESR is much smaller and the capacitance value itself becomes more significant. Paralleling output capacitors to achieve a desired output capacitance generally lowers the effective ESR more effectively than using a single larger capacitor. This increases performance at the expense of board area.

If there are load transient requirements that must be met, the overshoot and undershoot of the output voltage must be considered. If the load suddenly increases, the output voltage momentarily dips until the current in the inductor can ramp up to match the new load requirement. If the feedback loop is designed aggressively, this undershoot can be minimized. For a given undershoot specification, the required output capacitance can be found by:

$$C_{O(under)} = \frac{L \times I_{STEP}^{2}}{2 \times V_{UNDER} \times D_{MAX} \times (V_{IN} - V_{OUT})}$$

(F) (4)

where

- C<sub>O(under)</sub> is the output capacitance required to meet the undershoot specification (F)

- L is the inductor value (H)

- I<sub>STEP</sub> is the change in load current (A)

- V<sub>UNDER</sub> is the maximum allowable output voltage undershoot

- D<sub>MAX</sub> is the maximum duty cycle for the converter

- V<sub>IN</sub> is the input voltage

- V<sub>OUT</sub> is the output voltage

Similarly, if the load current suddenly goes from a high value to a low value, the output voltage overshoots. The ouput voltage rises until the current in the inductor drops to the new load current. The required capacitance for a given amount of overshoot can be found by:

$$C_{O(over)} = \frac{L \times I_{STEP}^{2}}{2 \times V_{OVER} \times V_{OUT}} \quad (F)$$

where

- C<sub>O(over)</sub> is the output capacitance required to meet the undershoot specification (F)

- L in the inductor value (H)

- I<sub>STEP</sub> is the change in load current (A)

- V<sub>OVER</sub> is the maximum allowable output voltage overshoot

- V<sub>OUT</sub> is the output voltage

(3)

(5)

#### **APPLICATION INFORMATION (continued)**

#### Calculating the Current Sense Filter Network

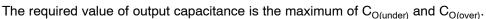

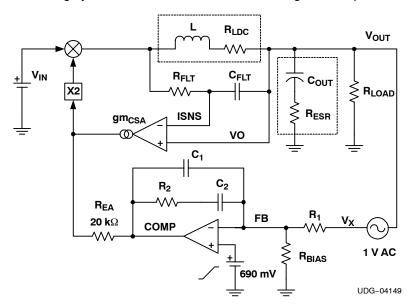

The TPS 40100 gets current feedback information by sensing the voltage across the inductor resistance, R<sub>LDC</sub>. In order to do this, a filter must be constructed that allows the sensed voltage to be representative of the actual current in the inductor. This filter is a series R-C network connected across the inductor as shown in Figure 3.

**Figure 3. Current Sensing Filter Circuit**

If the R<sub>FLT</sub>-C<sub>FLT</sub> time constant is matched to the L/R<sub>LDC</sub> time constant, the voltage across C<sub>FLT</sub> is equal to the voltage across R<sub>LDC</sub>. It is recommended to keep R<sub>FLT</sub> 10 kΩ or less. C<sub>FLT</sub> can be arbitrarily chosen to meet this condition (100 nF is suggested).  $R_{FIT}$  can then be calculated.

$$R_{FLT} = \frac{L}{R_{LDC} \times C_{FLT}} - 100 \quad (\Omega)$$

(6)

where

- $R_{FLT}$  is the current sense filter resistance ( $\Omega$ )

- $C_{FIT}$  is the current sense filter capacitance (F)

- L is the output inductance (H)

- $R_{LDC}$  is the DC resistance of the output inductor ( $\Omega$ )

When laying out the board, better performance can be accomplished by locating C<sub>FLT</sub> as close as possible to the VO and ISNS pins. The closer the two resistors can be brought to the device the better as this reduces the length of high impedance runs that are susceptible to noise pickup. The 100- $\Omega$  resistor from V<sub>OUT</sub> to the VO pin of the device is to limit current in the event that the output voltage dips below ground when a short is applied to the output of the converter.

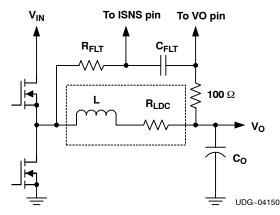

#### **Compensation for Inductor Resistance Change Over Temperature**

The resistance in the inductor that is sensed is the resistance of the copper winding. This value changes over temperature and has approximately a 4000 ppm/°C temperature coefficient. The gain of current sense amplifier in the TPS40100 has a built in temperature coefficient of approximately -2000 ppm/°C. If the circuit is physically arranged so that there is good thermal coupling between the inductor and the device, the thermal shifts tend to offset. If the thermal coupling is perfect, the net temperature coefficient is 2000 ppm/°C. If the coupling is not perfect, the net temperature coefficient lies between 2000 ppm/°C and 4000 ppm/°C. For most applications this is sufficient. If desired, the temperature drifts can be compensated for. The following compensation scheme assumes that the temperature rise at the device is directly proportional to the temperature rise at the inductor. If this is not the case, compensation accuracy suffers. Also, there is generally a time lag in the temperature rise at the device vs. at the inductor that could introduce transient errors beyond those predicted by the compensation.

Also, the 100- $\Omega$  resistor in Figure 3 is not shown. However, it is required if the output voltage can dip below ground during fault conditions. The calculations are not affected, other than increasing the effective value of R<sub>F1</sub> by 100-Ω.

#### **APPLICATION INFORMATION (continued)**

The relative resistance change in the inductor is given by:

$R_{REL(L)} = 1 + TC_{L} \times (T_{L} - T_{BASE})$  (dimensionless)

where

- R<sub>REL(L)</sub> is the relative resistance of the inductor at T<sub>L</sub> compared to the resistance at T<sub>BASE</sub>

- TC<sub>L</sub> is the temperature coefficient of copper, 4000 ppm/°C or 0.004

- T<sub>L</sub> is the inductor copper temperature (°C)

- T<sub>BASE</sub> is the reference temperature, typically lowest ambient (°C)

The relative gain of the current sense amplifier is given by a similar equation:

$$gm_{(REL)} = 1 + TC_{GM} \times (T_{IC} - T_{BASE})$$

(dimensionless)

where

- $gm_{REL}$  is the relative gain of the amplifier at  $T_{IC}$  compared to the gain at  $T_{BASE}$

- TC<sub>GM</sub> is the temperature coefficient of the amplifier gain, -2000 ppm/°C or -0.002

- T<sub>IC</sub> is the device junction temperature (°C)

- T<sub>BASE</sub> is the reference temperature, typically lowest ambient (°C)

The temperature rise of the device can usually be related to the temperature rise of the inductor. The relationship between the two temperature rises can be approximated as a linear relationship in most cases:

$$T_{IC} - T_{BASE} = (T_L - T_{BASE}) \times k_{THM}$$

where

- T<sub>IC</sub> is the device junction temperature (°C)

- T<sub>BASE</sub> is the reference temperature, typically lowest ambient (°C)

- T<sub>L</sub> is the inductor copper temperature (°C)

- k<sub>THM</sub> is the constant that relates device temperature rise to the inductor temperature rise and must be determined experimentally for any given design

With these assumptions, the effective inductor resistance over temperature is:

$$R_{\text{REL(eff)}} = R_{\text{REL(L)}} \times gm_{\text{REL}} = \left[1 + TC_{\text{L}}(T_{\text{L}} - T_{\text{BASE}})\right] \times \left[1 + k_{\text{THM}} \times TC_{\text{GM}} \times (T_{\text{L}} - T_{\text{BASE}})\right] \text{ (dimensionless)}$$

(10)

$R_{REL(eff)}$  is the relative effective resistance that must be compensated for when doing the compensation. The circuit of Figure 4 shows a method of compensating for thermal shifts in current limit. The NTC thermistor ( $R_{NTC}$ ) must be well coupled to the inductor.  $C_{FLT}$  should be located as close to the device as possible.

TEXAS

(8)

(7)

(9)

#### **APPLICATION INFORMATION (continued)**

Figure 4. Compensation for Temperature Coefficient of the Inductor Resistance

The first step is to determine an attenuation ratio  $\alpha$ . This ratio should be near to 1 but not too close. If it is too close to 1, the circuit requires large impedances and thermistor values too high. If  $\alpha$  is too low, the current signal is attenuated unnecessarily. A suggested value is 0.8.

$$\alpha \approx 0.8 \frac{R_{THE}}{R_{THE} + R_{F1}} \quad \text{(dimensionless)} \tag{11}$$

$R_{THE}$  is the equivalent resistance of the  $R_{F2}$ - $R_{F3}$ - $R_{NTC}$  network:

$$R_{\text{THE}} = R_{\text{F2}} + \frac{R_{\text{F3}} \times R_{\text{NTC}}}{R_{\text{F3}} + R_{\text{NTC}}} \quad (\Omega)$$

(12)

The base temperature ( $T_{BASE}$ ) should be selected to be the lowest temperature of interest for the thermal matching – the lowest ambient expected. The resistance of the inductor at this base temperature should be used to calculate effective resistance. The expected current sense amplifier gain at  $T_{BASE}$  should be used for calculating over current components ( $R_{ILIM}$ ).

The next step is to decide at what two temperatures the compensation is matched to the response of the deviceand inductor copper, T1 and T2. Once these are chosen, an NTC thermistor can be chosen and its value found from its data sheet at these two temperatures:  $R_{NTC(T1)}$  and  $R_{NTC(T2)}$ . The component values in the network can be calculated using the following equations:

#### **APPLICATION INFORMATION (continued)**

$$\begin{split} \mathsf{R}_{\mathsf{F1}} &= \frac{\mathsf{L}}{\mathsf{R}_{\mathsf{LDC}(\mathsf{Tbase}) \times \mathsf{C}_{\mathsf{FLT}} \times \alpha}} \quad (\Omega) \\ \mathsf{R}_{\mathsf{LDC}(\mathsf{T1})} &= \mathsf{R}_{\mathsf{LDC}(\mathsf{Tbase}) \times \mathsf{R}_{\mathsf{REL}(\mathsf{effT1})}} \quad (\Omega) \\ \mathsf{R}_{\mathsf{LDC}(\mathsf{T2})} &= \mathsf{R}_{\mathsf{LDC}(\mathsf{Tbase}) \times \mathsf{R}_{\mathsf{REL}(\mathsf{effT2})}} \quad (\Omega) \\ \mathsf{R}_{\mathsf{THE}(\mathsf{T1})} &= \frac{\alpha \times \mathsf{R}_{\mathsf{LDC}(\mathsf{Tbase}) \times \mathsf{R}_{\mathsf{F1}}}}{\mathsf{R}_{\mathsf{LDC}(\mathsf{T1})} - \alpha \times \mathsf{R}_{\mathsf{LDC}(\mathsf{Tbase})}} \quad (\Omega) \\ \mathsf{R}_{\mathsf{THE}(\mathsf{T2})} &= \frac{\alpha \times \mathsf{R}_{\mathsf{LDC}(\mathsf{Tbase}) \times \mathsf{R}_{\mathsf{F1}}}}{\mathsf{R}_{\mathsf{LDC}(\mathsf{T2})} - \alpha \times \mathsf{R}_{\mathsf{LDC}(\mathsf{Tbase})}} \quad (\Omega) \\ \mathsf{a} &= 1 - \frac{\mathsf{R}_{\mathsf{NTC}(\mathsf{T1})} - \mathsf{R}_{\mathsf{NTC}(\mathsf{T2})}}{\mathsf{R}_{\mathsf{THE}(\mathsf{T2})}} \quad (\mathsf{dimensionless}) \\ \mathsf{b} &= \mathsf{R}_{\mathsf{NTC}(\mathsf{T1})} + \mathsf{R}_{\mathsf{NTC}(\mathsf{T2})} \quad (\Omega) \\ \mathsf{c} &= \mathsf{R}_{\mathsf{NTC}(\mathsf{T1})} \times \mathsf{R}_{\mathsf{NTC}(\mathsf{T2})} \quad (\Omega^2) \\ \mathsf{c} &= \mathsf{R}_{\mathsf{NTC}(\mathsf{T1})} \times \mathsf{R}_{\mathsf{NTC}(\mathsf{T2})} \quad (\Omega^2) \\ \end{split}$$

$$R_{F3} = \frac{-b \pm \sqrt{b^2 - 4ac}}{2a} \quad (\Omega)$$

(21)

$$R_{F2} = \frac{R_{THE(T1)} \times (R_{F3} + R_{NTC(T1)}) - R_{F3} \times R_{NTC(T1)}}{R_{F3} + R_{NTC(T1)}} \quad (\Omega)$$

(22)

where

- L is the value of the output inductance (H)

- C<sub>FLT</sub> is the value of the current sense filter capacitor (F)

- $\alpha$  is the attenuation ratio chosen from Equation 11

- R<sub>THE(T1)</sub>, R<sub>THE(T2)</sub> are the equivalent resistances of the R<sub>THE</sub> network at temperatures T1 and T2

- R<sub>LDC(Tbase)</sub> is the DC resistance of the inductor at temperature T<sub>BASE</sub> in Ω

- R<sub>LDC(T1)</sub>, R<sub>LDC(T2)</sub> are the inductor resistances at temperatures T1 and T2

- R<sub>REL(effT1)</sub>, R<sub>REL(effT2)</sub>, are the relative resistances of the inductor at T1 and T2 vs. Tbase

- R<sub>NCT(T1)</sub>, R<sub>NTC(T2)</sub> are the effective resistance of the NTC thermistor at temperatures T1 and T2

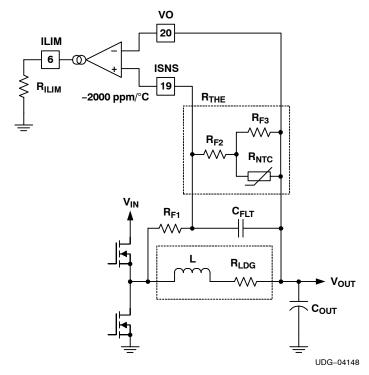

#### **Establishing Current Feedback**

The amount of current feedback in a given application is programmable by the user. The amount of current feedback used is intended to be just enough to reduce the Q of the output filter double pole. This allows design of a converter control loop that is stable for a very wide range of output capacitance. Setting the current feedback higher offers little real benefit and can actually degrade load transient response, as well as introduce pulse skipping in the converter. The current feedback is adjusted by setting the gain of the current sense amplifier. The amplifier is a transconductance type and its gain is a set by connecting a resistor from the GM pin to GND:

$$R_{GM} = \frac{3}{43.443 \times gm_{CSA}^2 + 0.01543 \times gm_{CSA} + 3.225 \times 10^{-6}} \quad (\Omega)$$

(23)

where

- $R_{GM}$  is the resistor that sets the gain of the amplifier ( $\Omega$ )

- $gm_{CSA}$  is the gain of the current sense amplifier (S)

The value of the sense amplifier gain should be less than 1000  $\mu$ S, and more than 250  $\mu$ S, with the resulting gain setting resistor greater than 50 k $\Omega$ . As a suggested starting point, set the gain of the current sense amplifier to a nominal 280  $\mu$ S with RGM of 279 k $\Omega$ . This value should accommodate most applications adequately. Figure 5 shows the current sense amplifier gain setting resistance vs. the sense amplifier gain.

#### **APPLICATION INFORMATION (continued)**

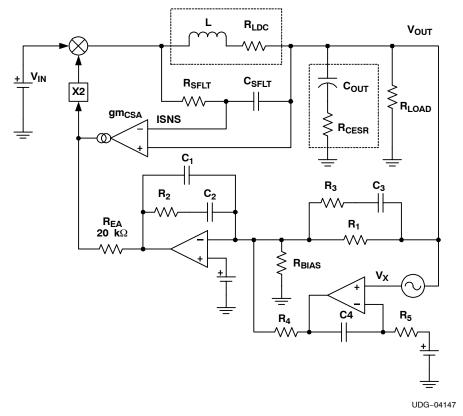

#### Control to Output Gain of the Converter

A model that gives a good first order approximation to the control to output gain of a converter based on the TPS40100 controller is shown in Figure 6. This model can be used in conjunction with a simulator to generate ac and transient response plots. The block labeled "X2" is a simple gain of 2. The amplifier gm can be a simple voltage controlled current source with a gain equal to the selected gm for the current sense amplifier (CSA).

Analytically, the control to output gain of this model (Figure 6) can be expressed as follows:

$$K_{CO}(s) = \frac{V_{IN} \times K_{PWM} \times K_{FILT}(s)}{1 + Y(s) \times K_{CS} \times K_{PWM} \times V_{IN}} \quad (dimensionless)$$

(24)

$K_{FILT}(s)$  is the output filter transfer function:

$K_{FILT}(s) =$

$$\frac{R_{LOAD}}{R_{LDC} + R_{LOAD}} \times \frac{R_{ESR} \times C_{OUT} \times s + 1}{\frac{L \times C_{OUT} + R_{LOAD}}{R_{LDC} + R_{LOAD}} \times s^{2} + \frac{L + C_{OUT} \times (R_{LOAD} \times R_{ESR} + R_{LDC} \times R_{LOAD} + R_{LDC} \times R_{ESR})}{R_{LOAD}} \times s + 1}$$

(25)

(dimensionless)

Usually,  $R_{LDC} \ll R_{LOAD}$  and the following approximation holds:

$$K_{\text{FILT}}(s) = \frac{R_{\text{ESR}} \times C_{\text{OUT}} \times s + 1}{L \times C_{\text{OUT}} \times s^{2} + \left[\frac{L + R_{\text{LOAD}} \times C_{\text{OUT}} \times (R_{\text{ESR}} + R_{\text{LDC}})}{R_{\text{LOAD}}}\right] \times s + 1}$$

(26)

Y(s) is the current signal transfer function and assumes that the inductor intrinsic time constant is matched to the current sense filter network time constant.

(27)

(28)

#### **APPLICATION INFORMATION (continued)**

$$Y(s) = \frac{1 - K_{FILT}(s)}{\frac{L}{R_{LDC}} \times s + 1}$$

(dimensionless)

K<sub>CS</sub> is the gain of the current sense amplifier in the current feedback loop:

${\rm K}_{\rm CS}$  =  ${\rm gm}_{\rm CSA}$   $\times$  20  ${\rm k}\Omega$   $\,$  (dimensionless)

where (for Equation 24 through Equation 28)

- V<sub>IN</sub> is the input voltage (V)

- K<sub>PWM</sub> is the gain of the pulse width modulator and is equal to 2

- $R_{LOAD}$  is the equivalent load resistance ( $\Omega$ )

- $R_{LDC}$  is the DC inductor resistance ( $\Omega$ )

- L is the output filter inductance (H)

- C<sub>OUT</sub> is the output filter capacitance (F)

- R<sub>ESR</sub> is the equivalent series resistance of the output filter capacitor (Ω)

- gm<sub>CSA</sub> is the gain of the current sense amplifier (S)

- 20 kΩ is the impedance the current sense amplifier works against (from block diagram)

A computer aided math tool is highly recommended for use in evaluating these equations.

Figure 6. Averaged Model for a Converter Based on the TPS40100

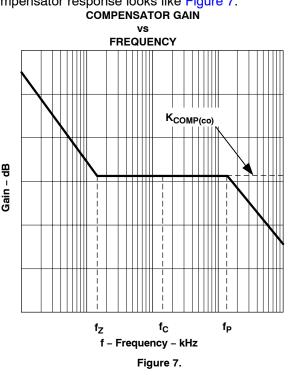

#### Compensating the Loop (Type II)

The first step is to select a target loop crossover frequency. Choosing the crossover frequency too high contributes to making the converter pulse skip. A balance of crossover frequency and amount of current feedback must be maintained to avoid pulse skipping. A suggested maximum loop crossover frequency is one fifth-of the switching frequency.

$$f_{C} \leq \frac{f_{SW}}{5}$$

(Hz)

where

- f<sub>C</sub> is the loop crossover frequency

- f<sub>sw</sub> is the switching frequency

(29)

## **APPLICATION INFORMATION (continued)**

Using either the analytical model or the simulated model, determine the control to output gain at the chosen loop crossover frequency. The gain of the compensator is the reciprocal of this gain:

$$K_{COMP(co)} = \frac{1}{|K_{CO}(fc)|}$$

(Hz)

$R_2 = K_{IF} \times R_1 \quad (\Omega)$

where

- K<sub>COMP(CO)</sub> is the required compensator gain at the crossover frequency

- K<sub>CO</sub>(f<sub>C</sub>) is the value of the control to output transfer function at the crossover frequency

If simulating the response using the model, the control to output gain is  $V_X/V_{OUT}$ . Sweep the AC voltage source over the range of interest and plot  $V_X/V_{OUT}$ .

Depending on the chosen loop crossover frequency and the characteristics of the output capacitor, either a Type II or a Type III compensator could be required. If the output capacitance has sufficient ESR, phase shift from the ESR zero may by used to eliminate the need for a Type III compensator. The model in Figure 6 uses a Type II compensator. In this case the compensator response looks like Figure 7.

First select  $R_1$ . The choice is somewhat arbitrary but affects the rest of the components once chosen. The suggested value is 10 k $\Omega$ .

$R_2$  is found from the gain required from the compensator at the crossover frequency.

(30)

TPS40100

SLUS601-MAY 2005

(31)

TEXAS INSTRUMENTS www.ti.com

#### **APPLICATION INFORMATION (continued)**

$$f_{P} = f_{C} \times 10 = \frac{1}{2 \pi \times R_{2} \times C_{1}} \quad (Hz)$$

$$f_{Z} = \frac{f_{C}}{10} = \frac{1}{2 \pi \times R_{2} \times C_{2}} \quad (Hz) \quad (33)$$

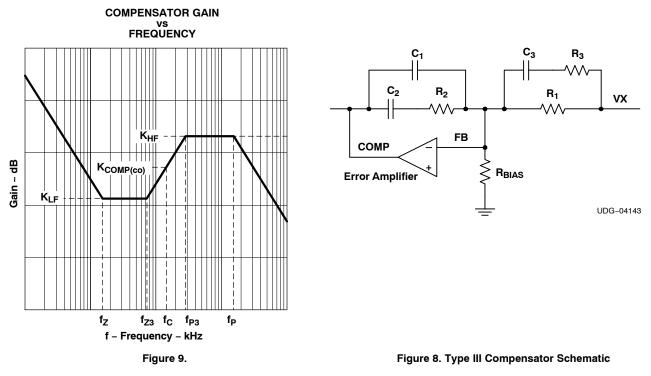

#### Compensating the Loop (Type III)

If the output capacitor does not have sufficient ESR to use the phase shift from the ESR zero, a Type III compensator is required. This is the case for most designs with ceramic output capacitors only. A series R-C circuit is added in parallel to  $R_1$  as shown in Figure 8.

This is the same compensator as in Figure 6 except for the addition of  $C_3$  and  $R_3$ . A typical response of this circuit is shown in Figure 9.

The reason for using the Type III compensator is to take advantage of the phase lead associated with the upward slope of the gain between  $f_{Z3}$  and  $f_{P3}$ . The crossover frequency should be located between these two frequencies. The amount of phase lead generated is dependent on the separation of the  $f_{Z3}$  and  $f_{P3}$ . In general, if  $f_{Z3}$  is one half of  $f_C$  and  $f_{P3}$  is twice  $f_C$ , the amount of phase lead at  $f_C$  generated is sufficient for most applications. Certainly more or less may be used depending on the situation.

As an example of selecting the extra required extra phase lead, suppose that the control to output gain phase evaluates to -145° at  $f_C$ . The Type II compensator has approximately 11.5° of phase lag at  $f_C$  due to the origin pole, the zero at  $f_C/10$  and the pole at  $10xf_C$ . This would give only 23.5° of phase margin, which while stable is not ideal. Placing  $f_{Z3}$  and  $f_{P3}$  at one half and twice the crossover frequency respectively adds approximately 36° of phase lead at  $f_C$  for a new phase margin of 59.5°.

To calculate the values for this type of compensator, first select R1. Again the choice is somewhat arbitrary. 10  $k\Omega$  is a suggested value.

APPLICATION INFORMATION (continued)

Select the required extra phase lead beyond the Type II compensation to obtain the required phase margin and calculate the required multiple for the additional pole and zero:

$$K_{3} = \tan(\Theta_{\text{LEAD}}) + \sqrt{\tan(\Theta_{\text{LEAD}}) + 1} \quad \text{(dimensionless)}$$

(34)

where

- $\Theta_{\text{LEAD}}$  is the required extra phase lead to be generated by the addition of the extra pole and zero

- K<sub>3</sub> is the multiplier applied to f<sub>C</sub> to get the new pole and zero locations

The locations of  $f_{Z3}$  and  $f_{P3}$  are:

$$f_{Z3} = \frac{f_C}{K_3} \quad (Hz)$$

$$f_{P3} = f_C \times K_3 \quad (Hz)$$

(35)

(36)

where

- K<sub>3</sub> is the multiplier applied to f<sub>C</sub> to get the new pole and zero locations

- $f_{Z3}$  is the zero created by the addition of  $R_3$  and  $C_3$

- $f_{P3}$  is the pole created by the addition of  $R_3$  and  $C_3$

The required gain,  $K_{COMP(co)}$ , from the compensator at  $f_C$ , is the same as for the Type II compensation, found in Equation 30. The gain  $K_{LF}$  (see Figure 9) is found by:

$$K_{LF} = \frac{K_{COMP(co)}}{K_3} \quad \text{(dimensionless)}$$

(37)

R<sub>2</sub> can then be found:

$$\mathsf{R}_2 = \mathsf{K}_{\mathsf{LF}} \times \mathsf{R}_1 \quad (\Omega) \tag{38}$$

The high-frequency gain is:

$$K_{HF} = K_{COMP(co)} \times K_3 \text{ (dimensionless)}$$

(39)

Now:

$$\mathsf{R}_3 = \frac{\mathsf{R}_1 \times \mathsf{R}_2}{\mathsf{K}_{\mathsf{HF}} \times \mathsf{R}_1 - \mathsf{R}_2} \quad (\Omega) \tag{40}$$

$$C_3 = \frac{1}{2\pi \times R_3 \times f_{P3}} \quad (F)$$

(41)

The remaining pole and zero are located a decade above and below  $f_C$  as before. Equation 31 and Equation 32 can be used to solve for  $C_1$  and  $C_2$  as before.

TPS40100

### **APPLICATION INFORMATION (continued)**

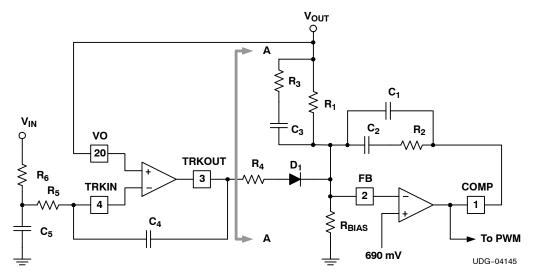

#### Establishing Tracking and Designing a Tracking Control Loop

The tracking startup feature of the TPS40100 is a separate control loop that controls the output voltage to a reference applied to the TRKIN pin. This reference voltage is typically a ramp generated by an external R-C circuit. Connecting the junction of R5, C5 and R6 (see Figure 10) of multiple converters together allows the converters output voltages to track together during start up. A controlled power down is accomplished by pulling down the common junction in a controlled manner and then removing power to the converters or turning them off by grounding the UVLO pin. The relevant circuit fragment is shown in Figure 10.

Figure 10. Tracking Loop Control Schematic

First, select a value for  $R_4$ . In order for this circuit to work properly, the output of the tracking amplifier must be able to cause the FB pin to reach at least 690 mV with the output voltage at zero volts. This is so that the output voltage can be forced to zero by the tracking amplifier. This places a maximum value on  $R_4$ :

$$R_{4} < \frac{\left[V_{HTRKOUT(min)} - V_{DIODE} - V_{FB}\right]}{V_{FB}} \times \frac{R_{1} \times R_{BIAS}}{R_{1} + R_{BIAS}} \Omega$$

(42)

where

- V<sub>HTRKOUT(min)</sub> is the minimum output voltage of the tracking amplifier (see Electrical Characteristics table)

- V<sub>DIODE</sub> is the forward voltage of the device selected for D<sub>1</sub>

- V<sub>FB</sub> is the value of the reference voltage (690 mV)

$R_4$  should not be chosen much lower than this value since that unnecessarily increases tracking loop gain, making compensation more difficult and opening the door to potential non-linear control issues. D1 could be a schottky if the impedance of the  $R_1$ - $R_{BIAS}$  string is low enough that the leakage current is not a consequence. Be aware that schottky diode leakage currents rise significantly at elevated temperature. If elevated temperature operation and increased accuracy are important, use a standard or low leakage junction diode or the base-emitter junction of a transistor for  $D_1$ .

Once  $R_4$  is selected, the gain of the closed loop power supply looking into "A" is known. That gain is the ratio of  $R_1$  and  $R_4$ :

$$\frac{dV_{OUT}}{dV_{TRKOUT}} = -\frac{R_1}{R_4}$$

(dimensionless)

(43)

The tracking loop itself should have a crossover frequency much less that the crossover frequency of the voltage control loop. Typically, the tracking loop crossover frequency is 1/10th or less of the voltage loop crossover frequency to avoid loop interactions. Note that the presence of the diode in the circuit gives a non-linear control mechanism for the tracking loop. The presence of this non-linearity makes designing a control loop more challenging. The simplest approach is to simply limit the bandwidth of this loop to no more than necessary.

APPLICATION INFORMATION (continued)

Knowing the gain of the voltage loop looking into R<sub>4</sub> and the desired tracking loop crossover frequency, R<sub>5</sub> and C<sub>4</sub> can be found:

$$R_5 \times C_4 = \frac{R_4}{2 \pi \times R_1 \times f_{cTRK}} \quad (s)$$

where

**IRUMENTS** www.ti.com

f<sub>CTBK</sub> is the desired tracking loop crossover frequency

The actual values of R<sub>5</sub> and C<sub>4</sub> are a balance between impedance level and component size. Any of a range of values is applicable. In general,  $R_5$  should be no more than 20% of  $R_6$ , and less than 10 k $\Omega$ . If this is done, then R<sub>6</sub> can safely be ignored for purposes of tracking loop gain calculations. For general usage, R<sub>6</sub> should probably be between 100 k $\Omega$  and 500 k $\Omega$ .

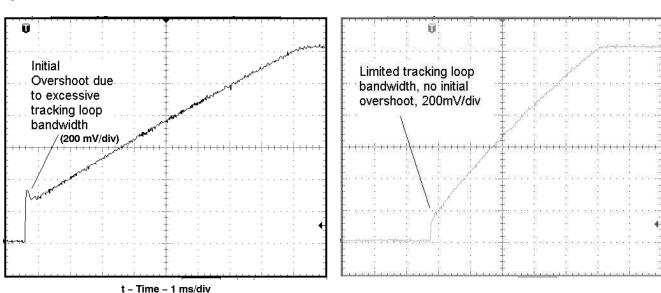

If an overshoot bump is present on the output at the beginning a tracking controlled startup, the tracking loop bandwidth is likely too high. Reducing the bandwidth helps reduce the initial overshoot. See Figure 11 and Figure 12.

Figure 11. Excessive Tracking Loop Bandwidth Figure 12. Limited Tracking Loop Bandwidth The tracking ramp time is the time required for C<sub>5</sub> to charge to the same voltage as the output voltage of the

converter.  $t_{TRK} = -R_6 \times C_5 \times ln \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$  (s)

where

V<sub>OUT</sub> is the output voltage of the converter

- V<sub>IN</sub> is the voltage applied to the top of R<sub>6</sub>

- $t_{\text{TRK}}$  is the desired tracking ramp time

With these equations, it is possible to design the tracking loop so that the impedance level of the loop and the component size are balanced for the particular application. Note that higher impedances make the loop more susceptible to noise issues while lower impedances require increased capacitor size.

Figure 13 shows the spice model for the voltage loop expanded for use with the tracking loop.

(45)

SLUS601-MAY 2005

4)

(46)

SLUS601-MAY 2005

#### **APPLICATION INFORMATION (continued)**

Figure 13. AC Behavioral Model for Tracking Control Loop

To use the model, the AC voltage source is swept over the frequency range of interest. The open loop ac response is  $V_X/V_{OUT}$ .

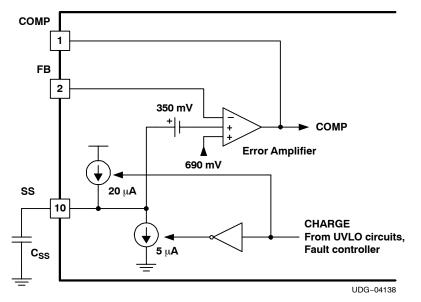

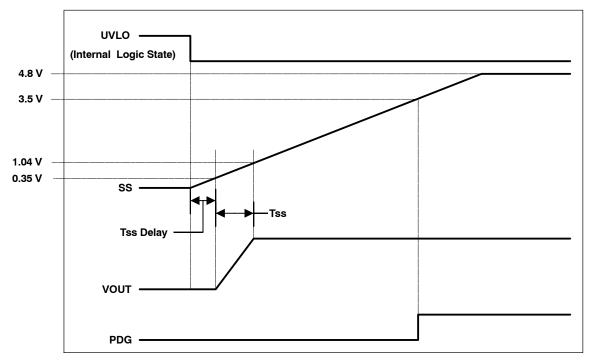

#### Programming Soft-Start Time