www.ti.com SLUS864 – MAY 2009

# SYNCHRONOUS BUCK CONTROLLER WITH HIGH-CURRENT GATE DRIVER

Check for Samples: TPS51113 TPS51163

#### **FEATURES**

Flexible Power Rails: 5 V to 12 V

Reference: 800 mV ± 0.8%

- Voltage Mode Control

- Support Pre-biased Startup

- Programmable Overcurrent Protection with Low-Side R<sub>DS(on)</sub> Current Sensing

- Fixed 300-kHz (TPS51113) and 600-kHz (TPS51163) Switching Frequency

- UV/OV Protections and Power Good Indicator

- Internal Soft-start

- Integrated High-Current Drivers Powered by VDD

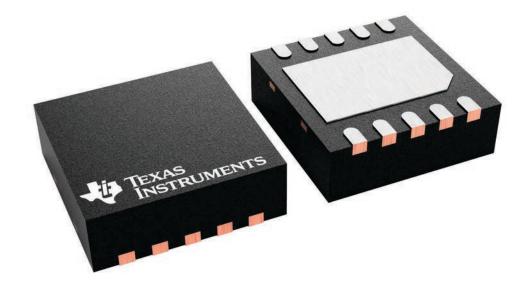

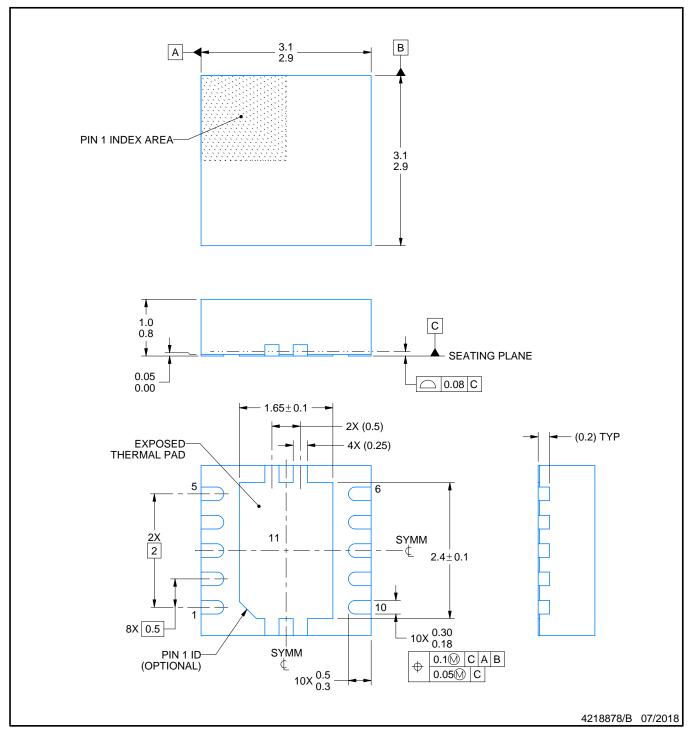

- 10-Pin 3 x 3 SON Package

#### **APPLICATIONS**

- Server and Desktop Computer Subsystem Power Supplies (MCH, IOCH, PCI, Termination)

- Distributed Power Supplies

- General DC-DC Converters

#### DESCRIPTION

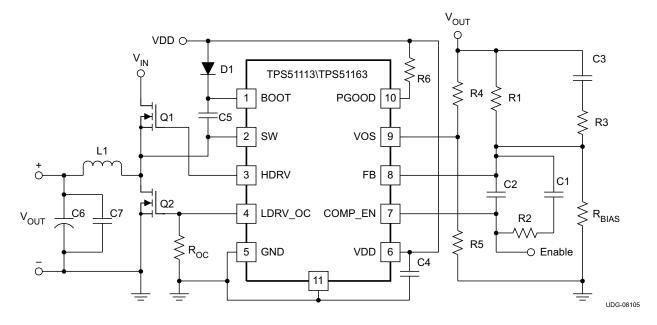

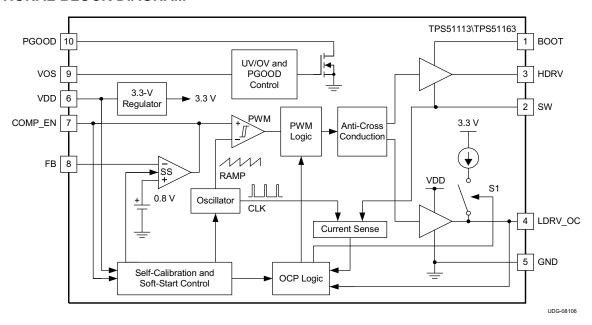

The TPS51113 and TPS51163 are cost-optimized, feature rich, single-channel synchronous-buck controllers that operates from a single 4.5-V to 13.2-V supply and can convert an input voltage as low as 1.5 V.

The controller implements voltage mode control with a fixed 300-kHz (TPS51113) and 600-kHz (TPS51163) switching frequency. The overcurrent (OC) protection employs the low-side  $R_{\text{DS(on)}}$  current sensing and has user-programmable threshold. The OC threshold is set by the resistor from LDRV\_OC pin to GND. The resistor value is read when the over-current programming circuit applies 10  $\mu\text{A}$  of current to the LDRV\_OC pin during the calibration phase of the start-up sequence.

The TPS51113/TPS51163 also supports output pre-biased startup.

The integrated gate driver is directly powered by VDD. VDD can be connected to  $V_{\text{IN}}$  in some applications. The strong gate drivers with low deadtime allow for the utilization of larger MOSFETs to achieve higher efficiency. An adaptive anti-cross conduction scheme is used to prevent shoot-through between the power FETs.

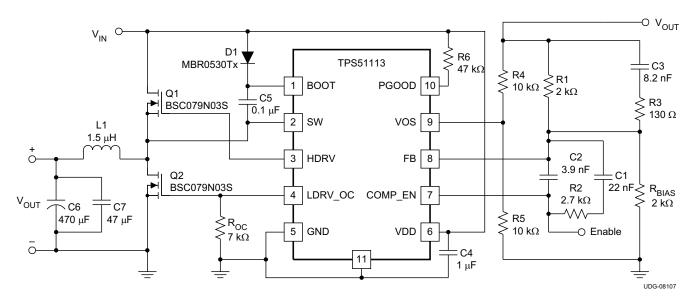

## TYPICAL APPLICATION CIRCUIT

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## Table 1. ORDERING INFORMATION<sup>(1)</sup>

| ORDERABLE<br>DEVICE | TYPE | DRAWING | PINS | QTY  | ECO PLAN            | LEAD/BALL<br>FINISH | MSL PEAK<br>TEMPERATURE |  |

|---------------------|------|---------|------|------|---------------------|---------------------|-------------------------|--|

| TPS51113DRCR        | SON  | DRC     | 10   | 3000 | Green               | CU NIPDAU           | Level-2-260C-1Year      |  |

| TPS51163DRCR        | 0011 | BRO     | 10   | 3000 | (RoHS and no Sb/Br) | OO WII DAO          | 2000 1 Todi             |  |

| TPS51113DRCT        | SON  | DRC     | 10   | 250  | Green               | CU NIPDAU           | Level-2-260C-1Year      |  |

| TPS51163DRCT        | SON  | DRC     | 10   | 250  | (RoHS and no Sb/Br) | CO NIPDAO           | Level-2-200C-1 Year     |  |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

# ABSOLUTE MAXIMUM RATINGS(1) (2)

Over operating free-air temperature range (unless otherwise noted, all voltages are with respect to GND.)

|                                   | PARAMETER                                                                                 | VALUE       | UNIT |

|-----------------------------------|-------------------------------------------------------------------------------------------|-------------|------|

|                                   | VDD                                                                                       | -0.3 to 15  |      |

|                                   | BOOT                                                                                      | -0.3 to 30  |      |

| Input voltage range               | BOOT, to SW (negative overshoot $-5$ V for t < 25 ns, 125 V × ns/t for 25 ns < t< 100 ns) | -5.0 to 15  | V    |

|                                   | BOOT, (negative overshoot –5 V for t < 25ns, 125 V x ns/t for 25 ns < t < 100 ns)         | -5.0 to 37  |      |

|                                   | All other pins                                                                            | -0.3 to 3.6 |      |

|                                   | SW                                                                                        | -0.3 to 22  |      |

|                                   | SW, (negative overshoot $-5$ V for t < 25ns, 125 V × ns/t for 25 ns < t < 100 ns)         | -5.0 to 30  |      |

|                                   | HDRV                                                                                      | -0.3 to 30  |      |

|                                   | HDRV to SW (negative overshoot –5 V for t < 25 ns, 125 V × ns/t for 25 ns < t< 100 ns)    | -5.0 to 15  |      |

| Output voltage range              | HDRV (negative overshoot $-5$ V for t < 25ns, 125 V × ns/t for 25 ns < t < 100 ns)        | -5.0 to 37  | V    |

|                                   | LDRV_OC                                                                                   | -0.3 to 15  |      |

|                                   | LDRV_OC (negative overshoot –5 V for t < 25ns, 125 V x ns/t for 25 ns < t < 100 ns)       | -5.0 to 15  |      |

|                                   | PGOOD                                                                                     | -0.3 to 15  |      |

|                                   | All other pins                                                                            | -0.3 to 3.6 |      |

| T <sub>J</sub> Operating junction | n temperature                                                                             | -40 to 125  | °C   |

| T <sub>stg</sub> Storage junction | temperature                                                                               | -55 to 150  |      |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

|                            | MIN | TYP | MAX  | UNIT |

|----------------------------|-----|-----|------|------|

| Human Body Model (HBM)     |     |     | 2500 | V    |

| Charged Device Model (CDM) |     |     | 1500 | V    |

Submit Documentation Feedback

<sup>(2)</sup> All voltage values are with respect to the network ground terminal unless otherwise noted.

www.ti.com

PACKAGE DISSIPATION RATINGS

| PACKAGE | AIRFLOW (LFM)          | R <sub>θJA</sub> HIGH-K BOARD <sup>(1)</sup><br>(°C/W) | POWER RATING (W)<br>T <sub>A</sub> = 25°C | POWER RATING (W)<br>T <sub>A</sub> = 85°C |

|---------|------------------------|--------------------------------------------------------|-------------------------------------------|-------------------------------------------|

|         | 0 (natural convection) | 47.9                                                   | 2.08                                      | 0.835                                     |

| DRC     | 200                    | 40.5                                                   | 2.46                                      | 0.987                                     |

|         | 400                    | 38.2                                                   | 2.61                                      | 1.04                                      |

<sup>(1)</sup> Ratings based on JEDEC High Thermal Conductivity (High K) Board. For more information on the test method, see TI Technical Brief (SZZA017).

## RECOMMENDED OPERATING CONDITIONS

(unless otherwise noted, all voltages are with respect to GND)

|                          |                                                                                         | MIN  | TYP MAX | UNIT |

|--------------------------|-----------------------------------------------------------------------------------------|------|---------|------|

|                          | VDD                                                                                     | -0.1 | 13.2    |      |

|                          | BOOT                                                                                    | -0.1 | 28.0    |      |

| Supply voltages          | BOOT, to SW (negative overshoot –5 V for t < 25 ns, 125 V × ns/t for 25 ns < t< 100 ns) | -3.0 | 13.2    | V    |

|                          | BOOT, (negative overshoot $-5$ V for t < 25 ns,<br>125 V × ns/t for 25 ns < t < 100 ns) | -3.0 | 35.0    |      |

|                          | All other pins                                                                          | -0.1 | 3.0     |      |

|                          | SW                                                                                      | -0.1 | 20.0    |      |

|                          | SW, (negative overshoot –5 V for t < 25 ns, 125 V × ns/t for 25 ns < t < 100 ns)        | -3.0 | 28.0    |      |

|                          | HDRV                                                                                    | -0.1 | 28.0    |      |

|                          | HDRV to SW (negative overshoot –5 V for t < 25 ns, 125 V × ns/t for 25 ns < t< 100 ns)  | -3.0 | 13.2    |      |

| Output voltages          | HDRV (negative overshoot –5 V for t < 25 ns, 125 V × ns/t for 25 ns < t < 100 ns)       | -3.0 | 35.0    | V    |

|                          | LDRV_OC                                                                                 | -0.1 | 13.2    |      |

|                          | LDRV_OC (negative overshoot –5 V for t < 25 ns, 125 V × ns/t for 25 ns < t < 100 ns)    | -3.0 | 13.2    |      |

|                          | PGOOD                                                                                   | -0.1 | 13.2    |      |

|                          | All other pins                                                                          | -0.1 | 3.0     |      |

| Γ <sub>A</sub> Operating | ambient temperature                                                                     | -40  | 85      | °C   |

## **ELECTRICAL CHARACTERISTICS**

These specifications apply for -40°C  $\leq$  T<sub>A</sub>  $\leq$  to 85°C, V<sub>VDD</sub> = 12 Vdc. (unless otherwise noted)

|                      | PARAMETER                                       |          | TEST CONDITIONS                                     | MIN  | TYP  | MAX  | UNIT |

|----------------------|-------------------------------------------------|----------|-----------------------------------------------------|------|------|------|------|

| INPUT SUP            | PPLY                                            |          |                                                     |      |      |      |      |

| $V_{VDD}$            |                                                 |          |                                                     | 4.5  |      | 13.2 | ٧    |

| $I_{VDD}$            | Supply current                                  |          | Switching enabled <sup>(1)</sup>                    |      |      | 30   | mA   |

|                      | Shutdown current                                |          | Switching inhibited                                 |      |      | 6    | mA   |

| VDD UVLO             | 1                                               |          |                                                     |      |      | '    |      |

| UVLO                 | VDD UVLO                                        |          | VDD raising                                         | 4.0  | 4.3  | 4.6  | V    |

| UVLO <sub>HYS</sub>  | UVLO threshold hysteresis                       |          |                                                     |      | 250  |      | mV   |

| REFERENC             | CE                                              |          |                                                     |      |      | ,    |      |

| V <sub>REF</sub>     | Reference voltage                               |          | 0°C ≤ T <sub>A</sub> ≤ 85°C                         | 794  | 800  | 806  | mV   |

|                      | Reference voltage                               |          | -40°C ≤ T <sub>A</sub> ≤ 85°C                       | 792  | 800  | 808  | mV   |

| OSCILLAT             | OR                                              |          |                                                     |      |      | · ·  |      |

| ,                    |                                                 |          | Measured on the SW pin,                             | 270  | 300  | 330  |      |

| $f_{SW}$             | Switching frequency                             | TPS51163 | T <sub>A</sub> = 25°C                               | 540  | 600  | 660  | kHz  |

| $V_{RAMP}$           | PWM ramp amplitude <sup>(1)</sup>               |          |                                                     |      | 1.5  |      | V    |

| PWM                  |                                                 |          |                                                     |      |      | · ·  |      |

| D                    | Manifestore distriction                         | TPS51113 |                                                     | 72%  |      |      |      |

| $D_{MAX}$            | Maximum duty cycle                              | TPS51163 |                                                     | 69%  |      |      |      |

| TON <sub>MIN</sub>   | Minimum controlled pulse <sup>(1)</sup>         |          |                                                     |      |      | 100  | ns   |

| T <sub>NO</sub>      | Output driver dead time                         |          |                                                     |      | 30   |      | ns   |

| SOFT STA             | RT                                              |          |                                                     |      |      | · ·  |      |

| T <sub>SSD</sub>     | Soft-start delay time                           |          |                                                     | 4.0  | 5.5  | 7.0  | ms   |

| T <sub>SS</sub>      | Soft-start time                                 |          |                                                     | 2.0  | 3.5  | 5.0  | ms   |

| ERROR AN             | <b>IPLIFIER</b>                                 |          |                                                     |      |      | ,    |      |

| GBWP                 | Gain bandwidth product <sup>(1)</sup>           |          | C <sub>COMP</sub> < 20 pF                           |      | 16   |      | MHz  |

| Aol                  | DC gain <sup>(1)</sup>                          |          |                                                     | 89   |      |      | dB   |

| I <sub>IB</sub>      | Input bias current                              |          |                                                     | -100 |      |      | nA   |

| EA <sub>SR</sub>     | Error amplifier output slew rate (1)            |          | C <sub>COMP</sub> < 20 pF                           | 6    |      |      | V/µs |

| V <sub>COMPDIS</sub> | COMP_EN pin disabling voltage                   |          |                                                     |      | 0.8  |      | V    |

| SHORT CIF            | RCUIT PROTECTION                                |          |                                                     |      |      |      |      |

| I <sub>ILIM</sub>    | Overcurrent threshold set current               |          |                                                     | 9.3  | 10.0 | 10.7 | μΑ   |

| GATE DRIV            | /ERS                                            |          |                                                     | •    |      | '    |      |

| I <sub>HDHI</sub>    | High-side driver pull-up current <sup>(1)</sup> |          | BOOT to HDRV voltage is 5 V                         |      | 1.5  |      | Α    |

| R <sub>HDLO</sub>    | High-side driver pull-down resistan             | ce       | $V_{VDD} = 12 \text{ V}; I_{DRV} = -100 \text{ mA}$ |      | 1.4  |      | Ω    |

| I <sub>LDHI</sub>    | Low-side driver pull-up current <sup>(1)</sup>  |          | VDD to LDRV voltage is 5 V                          |      | 1.5  |      | Α    |

| R <sub>LDLO</sub>    | Low-side driver pull-down resistant             | е        | V <sub>VDD</sub> = 12 V                             |      | 0.8  |      | Ω    |

<sup>(1)</sup> Ensured by design. Not production tested.

SLUS864 - MAY 2009

# **ELECTRICAL CHARACTERISTICS (continued)**

These specifications apply for -40°C  $\leq$  T<sub>A</sub>  $\leq$  to 85°C, V<sub>VDD</sub> = 12 Vdc. (unless otherwise noted)

|                    | PARAMETER                 | TEST CONDITIONS          | MIN   | TYP   | MAX   | UNIT |

|--------------------|---------------------------|--------------------------|-------|-------|-------|------|

| POWER G            | OOD                       |                          |       |       | ,     |      |

| $V_{PGLR}$         | Lower powergood threshold | VOS voltage rising       | 0.728 | 0.752 | 0.776 | V    |

| V <sub>PGLF</sub>  | Lower powergood threshold | VOS voltage falling      | 0.696 | 0.720 | 0.744 | V    |

| V <sub>PGUR</sub>  | Upper powergood threshold | VOS voltage rising       | 0.856 | 0.880 | 0.904 | V    |

| V <sub>PGUF</sub>  | Upper powergood threshold | VOS voltage falling      | 0.824 | 0.848 | 0.872 | V    |

| $V_{PG}$           | PGOOD pin voltage         | I <sub>PDG</sub> = 4 mA  |       |       | 0.4   | V    |

| I <sub>PGDLK</sub> | Leakage current           | V <sub>PGOOD</sub> = 5 V |       |       | 20    | μA   |

| UV/OV PR           | ROTECTION                 |                          |       |       |       |      |

| V <sub>UVP</sub>   | UVP threshold             | VOS voltage falling      | 0.576 | 0.600 | 0.624 | V    |

| V <sub>OVP</sub>   | OVP threshold             | VOS voltage rising       | 0.96  | 1.00  | 1.04  | V    |

| V <sub>OVPL</sub>  | OVP latch threshold       | VOS voltage falling      | 0.376 | 0.400 | 0.424 | V    |

| Ios                | VOS input bias current    |                          | -100  |       | 100   | nA   |

## **TERMINAL INFORMATION**

## **TERMINAL FUNCTIONS**

| TERMIN  | AL         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | PIN<br>NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| воот    | 1          | I   | Gate drive voltage for the high-side N-channel MOSFET. Typically, a 100 nF capacitor must be connected between this pin and SW. Also, a diode from VDD to BOOT should be externally provided.                                                                                                                                                                                                                                                                                                                        |

| COMP_EN | 7          | I/O | Output of the error amplifier and the shutdown pin. Pulling the voltage on this pin lower than 800 mV shuts the controller down.                                                                                                                                                                                                                                                                                                                                                                                     |

| FB      | 8          | I   | Inverting input to the error amplifier. In normal operation, the voltage on this pin is equal to the internal reference voltage of 800 mV.                                                                                                                                                                                                                                                                                                                                                                           |

| GND     | 5          | -   | Common reference for the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HDRV    | 3          | 0   | Gate drive output for the high-side N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LDRV_OC | 4          | 0   | Gate drive output for the low-side or rectifier MOSFET. The set point is read during start up calibration with the 10 µA current source present.                                                                                                                                                                                                                                                                                                                                                                     |

| PGOOD   | 10         | 0   | Open drain power good output. An external pull-up resistor is required.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SW      | 2          | 0   | Sense line for the adaptive anti-cross conduction circuitry. Serves as common connection for the flying high-side FET driver.                                                                                                                                                                                                                                                                                                                                                                                        |

| VDD     | 6          | I   | Power input to the controller, 4.5 V to 13.2 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| vos     | 9          | ı   | Input to set undervoltage and overvoltage protections. Undervoltage protection occurs when VOS voltage is lower than 600 mV. The controller shuts down with both MOSFETs latched off. Overvoltage protection occurs when VOS voltage is higher than 1V, the upper MOSFET is turned off and the lower MOSFET is forced on until VOS voltage reaches 400 mV. Then the lower MOSFET is also turned off. After the undervoltage or overvoltage events, normal operation can be restored only by cycling the VDD voltage. |

#### SON PACKAGE (TOP VIEW) воот (10 **PGOOD** sw vos **TPS51113DRC HDRV** 3 FΒ **TPS51163DRC** LDRV\_OC COMP\_EN GND 6 VDD 5

www.ti.com

## **FUNCTIONAL BLOCK DIAGRAM**

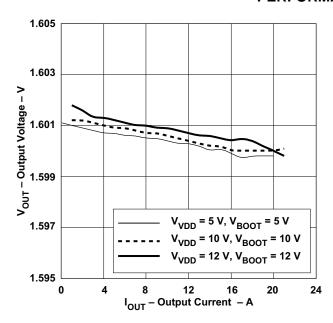

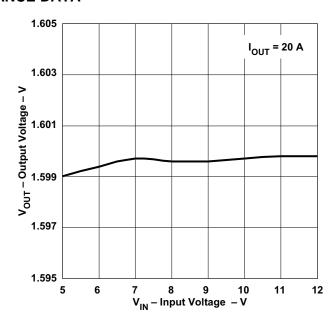

## **PERFORMANCE DATA**

Figure 1. Load Regulation

Figure 2. Line Regulation

SLUS864 – MAY 2009 www.ti.com

# TEXAS INSTRUMENTS

## **PERFORMANCE DATA (continued)**

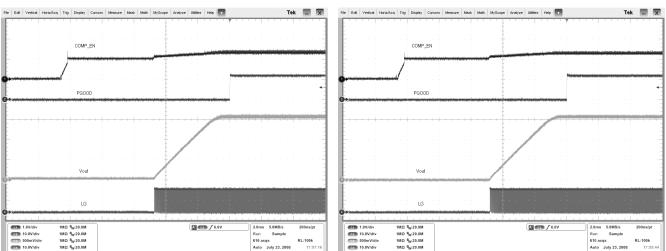

Figure 3. Startup Waveform at  $V_{IN}$  = 5 V,  $V_{OUT}$  = 1.6 V,  $I_{OUT}$  = 0 A

Figure 4. Startup Waveform at V<sub>IN</sub>= 12 V, V<sub>OUT</sub>= 1.6 V,  $I_{OUT}$ =0 A

CH1: COMP\_EN CH2: PGOOD CH3: VOUT

CH4: LDRV

CH1: COMP\_EN

CH2: PGOOD

CH3: VOUT

CH4: LDRV

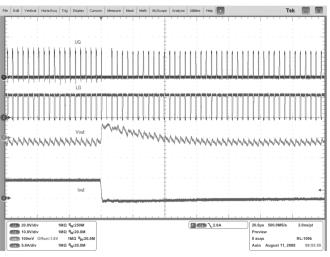

Figure 5. Load Step 0 A to 5 A

Figure 6. Load Step 5 A to 0 A

www.ti.com SLUS864 – MAY 2009

## **DETAILED DESCRIPTION**

TPS51113 and TPS51163 are cost-optimized, single channel synchronous buck controllers that operate at a 300-kHz (TPS51113) and 600-kHz (TPS51163) fixed switching frequency, from a single 4.5-V to 13.2-V supply, and supports output pre-biased startup. The overcurrent protection uses the low-side R<sub>DS(on)</sub> current sensing for a low-cost, loss-less solution. Other features include input undervoltage lockout (UVLO), programmable overcurrent threshold, soft-start, output oververvoltage/undervoltage (OV/UV) protection. The integrated gate driver is powered directly by VDD. This makes the gate drive voltage more flexible.

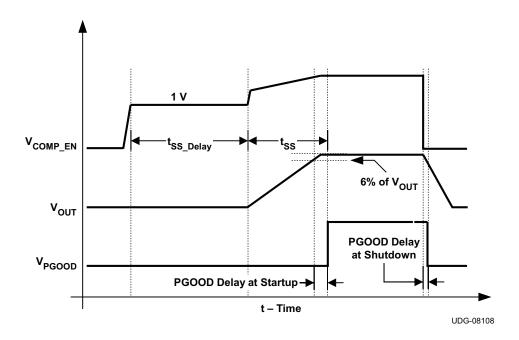

#### SOFT START AND SELF-CALIBRATION

When VDD is above 4.3 V and the COMP\_EN pin is released from being pulled low with open-drain system logic, the controller enters the start-up sequence. There is a two stage start-up sequence for the COMP\_EN voltage. In the first phase of start-up ( $t_{SS\_delay}$ ), the controller completes self-calibration and inhibits FET switching, leaving both the upper and lower MOSFETs in the off state. In the second phase of start-up ( $t_{SS}$ ), soft-start begins and switching is enabled. The internal reference gradually rises to 800 mV, and the output voltage gets within its regulation point. The soft-start time ( $t_{SS}$ ) is internally programmed at 3.5 ms, and  $t_{SS\_Delay}$  is programmed at 5.5 ms. On average, it takes approximately 9 ms for the output voltage to come into regulation after the COMP\_EN pin is released.

Figure 7 shows the typical startup and shutdown sequence. The overcurrent protection is enabled when the soft-start begins and the soft-start voltage exceeds the pre-biased VOS voltage. The output overvoltage protection is enabled approximately 64 clock cycles after the COMP pin voltage rises above 0.8 V (thereby enabling the device). When the soft-start ends, the output undervoltage protection is enabled, and PGOOD signal also goes high at the same time.

Figure 7. Typical Startup and Shutdown Sequence

# TEXAS INSTRUMENTS

#### **OVERCURRENT PROTECTION**

Overcurrent detection is done by comparing a user programmable threshold with the voltage drop across the low-side FET at the end of the switching period (The low-side FET is on). The OC threshold is set with a single external resistor connected from the LDRV\_OC pin to GND.

The overcurrent programming circuit applies 10-µA of current to the LDRV\_OC pin during the calibration phase of the start-up sequence. Voltage drop on the LDRV\_OC pin is measured and digitized, and the related code is stored in the internal latch. This code determines a reference level for the overcurrent comparator. The value of the OC set resistor R<sub>OCSET</sub> can be determined in Equation 1.

$$R_{OCSET} = \frac{R_{LDS(on)} \times \left(I_{OC} - \frac{I_{RIPPLE}}{2}\right)}{10 \,\mu\text{A}} \tag{1}$$

where

- R<sub>LDS(on)</sub> is the drain-to-source resistance of the lower MOSFET in the ON state

- I<sub>OC</sub> is the desired value of the overcurrent protection threshold for load current

- $\bullet$   $\;\;$   $I_{\text{RIPPLE}}$  is the peak-to-peak amplitude of the inductor ripple current

- the valley of the inductor current is compared with the overcurrent threshold for protection

When the controller senses the overcurrent condition for more than two clock cycles, both the upper and the lower MOSFETs are latched off. To restart the controller, the VDD input should be cycled.

If the overcurrent set resistor value is higher than 50 k $\Omega$ , for example, the voltage drop on the LDRV\_OC pin exceeds 0.5 V, the controller stays in the calibration state without entering soft-start. This prevents the controller from being activated if the overcurrent set resistor is missing.

## **OVERVOLTAGE (OV) AND UNDERVOLTAGE (UV) PROTECTION**

The controller employs the dedicated VOS input to set output undervoltage and overvoltage protections. A resistor divider with the same ratio as on the FB input is recommended for the VOS input. The overvoltage and undervoltage thresholds for VOS are set to  $\pm$  25% of the internal reference, which is 800 mV.

When the voltage on VOS is lower than 600 mV, the undervoltage protection is triggered. The controller is latched off with both the upper and lower MOSFETs turned off.

When the voltage on VOS is higher than 1 V, the overvoltage protection is activated. In the event of overvoltage, the upper MOSFET is turned off and the lower MOSFET is forced on until VOS voltage reaches 400 mV. Then the lower MOSFET is also turned off, and the controller is latched off.

After both the undervoltage and overvoltage events, normal operation can only be restored by cycling the VDD voltage.

#### **PGOOD**

The TPS51113 and TPS51163 have a power good output that indicates HIGH when the output voltage is within the target range. The PGOOD function is activated as soon as the soft-start ends. When the output voltage goes  $\pm$  10% outside of the target value, PGOOD goes low. When the output voltage returns to be within  $\pm$  6% of the target value, PGOOD signal goes HIGH again. The PGOOD output is an open drain and needs external pull up resistor.

Submit L

#### APPLICATION INFORMATION

#### **EXTERNAL PARTS SELECTION**

#### **CHOOSING THE INDUCTOR**

The value of the output filtering inductor determines the magnitude of the current ripple, which also affects the output voltage ripple for a certain output capacitance value. Increasing the inductance value reduces the ripple current, and thus, results in reduced conduction loss and output ripple voltage. On the other hand, low inductance value is needed due to the demand of low profile and fast transient response. Therefore, it is important to obtain a compromise between the low ripple current and low inductance value.

In practical application, to ensure high power conversion efficiency at light load condition, the peak-to-peak current ripple is usually designed to be between 1/4 to 1/2 of the rated load current. Since the magnitude of the current ripple is determined by inductance value, switching frequency, input voltage and output voltage, the required inductance value for a certain required ripple  $\Delta I$  is shown in Equation 2,

$$L = \frac{\left(V_{IN} - V_{OUT}\right) \times V_{OUT}}{V_{IN} \times I_{RIPPLE} \times f_{SW}}$$

(2)

where

- V<sub>IN</sub> is the input voltage

- V<sub>OUT</sub> is the output voltage

- IRIPPLE is the required current ripple

- f<sub>SW</sub> is the switching frequency

#### CALCULATING OUTPUT CAPACITANCE

When the inductance value is determined, the output capacitance value can also be derived according to the output ripple voltage and output load transient response requirement. The output ripple voltage is a function of both the output capacitance and capacitor ESR. Considering the worst case and assume the capacitance value is  $C_{OUT}$ , the peak-to-peak ripple voltage can be derived in Equation 3.

$$\Delta V = I_{RIPPLE} \times \left(ESR + \frac{1}{8 \times C_{OUT} \times f_{SW}}\right)$$

(3)

Thus, output capacitors with suitable ESR and capacitance value should be chosen to meet the ripple voltage  $(\Delta V)$  requirement.

Minimum capacitance value is also calculated according to the demand of the load transient response. When the load current changes, the energy that the inductor needs to release or absorb is derived in Equation 4.

$$\mathsf{E}_{\mathsf{L}} = \frac{1}{2} \times \mathsf{L} \times \left( \left( \mathsf{I}_{\mathsf{OH}} \right)^2 - \left( \mathsf{I}_{\mathsf{OL}} \right)^2 \right) \tag{4}$$

At the same time, the energy that is delivered to or provided by the output capacitor can also be derived as shown in Equation 5.

$$E_{C} = \frac{1}{2} \times C_{OUT} \times \left( \left( Vf \right)^{2} - \left( Vi \right)^{2} \right)$$

(5)

SLUS864 – MAY 2009 www.ti.com

As a result, to meet the load transient response demand, the minimum output capacitance should be

$$C_{OUT} = \frac{L \times \left( (I_{OH})^2 - (I_{OL})^2 \right)}{\left| (V_f)^2 - (V_i)^2 \right|}$$

(6)

where

- I<sub>OH</sub> is the output current under heavy load conditions

- I<sub>OL</sub> is the output current under light load conditions

- V<sub>f</sub> is the final peak capacitor voltage

- V<sub>i</sub> is the initial capacitor voltage

By considering the demand of both output ripple voltage and load transient response, the minimum output capacitance can be determined.

#### INPUT CAPACITOR SELECTION

For a certain rated load current, input and output voltage, the input ripple voltage caused by the input capacitance value and ESR are shown in Equation 7 and Equation 8, respectively.

$$V_{RIPPLE}(C_{IN}) = \frac{I_{OUT} \times V_{OUT}}{C_{IN(min)} \times V_{IN} \times f_{SW}}$$

(7)

$$V_{RIPPLE}(ESR_{C_{IN}}) = ESR_{C_{IN}} \times \left(I_{OUT} + \frac{1}{2} \times I_{RIPPLE}\right)$$

(8)

Based on the required input voltage ripple, suitable capacitors can be chosen by using the above equations.

#### **CHOOSING MOSFETS**

Choosing suitable MOSFETs is extremely important to achieve high power conversion efficiency for the converter. For a buck converter, suitable MOSFETs should not only meet the requirement of voltage and current rating, but also ensure low power loss. VDD can be connected to the 5-V rail when Ciclon FETs are used. But when less expensive FETs are used, direct gate drive facilitates the use of a higher drive voltage (such as  $V_{IN}$ ) to boost the efficiency.

#### High-Side MOSFET

Power loss of the high-side MOSFETs primarily consists of the conduction loss ( $P_{COND1}$ ) and the switching loss ( $P_{SW1}$ ).

The conduction loss of the high-side MOSFET is the  $I^2R$  loss in the MOSFET's on-resistance,  $R_{DS(on)1}$ . The RMS value of the current passing through the top MOSFET depends on the average load current, ripple current and duty cycle the converter is operating.

$$I_{RMS1} = \sqrt{D \times \left( \left( I_{OUT} \right)^2 + \frac{\left( I_{RIPPLE} \right)^2}{12} \right)}$$

(9)

The conduction loss can, thus, be calculated as follows.

$$P_{COND1} = (I_{RMS1})^2 \times R_{DS(ON)1}$$

(10)

2 Submit Documentation Feedback

Also, the switching loss can be approximately described as

$$P_{SW1} = V_{IN} \times \left( \left( \frac{I_{D1} \times I_{S1}}{6} \right) + \left( \frac{I_{D2} \times I_{S2}}{2} \right) \right) \times f_{SW}$$

(11)

where

I<sub>D1</sub> and I<sub>D2</sub> are the current magnitudes at the time instance when the MOSFETs switch

$$I_{D1} = I_{OUT} - \frac{1}{2} \times I_{RIPPLE}$$

and  $I_{D2} = I_{OUT} + \frac{1}{2} \times I_{RIPPLE}$  (12)

where

- t<sub>s1</sub> is the MOSFET switching-on time

- t<sub>s2</sub> is the MOSFET switching-off time

Therefore, the total power loss of the high-side MOSFET is estimated by the sum of the above power losses,

$$P_{HFET\_Loss} = P_{COND1} + P_{SW1}$$

(13)

### Synchronous Rectifier MOSFET Power Loss

Power loss associated with the synchronous rectifier (SR) MOSFET mainly consists of R<sub>DS(on)</sub> conduction loss, body diode conduction loss and reverse recovery loss.

Similarly to the high-side MOSFET, the conduction loss of the SR MOSFET is also the  $I^2R$  loss of the MOSFET's on-resistance,  $R_{DS(on)2}$ . Since the switching on-time of the SR MOSFET is (1-D)xT, where T is the duration of one switching cycle, the RMS current of the SR MOSFET can be calculated as follows.

$$I_{RMS2} = \sqrt{(1-D)\times\left(\left(I_{OUT}\right)^2 + \frac{\left(I_{RIPPLE}\right)^2}{12}\right)}$$

(14)

The symchronous rectifier (SR) MOSFET conduction loss is

$$P_{COND2} = (I_{RMS2})^2 \times R_{DS(ON)2}$$

(15)

The body diode conduction loss is

$$P_{COND3} = I_{OUT} \times V_F \times t_D \times f_{SW}$$

(16)

where

- V<sub>F</sub> is the forward voltage of the MOSFET body diode

- t<sub>D</sub> is the total conduction time of the body diode in one switching cycle

The body diode recovery time – the time it takes for the body diode to restore its blocking capability from forward conduction state, determines the reverse recovery losses.

$$P_{RR} = \frac{1}{2} \times Q_{RR} \times V_{IN} \times f_{SW}$$

(17)

where

Q<sub>RR</sub> is the reverse recovery charge of the body diode

Therefore, the total power loss of the SR MOSFET is estimated by the sum of the above power losses.

$$P_{SR\_Loss} = P_{COND2} + P_{COND3} + P_{RR}$$

(18)

SLUS864 – MAY 2009 www.ti.com

# Instruments

## **Feedback Loop Compensation**

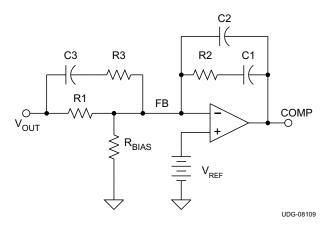

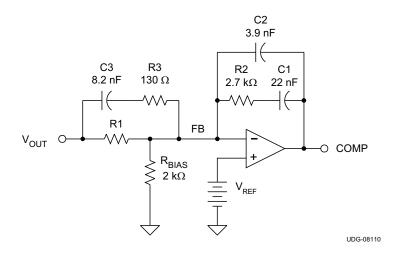

Since TPS51113/TPS51163 utilizes voltage-mode control for buck converters, Type III network is recommended for loop compensation. Suitable poles and zeros can be set by choosing proper parameters for the loop compensation network.

To calculate loop compensation parameters, the poles and zeros for the buck converter should be obtained. The double pole, determined by the L, and  $C_{OUT}$  of the buck converter, is located at the frequency as shown in the following equation.

$$f_0 = \frac{1}{2\pi \times \sqrt{L \times C_{OUT}}}$$

(19)

Also, the ESR zero of the buck converter can be achieved.

$$f_Z = \frac{1}{2\pi \times ESR \times C_{OUT}}$$

(20)

Figure 8 shows the configuration of Type III compensation. The transfer function of the compensator is described in Equation 21. Also, poles and zeros for the Type III network are shown in Equation 22 through Equation 26.

Figure 8. Type III Compensation Network

SLUS864-MAY 2009 www.ti.com

$$G(s) = \frac{(sR_2C_1 + 1) \times (s(R_1 + R_3)C_3 + 1)}{sR_1(C_1 + C_2) \times \left(s\left(\frac{R_2C_1C_2}{C_1 + C_2}\right) + 1\right) \times (sR_3C_3 + 1)}$$

(21)

$$f_{Z1} = \frac{1}{2\pi \times R_2 \times C_1} \tag{22}$$

$$f_{P1} = \frac{1}{2\pi \times R_2 \times \left(\frac{(C_1 \times C_2)}{(C_1 + C_2)}\right)}$$

(23)

$$f_{P2} = \frac{1}{2\pi \times R_3 \times C_3} \tag{24}$$

$$f_{Z2} = \frac{1}{2\pi \times (R_1 + R_3) \times C_3}$$

(25)

$$f_{C} = \frac{1}{2\pi \times R_{1} \times (C_{1} + C_{2})}$$

(26)

f<sub>P1</sub> is usually used to cancel the ESR zero in Equation 20. f<sub>P2</sub> can be placed at higher frequency in order to attenuate the high frequency noise and the switching ripple.  $f_{Z1}$  and  $f_{Z2}$  are chosen to be lower than the switching frequency, and  $f_{Z1}$  is lower than resonant frequency  $f_0$ . Suitable values can be selected to achieve the compromise between high phase margin and fast response. A phase margin of over 60° is usually recommended. Then, the compensator gain is chosen to achieve the desired bandwidth.

The value of R<sub>BIAS</sub> is calculated to set the output voltage V<sub>OUT</sub>.

$$R_{BIAS} = \frac{0.8 \times R_1}{V_{OUT} - 0.8} \tag{27}$$

## **Layout Considerations**

For the grounding and circuit layout, certain points need to be considered.

- It is important that the signal ground and power ground properly use separate copper planes to prevent the noise of power ground from influencing the signal ground. The impedance of each ground is minimized by using its copper plane. Sensitive nodes, such as the FB resistor divider and VOS resistor divider, should be connected to the signal ground plane, which is also connected with the GND pin of the device. The high power noisy circuits, such as synchronous rectifier, MOSFET driver decoupling capacitors, the input capacitors and the output capacitors should be connected to the power ground plane. Finally, the two separate ground planes should be strongly connected together near the device by using a single path/trace.

- A minimum of 0.1-μF ceramic capacitor must be placed as close to VDD pin and GND pin as possible with a

trace at least 20 mils wide, from the bypass capacitor to the GND. Usually a capacitance value of 1 μF is

recommended for the bypass capacitor.

- The PowerPAD should be electrically connected to GND.

- A parallel pair of trace (with at least 15 mils wide) connects the regulated voltage back to the chip. The trace should be away from the switching components. The bias resistor of the resistor divider should be connected to the FB pin and GND pin as close as possible.

- The component placement of the power stage should ensure minimized loop areas to suppress the radiated emissions. The input current loop is consisted of the input capacitors, the main switching MOSFET, the inductor, the output capacitors and the ground path back to the input capacitors. The SR MOSFET, the inductor, the output capacitors and the ground path back to the source of the SR MOSFET consists of the output current loop. The connection/trace should be as short as possible to reduce the parasitic inductance.

- Connections from the drivers to the respective gate of the high-side or the low-side MOSFET should be as short as possible to reduce stray inductance. A trace of 25 mils or wider is recommended.

- Connect the overcurrent setting resistor from LDRV OC to GND close to the device.

## **TPS51113 Design Example**

The following example illustrates the design process and component selection for a single output synchronous buck converter using the TPS51113. The schematic of a design example is shown in Figure 9. The specification of the converter is listed in Table 2.

Table 2. Specification of the Single Output Synchronous Buck Converter

|                     | PARAMETER           | TEST CONDITION          | MIN  | TYP                   | MAX  | UNIT |

|---------------------|---------------------|-------------------------|------|-----------------------|------|------|

| $V_{IN}$            | Input voltage       |                         | 10.8 | 12                    | 13.2 | V    |

| V <sub>OUT</sub>    | Output voltage      |                         |      | 1.6                   |      | V    |

| V <sub>RIPPLE</sub> | Output ripple       | I <sub>OUT</sub> = 10 A | 2%   | 6 of V <sub>OUT</sub> |      | V    |

| l <sub>OUT</sub>    | Output current      |                         |      | 10                    |      | V    |

| f <sub>SW</sub>     | Switching frequency |                         |      | 300                   |      | kHz  |

6 Submit Documentation Feedback

SLUS864-MAY 2009 www.ti.com

Figure 9. Design Example, 12 V to 1.6 V/10 A DC-DC Converter

## **Choosing the Inductor**

Typically the peak-to-peak inductor current ∆I is selected to be approximately between 20% and 40% of the rated output current. In this design, IRIPPLE is targeted at around 30% of the load current. Using Equation 2.

$$L = \frac{\left(V_{\text{IN}} - V_{\text{O}}\right) \times V_{\text{O}}}{V_{\text{IN}} \times I_{\text{RIPPLE}} \times f_{\text{SW}}} = 1.534 \,\mu\text{H}$$

(29)

Therefore, an inductor value of 1.5 µH is selected in practical, and the inductor ripple current is 3.08 A.

## **Calculating Output Capacitance**

Minimum capacitance value can be calculated according to the demand of the load transient response. Considering 0-A to 10-A step load and 10% overshoot and undershoot, the output capacitance value can be estimated by using Equation 6,

$$C_{OUT} = \frac{L \times \left( \left( I_{OH} \right)^2 - \left( I_{OL} \right)^2 \right)}{\left| \left( V_f \right)^2 - \left( V_i \right)^2 \right|} = 279 \,\mu\text{F}$$

(30)

A 470-μF POS-CAP with 18-mΩ ESR and a 47-μF ceramic capacitor are paralleled for the output capacitor.

#### **Input Capacitor Selection**

Considering 100 mV  $V_{RIPPLE(Cin)}$  and 50 mV  $V_{RIPPLE(ESR\_Cin)}$ , the input capacitance value and ESR value can be calculated according to Equation 7 and Equation 8, respectively.

$$C_{IN(min)} = \frac{I_{OUT} \times V_{OUT}}{V_{RIPPLE(C_{IN})} \times V_{IN} \times f_{SW}} = 44 \,\mu\text{F}$$

(31)

$$ESR_{C_{IN}} = \frac{V_{RIPPLE(ESR\_C_{IN})}}{\left(\frac{\left(I_{OUT} + I_{RIPPLE}\right)}{2}\right)} = 4.3 \text{ m}\Omega$$

(32)

Therefore, two 22-μF ceramic capacitors with 2-mΩ ESR can meet this requirement.

## **Choosing MOSFETS**

### **High-Side MOSFET Power Loss**

BSC079N03S is used for the high-side MOSFET. The on-resistance,  $R_{DS(on)1}$  is 7.9 m $\Omega$ . MOSFET switching-on time ( $t_{s1}$ ) and switching-off time ( $t_{s2}$ ) are approximately 9 ns and 24 ns, respectively. By using Equation 9 through Equation 13, the total power loss of the high-side MOSFET is estimated.

$$P_{HFET\_Loss} = P_{COND1} + P_{SW1} = (I_{RMS1})^{2} \times R_{DS(on)1} + V_{IN} \times \left(\frac{I_{D1} \times I_{S1}}{6} + \frac{I_{D2} \times I_{S2}}{2}\right) \times f_{SW} = 649 \text{ mW}$$

(33)

### **Synchronous Rectifier MOSFET Power Loss**

BSC032N03S is used for the synchronous rectifier MOSFET. The on-resistance,  $R_{DS(on)1}$  is 3.2 m $\Omega$ . The body diode has a 0.84-V diode forward voltage and 15-nC reverse recovery charge. The output driver deadtime is 30 ns. By using Equation 14 through Equation 18, the total power loss of the synchronous MOSFET is estimated,

$$P_{SR\_Loss} = P_{COND2} + P_{COND3} + P_{RR} = \left[I_{RMS2}\right]^2 \times R_{DS(on)2} + I_O \times V_F \times t_D \times f_{SW} + \frac{1}{2} \times Q_{RR} \times V_{IN} \times f_{SW} = 382 \text{mW}$$

$$(34)$$

#### **Feedback Loop Compensation**

Since TPS51113 and TPS51163 utilize voltage-mode control for buck converters, Type III network is recommended for loop compensation. The converter utilizes a 1.5- $\mu$ H inductor and 470- $\mu$ F capacitor with 18-m $\Omega$  ESR. The double pole, determined by the L, and C<sub>OUT</sub> of the buck converter, is derived by Equation 19

$$f_0 = \frac{1}{2\pi \times \sqrt{L \times C_{OUT}}} = 6.0 \,\text{kHz}$$

(35)

Also, the ESR zero of the buck converter can be achieved by using Equation 20.

$$f_Z = \frac{1}{2\pi \times ESR \times C_{OUT}} = 18.8 \, \text{kHz}$$

(36)

www.ti.com

Figure 10 shows the detailed parameters used for the Type III compensation. Also, poles and zeros for the Type III network are derived based on Equation 22 through Equation 26.

Figure 10. Parameters for Type III Compensation Network

$$G(s) = \frac{(sR_2C_1 + 1) \times (s(R_1 + R_3)C_3 + 1)}{sR_1(C_1 + C_2) \times \left(s\left(\frac{R_2C_1C_2}{C_1 + C_2}\right) + 1\right) \times (sR_3C_3 + 1)}$$

(37)

$$f_{Z1} = \frac{1}{2\pi \times R_2 \times C_1} = 2.7 \text{kHz}$$

(38)

$$f_{Z2} = \frac{1}{2\pi \times (R_1 + R_3) \times C_3} = 9.2 \text{kHz}$$

(39)

$$f_{P1} = \frac{1}{2\pi \times R_2 \times \left(\frac{(C_1 \times C_2)}{(C_1 + C_2)}\right)} = 17.8 \,\text{kHz}$$

(40)

$$f_{P2} = \frac{1}{2\pi \times R_3 \times C_3} = 149.4 \,\text{kHz} \tag{41}$$

$$f_C = \frac{1}{2\pi \times R_1 \times (C_1 + C_2)} = 3.1 \text{kHz}$$

(42)

$f_{P1}$  is used to cancel the ESR zero.  $f_{P2}$  is placed at higher frequency to attenuate the high-frequency noise and the switching ripple.  $f_{Z1}$  is lower than resonant frequency  $f_0$ .

The value of R<sub>BIAS</sub> is calculated to set the output voltage V <sub>OUT</sub> by using Equation 27.

$$R_{BIAS} = \frac{0.8 \times R_1}{V_O - 0.8} = 2k\Omega \tag{43}$$

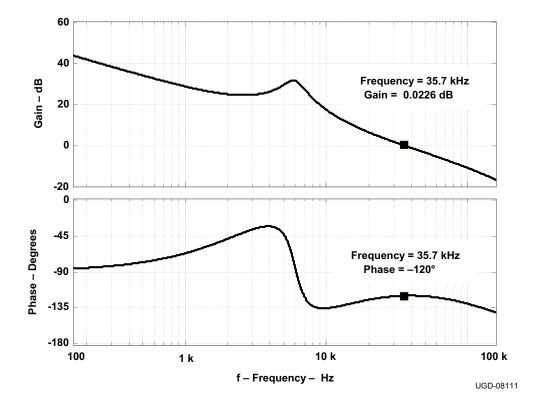

Based on Equation 43 and the power stage parameters, the bode-plot by simulation is shown in Figure 10 ( $V_{IN}$ =12 V and  $I_{OUT}$ =0 A). The achieved cross-over frequency is approximately 35.7 kHz, and the phase margin is approximately 60°.

Figure 11. Bode Plot of the Design Example Circuit by Simulation ( $V_{IN}$ =12 V and  $I_{OUT}$ =0 A)

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

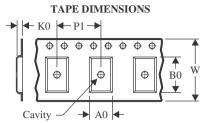

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

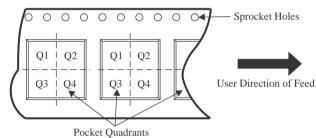

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS51113DRCR | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51113DRCT | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51163DRCR | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51163DRCT | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 3-Jun-2022

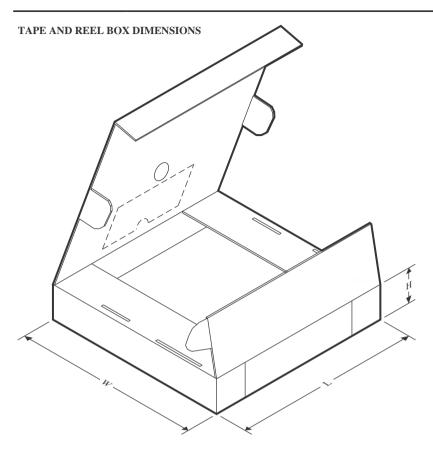

## \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS51113DRCR | VSON         | DRC             | 10   | 3000 | 356.0       | 356.0      | 35.0        |

| TPS51113DRCT | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS51163DRCR | VSON         | DRC             | 10   | 3000 | 356.0       | 356.0      | 35.0        |

| TPS51163DRCT | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

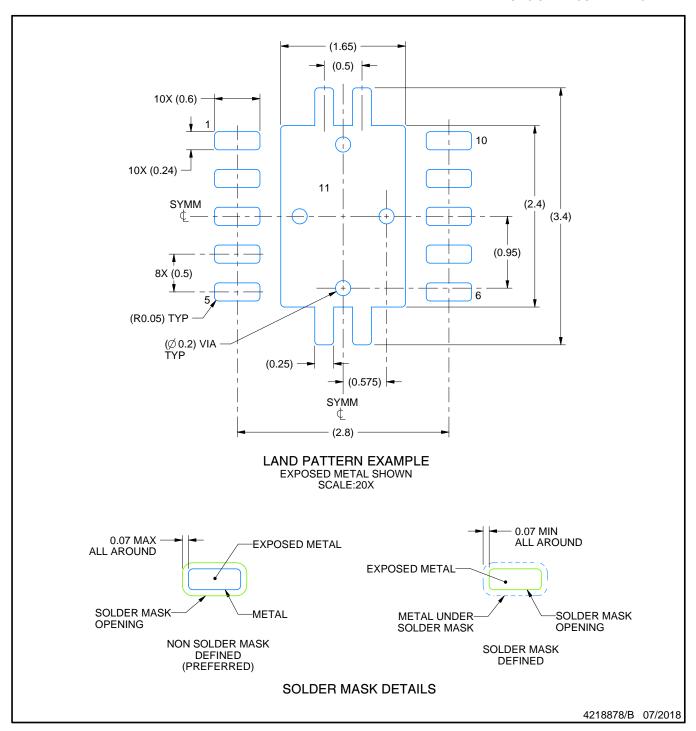

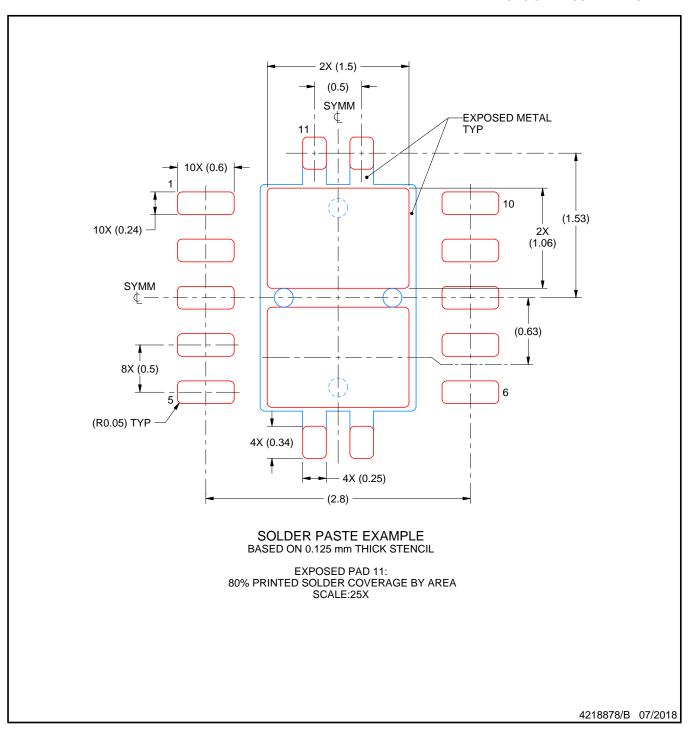

3 x 3, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

INSTRUMENTS www.ti.com

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated