### WIDEBAND, LOW-DISTORTION, FULLY DIFFERENTIAL AMPLIFIER

Check for Samples: THS4500-EP

#### **FEATURES**

- Fully Differential Architecture

- Bandwidth: 370 MHz

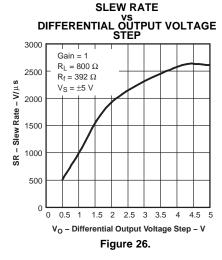

- Slew Rate: 2800 V/μs

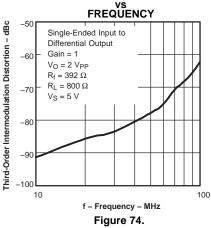

- IMD<sub>3</sub>: -90 dBc at 30 MHz

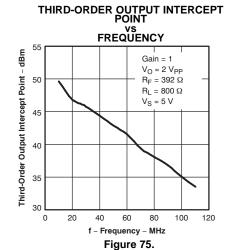

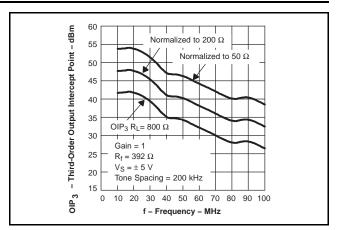

- OIP<sub>3</sub>: 49 dBm at 30 MHz

- Output Common-Mode Control

- Wide Power-Supply Voltage Range: 5 V, ±5 V, 12 V, 15 V

- Input Common-Mode Range Shifted to Include Negative Power-Supply Rail

- Power-Down Capability (THS4500)

- Evaluation Module Available

#### **APPLICATIONS**

- High Linearity Analog-to-Digital Converter Preamplifier

- Wireless Communication Receiver Chains

- Single-Ended to Differential Conversion

- Differential Line Driver

- Active Filtering of Differential Signals

### SUPPORTS DEFENSE, AEROSPACE, AND MEDICAL APPLICATIONS

- Controlled Baseline

- One Assembly and Test Site

- One Fabrication Site

- Available in Military (-55°C to 125°C)

Temperature Range

- Extended Product Life Cycle

- Extended Product-Change Notification

- Product Traceability

#### **RELATED DEVICES**

| DEVICE <sup>(1)</sup> | DESCRIPTION                                                  |

|-----------------------|--------------------------------------------------------------|

| THS4500/1             | 370 MHz, 2800 V/μs, V <sub>ICR</sub> Includes V <sub>S</sub> |

| THS4502/3             | 370 MHz, 2800 V/µs, Centered V <sub>ICR</sub>                |

| THS4120/1             | 3.3 V, 100 MHz, 43 V/µs, 3.7 nV/√Hz                          |

| THS4130/1             | ±15 V, 150 MHz, 51 V/µs, 1.3 nV/√Hz                          |

| THS4140/1             | ±15 V, 160 MHz, 450 V/µs, 6.5 nV/√Hz                         |

| THS4150/1             | ±15 V, 150 MHz, 650 V/µs, 7.6 nV/√Hz                         |

(1) Even-numbered devices feature power-down capability.

#### **DESCRIPTION**

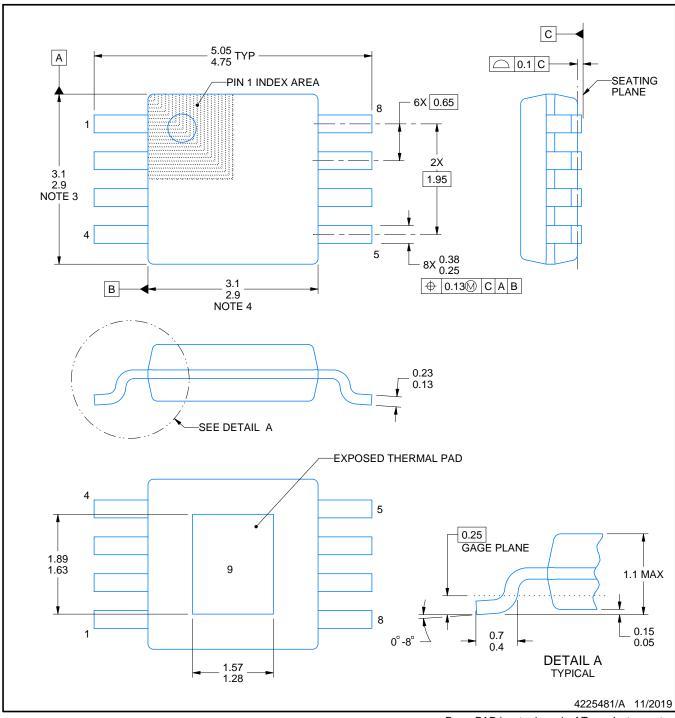

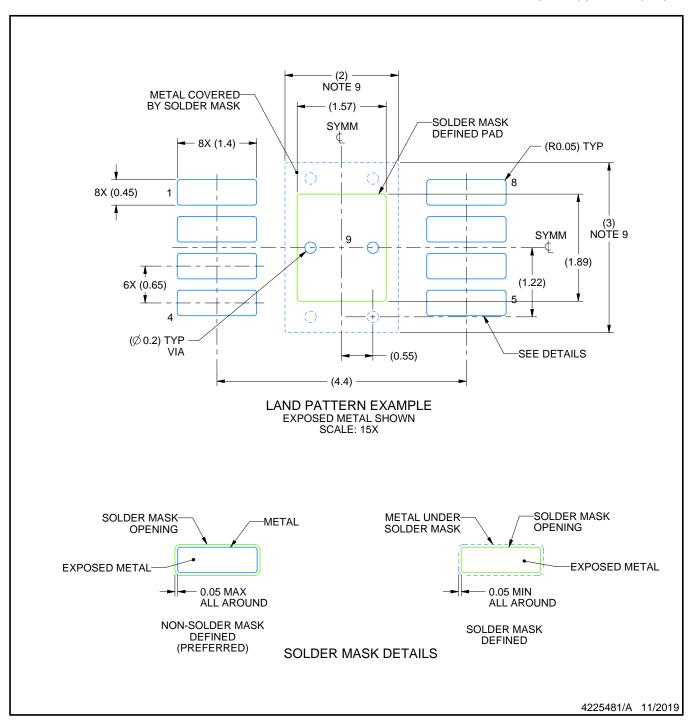

The THS4500 is a high-performance, fully differential amplifier from Texas Instruments. The THS4500, featuring power-down capability, sets new performance standards for fully differential amplifiers with unsurpassed linearity, supporting 14-bit operation through 40 MHz. Available in an MSOP-8 with PowerPAD™ package for a smaller footprint, enhanced ac performance, and improved thermal dissipation capability.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments, Incorporated. All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION<sup>(1)</sup>

| TJ             | PACKAGE        |              | PACKAGE ORDERABLE PART NUMBER |     | TOP-SIDE<br>MARKING | VID NUMBER |

|----------------|----------------|--------------|-------------------------------|-----|---------------------|------------|

| EE°C to 12E°C  | MSOP PowerPAD™ | Reel of 3000 | THS4500MDGNREP                | SJE | V62/13610-01XE      |            |

| -55°C to 125°C | (DGN)          | Tube of 80   | THS4500MDGNEP                 | SJE | V62/13610-01XE-T    |            |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at <a href="https://www.ti.com">www.ti.com</a>.

### **PIN ASSIGNMENTS**

Copyright © 2013, Texas Instruments Incorporated

#### ABSOLUTE MAXIMUM RATINGS(1)

Over operating free-air temperature range, unless otherwise noted.

|                                                              |        | UNIT            |

|--------------------------------------------------------------|--------|-----------------|

| Supply voltage, V <sub>S</sub>                               | 16.5 V |                 |

| Input voltage, V <sub>I</sub>                                |        | ±V <sub>S</sub> |

| Output current, I <sub>O</sub> <sup>(2)</sup>                |        | 150 mA          |

| Differential input voltage, V <sub>ID</sub>                  |        | 4 V             |

| Maximum junction temperature, T <sub>J</sub> <sup>(3)</sup>  |        | +150°C          |

| Storage temperature range, T <sub>stg</sub>                  |        | −65°C to +150°C |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |        | +300°C          |

|                                                              | НВМ    | 4000 V          |

| ESD rating:                                                  | CDM    | 1000 V          |

|                                                              | MM     | 100 V           |

- (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

- (2) The THS4500/1 may incorporate a PowerPAD on the underside of the chip. This acts as a heat sink and must be connected to a thermally dissipative plane for proper power dissipation. Failure to do so may result in exceeding the maximum junction temperature which could permanently damage the device. See TI technical briefs SLMA002 and SLMA004 for more information about utilizing the PowerPAD thermally-enhanced package.

- (3) The absolute maximum temperature under any condition is limited by the constraints of the silicon process.

#### THERMAL INFORMATION

|                  |                                                             | THS4500 |       |

|------------------|-------------------------------------------------------------|---------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | DGN     | UNITS |

|                  |                                                             | 8 PINS  |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 63.1    |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 46.2    |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (4)                    | 33.9    | 9C/M  |

| ΨЈТ              | Junction-to-top characterization parameter (5)              | 1.9     | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(6)</sup> | 33.6    |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance (7)            | 11.9    |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                                                |               | MIN | NOM        | MAX  | UNIT |

|------------------------------------------------|---------------|-----|------------|------|------|

| Supply valtage                                 | Dual supply   |     | <b>±</b> 5 | ±7.5 | \/   |

| Supply voltage                                 | Single supply | 5   |            | 15   | v    |

| Operating junction temperature, T <sub>J</sub> |               | -55 |            | 125  | °C   |

Product Folder Links: THS4500-EP

### ELECTRICAL CHARACTERISTICS: $V_s = \pm 5 V$

Applicable for  $-55^{\circ}\text{C} \le \text{T}_{\text{J}} \le +125^{\circ}\text{C}$ ,  $\text{R}_{\text{F}} = \text{R}_{\text{G}} = 392~\Omega$ ,  $\text{R}_{\text{L}} = 800~\Omega$ , G = +1, and single-ended input, unless otherwise noted.

| PARAMETER                                   | TEST CONDITIONS                                                                  | MIN   | TYP                  | MAX | UNITS              |

|---------------------------------------------|----------------------------------------------------------------------------------|-------|----------------------|-----|--------------------|

| AC PERFORMANCE                              |                                                                                  |       |                      |     |                    |

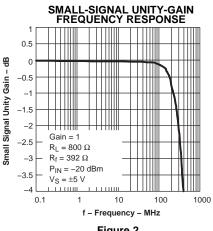

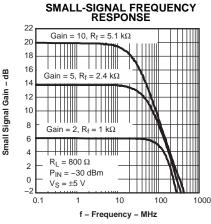

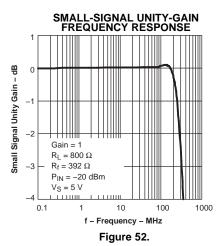

|                                             | $G = +1$ , $P_{IN} = -20$ dBm, $R_F = 392 \Omega$                                |       | 370                  |     | MHz                |

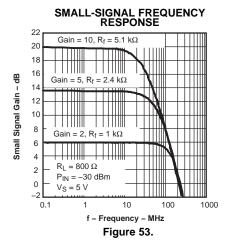

| 0 11 1 11 11 11                             | $G = +2$ , $P_{IN} = -30$ dBm, $R_F = 1$ kΩ                                      |       | 175                  |     | MHz                |

| Small-signal bandwidth                      | $G = +5$ , $P_{IN} = -30$ dBm, $R_F = 2.4 \text{ k}\Omega$                       |       | 70                   |     | MHz                |

|                                             | $G = +10, P_{IN} = -30 \text{ dBm}, R_F = 5.1 \text{ k}\Omega$                   |       | 30                   |     | MHz                |

| Gain-bandwidth product                      | G > +10                                                                          |       | 300                  |     | MHz                |

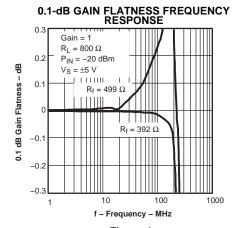

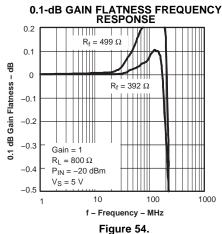

| Bandwidth for 0.1-dB flatness               | P <sub>IN</sub> = -20 dBm                                                        |       | 150                  |     | MHz                |

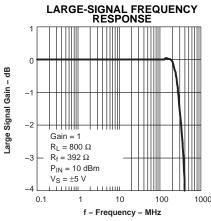

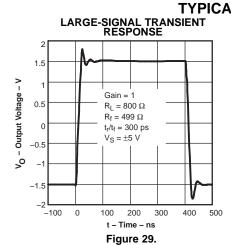

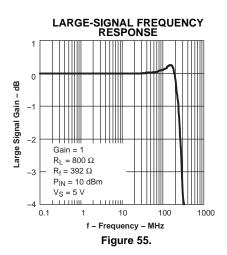

| Large-signal bandwidth                      | V <sub>P</sub> = 2 V                                                             |       | 220                  |     | MHz                |

| Slew rate                                   | 4 V <sub>PP</sub> Step                                                           |       | 2800                 |     | V/µs               |

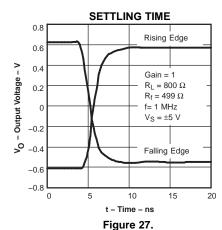

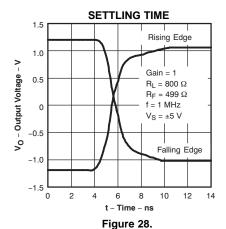

| Rise time                                   | 2 V <sub>PP</sub> Step                                                           |       | 0.4                  |     | ns                 |

| Fall time                                   | 2 V <sub>PP</sub> Step                                                           |       | 0.5                  |     | ns                 |

| Settling time to 0.01%                      | $V_O = 4 V_{PP}$                                                                 |       | 8.3                  |     | ns                 |

| 0.1%                                        | $V_O = 4 V_{PP}$                                                                 |       | 6.3                  |     | ns                 |

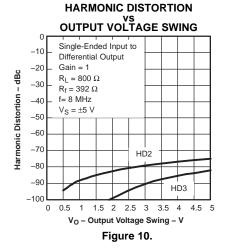

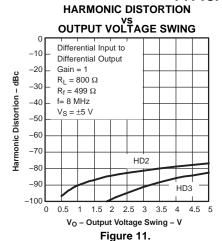

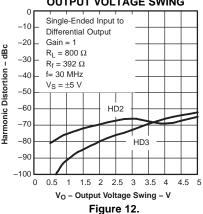

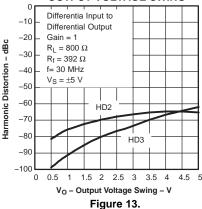

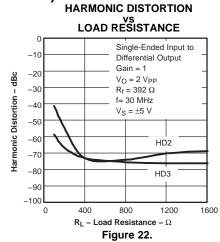

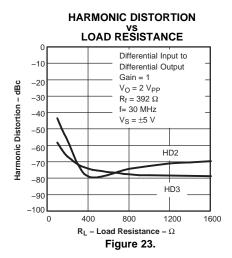

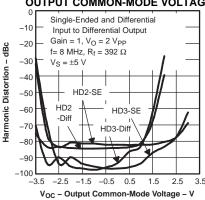

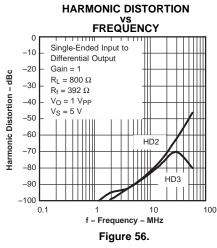

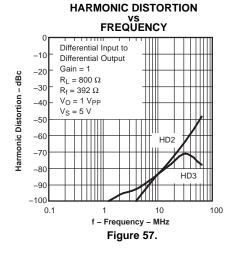

| Harmonic distortion                         | G = +1, V <sub>O</sub> = 2 V <sub>PP</sub>                                       |       |                      |     |                    |

|                                             | f = 8 MHz                                                                        |       | -82                  |     | dBc                |

| 2nd harmonic                                | f = 30 MHz                                                                       |       | -71                  |     | dBc                |

|                                             | f = 8 MHz                                                                        |       | -97                  |     | dBc                |

| 3rd harmonic                                | f = 30 MHz                                                                       |       | -74                  |     | dBc                |

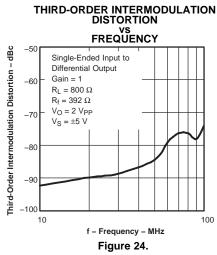

| Third-order intermodulation distortion      | $V_O$ = 2 $V_{PP}$ , $f_C$ = 30 MHz, $R_F$ = 392 $\Omega$ , 200 kHz tone spacing |       | -90                  |     | dBc                |

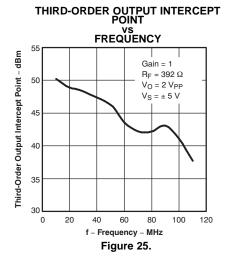

| Third-order output intercept point          | $f_C$ = 30 MHz, $R_F$ = 392 Ω,<br>Referenced to 50 Ω                             |       | 49                   |     | dBm                |

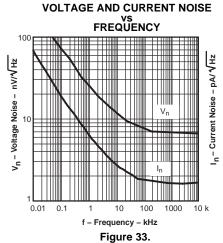

| Input voltage noise                         | f > 1 MHz                                                                        |       | 7                    |     | nV/√ <del>Hz</del> |

| Input current noise                         | f > 100 kHz                                                                      |       | 1.7                  |     | pA/√Hz             |

| Overdrive recovery time                     | Overdrive = 5.5 V                                                                |       | 60                   |     | ns                 |

| DC PERFORMANCE                              |                                                                                  |       | 1                    |     |                    |

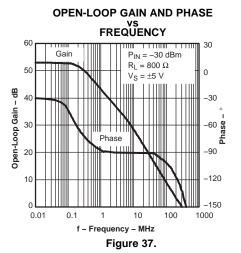

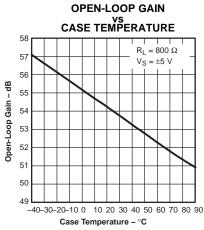

| Open-loop voltage gain                      |                                                                                  | 49    |                      |     | dB                 |

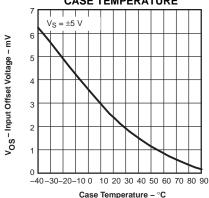

| Input offset voltage                        |                                                                                  | -11   |                      | 6   | mV                 |

| Average offset voltage drift                |                                                                                  |       | ±10                  |     | μV/°C              |

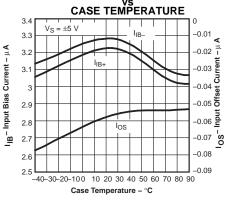

| Input bias current                          |                                                                                  |       |                      | 6.6 | μA                 |

| Average bias current drift                  |                                                                                  |       | ±10                  |     | nA/°C              |

| Input offset current                        |                                                                                  |       |                      | 2   | μA                 |

| Average offset current drift                |                                                                                  |       | ±40                  |     | nA/°C              |

| INPUT                                       |                                                                                  |       |                      |     | · ·                |

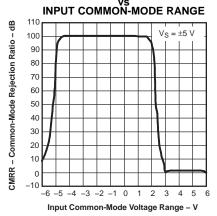

| Common-mode input range                     |                                                                                  | -5.1  |                      | 2   | V                  |

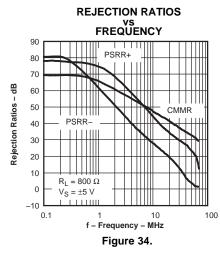

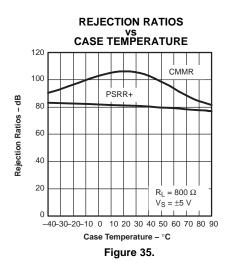

| Common-mode rejection ratio                 |                                                                                  | 70    |                      |     | dB                 |

| Input impedance                             |                                                                                  |       | 10 <sup>7</sup>    1 |     | Ω    pF            |

| OUTPUT                                      |                                                                                  |       |                      |     |                    |

| Differential output voltage swing           | $R_L = 1 k\Omega$                                                                | ±7.25 |                      |     | V                  |

| Differential output current drive           | R <sub>L</sub> = 20 Ω                                                            | 90    |                      |     | mA                 |

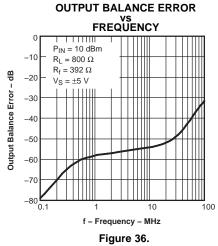

| Output balance error                        | P <sub>IN</sub> = -20 dBm, f = 100 kHz                                           |       | -58                  |     | dB                 |

| Closed-loop output impedance (single-ended) | f = 1 MHz                                                                        |       | 0.1                  |     | Ω                  |

Product Folder Links: THS4500-EP

### ELECTRICAL CHARACTERISTICS: $V_s = \pm 5 V$ (continued)

Applicable for  $-55^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq +125^{\circ}\text{C}, \ \text{R}_{\text{F}} = \text{R}_{\text{G}} = 392 \ \Omega, \ \text{R}_{\text{L}} = 800 \ \Omega, \ \text{G} = +1, \ \text{and single-ended input, unless otherwise noted.}$

| PARAMETER                      | TEST CONDITIONS                         | MIN   | TYP     | MAX  | UNITS    |

|--------------------------------|-----------------------------------------|-------|---------|------|----------|

| OUTPUT COMMON-MODE VOLTAGE     | CONTROL                                 |       |         |      | •        |

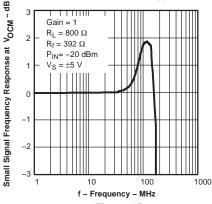

| Small-signal bandwidth         | R <sub>L</sub> = 400 Ω                  |       | 180     |      | MHz      |

| Slew rate                      | 2 V <sub>PP</sub> Step                  |       | 92      |      | V/µs     |

| Minimum gain                   |                                         | 0.98  |         |      | V/V      |

| Maximum gain                   |                                         |       |         | 1.08 | V/V      |

| Common-mode offset voltage     |                                         | -7.6  |         | 15   | mV       |

| Input bias current             | V <sub>OCM</sub> = 2.5 V                |       |         | 170  | μA       |

| Input voltage range            |                                         | ±3.4  |         |      | V        |

| Input impedance                |                                         |       | 25    1 |      | kΩ    pF |

| Maximum default voltage        | V <sub>OCM</sub> left floating          |       |         | 0.10 | V        |

| Minimum default voltage        | V <sub>OCM</sub> left floating          | -0.10 |         |      | V        |

| POWER SUPPLY                   | •                                       | •     | ,       |      | ·        |

| Specified operating voltage    |                                         |       |         | 7.5  | V        |

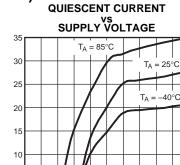

| Maximum quiescent current      |                                         |       |         | 40   | mA       |

| Minimum quiescent current      |                                         | 11    |         |      | mA       |

| Power-supply rejection (±PSRR) |                                         | 70    |         |      | dB       |

| POWER-DOWN                     |                                         |       |         |      | ·        |

| Enable voltage threshold       | Device enabled ON above -2.9 V          | -2.9  |         |      | V        |

| Disable voltage threshold      | Device disabled <i>OFF</i> below –4.3 V |       |         | -4.3 | V        |

| Power-down quiescent current   |                                         |       |         | 1400 | μA       |

| Input bias current             |                                         |       |         | 260  | μA       |

| Input impedance                |                                         |       | 50    1 |      | kΩ    pF |

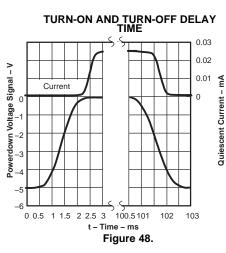

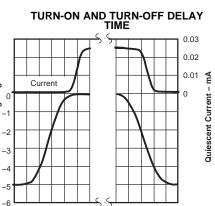

| Turn-on time delay             |                                         |       | 1000    |      | ns       |

| Turn-off time delay            |                                         |       | 800     |      | ns       |

### **ELECTRICAL CHARACTERISTICS:** V<sub>S</sub> = 5 V

Applicable for  $-55^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq +125^{\circ}\text{C}, \; \text{R}_{\text{F}} = \text{R}_{\text{G}} = 392 \; \Omega, \; \text{R}_{\text{L}} = 800 \; \Omega, \; \text{G} = +1, \; \text{and single-ended input, unless otherwise noted.}$

| PARAMETER                                   | TEST CONDITIONS                                       | MIN  | TYP                  | MAX | UNITS              |

|---------------------------------------------|-------------------------------------------------------|------|----------------------|-----|--------------------|

| AC PERFORMANCE                              |                                                       |      |                      |     |                    |

|                                             | $G = +1$ , $P_{IN} = -20$ dBm, $R_F = 392$ Ω          |      | 320                  |     | MHz                |

| Small-signal bandwidth                      | $G = +2$ , $P_{IN} = -30$ dBm, $R_F = 1$ kΩ           |      | 160                  |     | MHz                |

|                                             | $G = +5$ , $P_{IN} = -30$ dBm, $R_F = 2.4$ k $\Omega$ |      | 60                   |     | MHz                |

|                                             | $G = +10$ , $P_{IN} = -30$ dBm, $R_F = 5.1$ kΩ        |      | 30                   |     | MHz                |

| Gain-bandwidth product                      | G > +10                                               |      | 300                  |     | MHz                |

| Bandwidth for 0.1-dB flatness               | P <sub>IN</sub> = -20 dBm                             |      | 180                  |     | MHz                |

| Large-signal bandwidth                      | V <sub>P</sub> = 1 V                                  |      | 200                  |     | MHz                |

| Slew rate                                   | 2 V <sub>PP</sub> Step                                |      | 1300                 |     | V/µs               |

| Rise time                                   | 2 V <sub>PP</sub> Step                                |      | 0.5                  |     | ns                 |

| Fall time                                   | 2 V <sub>PP</sub> Step                                |      | 0.6                  |     | ns                 |

| Settling time to 0.01%                      | V <sub>O</sub> = 2 V Step                             |      | 13.1                 |     | ns                 |

| 0.1%                                        | V <sub>O</sub> = 2 V Step                             |      | 8.3                  |     | ns                 |

| Harmonic distortion                         | $G = +1, V_O = 2 V_{PP}$                              |      |                      |     |                    |

|                                             | f = 8 MHz,                                            |      | -80                  |     | dBc                |

| 2nd harmonic                                | f = 30 MHz                                            |      | -55                  |     | dBc                |

|                                             | f = 8 MHz                                             |      | -76                  |     | dBc                |

| 3rd harmonic                                | f = 30 MHz                                            |      | -60                  |     | dBc                |

| Input voltage noise                         | f > 1 MHz                                             |      | 7                    |     | nV/√ <del>Hz</del> |

| Input current noise                         | f > 100 kHz                                           |      | 1.7                  |     | pA/√ <del>Hz</del> |

| Overdrive recovery time                     | Overdrive = 5.5 V                                     |      | 60                   |     | ns                 |

| DC PERFORMANCE                              |                                                       | !    | -                    |     |                    |

| Open-loop voltage gain                      |                                                       | 48   |                      |     | dB                 |

| Input offset voltage                        |                                                       | -11  |                      | 6   | mV                 |

| Average offset voltage drift                |                                                       |      | ±10                  |     | μV/°C              |

| Input bias current                          |                                                       |      |                      | 8   | μA                 |

| Average bias current drift                  |                                                       |      | ±10                  |     | nA/°C              |

| Input offset current                        |                                                       |      |                      | 2   | μA                 |

| Average offset current drift                |                                                       |      | ±20                  |     | nA/°C              |

| INPUT                                       |                                                       | -1   | 1                    |     |                    |

| Common-mode input range                     |                                                       | -0.1 |                      | 2   | V                  |

| Common-mode rejection ratio                 |                                                       | 65   |                      |     | dB                 |

| Input Impedance                             |                                                       |      | 10 <sup>7</sup>    1 |     | Ω    pF            |

| OUTPUT                                      |                                                       | 1    |                      |     |                    |

| Differential output voltage swing           | $R_L = 1 \text{ k}\Omega$ , Referenced to 2.5 V       | ±2.7 |                      |     | V                  |

| Output current drive                        | $R_L = 20 \Omega$                                     | 80   |                      |     | mA                 |

| Output balance error                        | P <sub>IN</sub> = -20 dBm, f = 100 kHz                |      | -58                  |     | dB                 |

| Closed-loop output impedance (single-ended) | f = 1 MHz                                             |      | 0.1                  |     | Ω                  |

Product Folder Links: THS4500-EP

### **ELECTRICAL CHARACTERISTICS:** V<sub>S</sub> = 5 V (continued)

Applicable for  $-55^{\circ}\text{C} \le \text{T}_{\text{J}} \le +125^{\circ}\text{C}$ ,  $\text{R}_{\text{F}} = \text{R}_{\text{G}} = 392~\Omega$ ,  $\text{R}_{\text{L}} = 800~\Omega$ , G = +1, and single-ended input, unless otherwise noted.

| PARAMETER                      | TEST CONDITIONS                        | MIN  | TYP     | MAX  | UNITS    |

|--------------------------------|----------------------------------------|------|---------|------|----------|

| OUTPUT COMMON-MODE VOLTAGE     | CONTROL                                |      |         |      |          |

| Small-signal bandwidth         | $R_L = 400 \Omega$                     |      | 180     |      | MHz      |

| Slew rate                      | 2 V <sub>PP</sub> Step                 |      | 80      |      | V/µs     |

| Minimum gain                   |                                        | 0.92 |         |      | V/V      |

| Maximum gain                   |                                        |      |         | 1.17 | V/V      |

| Common-mode offset voltage     |                                        | -5.6 |         | 35   | mV       |

| Input bias current             | V <sub>OCM</sub> = 2.5 V               |      |         | 3    | μA       |

| Input voltage range            |                                        | 1.3  |         | 3.7  | V        |

| Input impedance                |                                        |      | 25    1 |      | kΩ    pF |

| Maximum default voltage        | V <sub>OCM</sub> left floating         |      |         | 2.75 | V        |

| Minimum default voltage        | V <sub>OCM</sub> left floating         | 2.25 |         |      | V        |

| POWER SUPPLY                   |                                        | ·    | ·       |      | ·        |

| Specified operating voltage    |                                        |      |         | 15   | V        |

| Maximum quiescent current      |                                        |      |         | 38   | mA       |

| Minimum quiescent current      |                                        | 10   |         |      | mA       |

| Power-supply rejection (+PSRR) |                                        | 66   |         |      | dB       |

| POWER -DOWN                    |                                        | ·    | ·       | •    | ·        |

| Enable voltage threshold       | Device enabled ON above 2.1 V          |      | 2.1     |      | V        |

| Disable voltage threshold      | Device disabled <i>OFF</i> below 0.7 V |      | 0.7     |      | V        |

| Power-down quiescent current   |                                        |      |         | 1400 | μA       |

| Input bias current             |                                        |      |         | 140  | μA       |

| Input impedance                |                                        |      | 50    1 |      | kΩ    pF |

| Turn-on time delay             |                                        |      | 1000    |      | ns       |

| Turn-off time delay            |                                        |      | 800     |      | ns       |

- (1) See datasheet for absolute maximum and minimum recommended operating conditions.

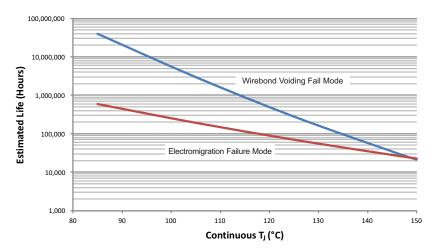

- (2) Silicon operating life design goal is 10 years at 105°C junction temperature (does not include package interconnect life).

- (3) Enhanced plastic product disclaimer applies.

- (4) Electromigration calculation is based on output switching 50% duty cycle at max load of 120 mA.

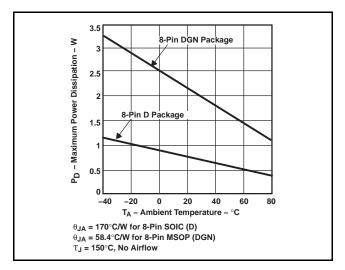

Figure 1. THS4500-EP Derating Chart

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

### TYPICAL CHARACTERISTICS: ±5 V

Figure 2.

Figure 3.

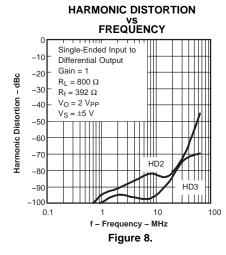

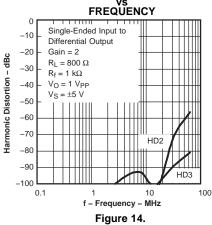

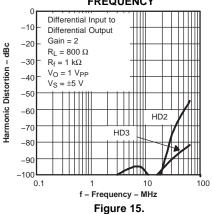

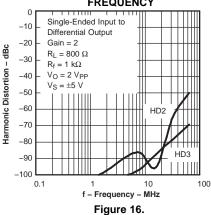

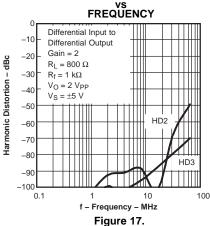

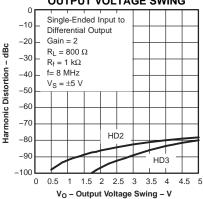

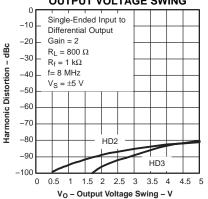

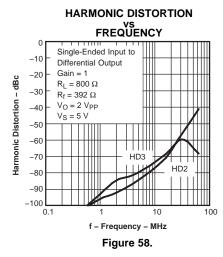

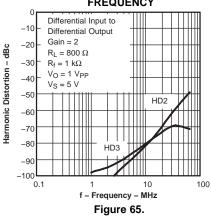

HARMONIC DISTORTION

Figure 4. HARMONIC DISTORTION

Figure 5.

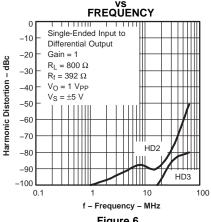

Figure 6. HARMONIC DISTORTION

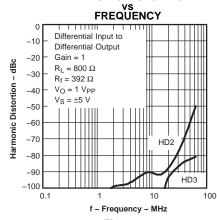

Figure 7.

Copyright © 2013, Texas Instruments Incorporated

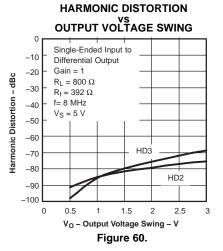

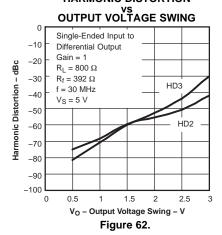

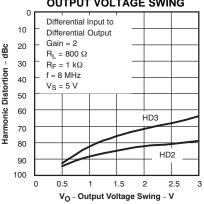

### OUTPUT VOLTAGE SWING

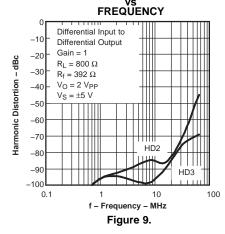

HARMONIC DISTORTION

OUTPUT VOLTAGE SWING

HARMONIC DISTORTION vs

HARMONIC DISTORTION

VS

FREQUENCY

HARMONIC DISTORTION

VS

FREQUENCY

HARMONIC DISTORTION

HARMONIC DISTORTION

VS

OUTPUT VOLTAGE SWING

Figure 18.

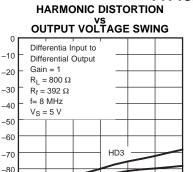

HARMONIC DISTORTION

VS

OUTPUT VOLTAGE SWING

Figure 19.

# TYPICAL CHARACTERISTICS: ±5 V (continued) HARMONIC DISTORTION HARMONIC DISTORTION OUTPUT VOLTAGE SWING OUTPUT VOLTAGE SWING

Copyright © 2013, Texas Instruments Incorporated

### TYPICAL CHARACTERISTICS: ±5 V (continued)

INPUT BIAS AND OFFSET CURRENT

Quiescent Current - mA

0 0.5

$V_S$  - Supply Voltage -  $\pm V$ Figure 40.

2 2.5 3 3.5

4 4.5

1.5

Figure 41.

**COMMON-MODE REJECTION RATIO**

Figure 39.

Figure 42.

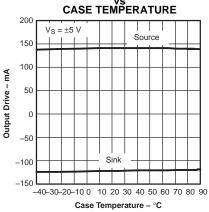

**OUTPUT DRIVE**

Figure 43.

### HARMONIC DISTORTION OUTPUT COMMON-MODE VOLTAGE

Figure 44.

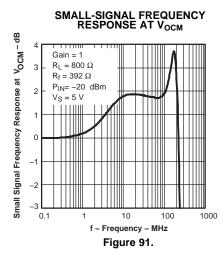

### SMALL-SIGNAL FREQUENCY RESPONSE AT $V_{\text{OCM}}$

Figure 45.

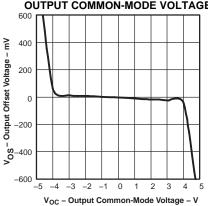

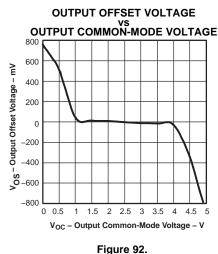

### OUTPUT OFFSET VOLTAGE AT V<sub>OCM</sub> OUTPUT COMMON-MODE VOLTAGE

Figure 46.

### TYPICAL CHARACTERISTICS: ±5 V (continued)

Figure 49.

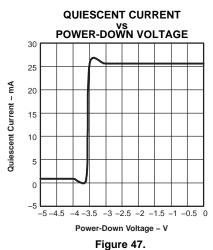

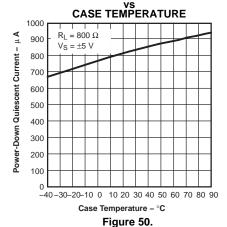

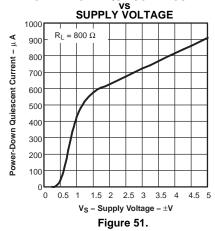

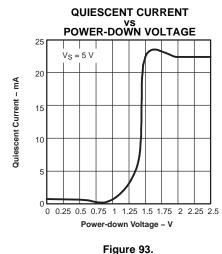

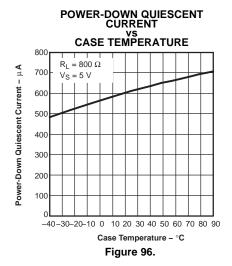

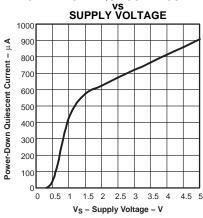

#### POWER-DOWN QUIESCENT CURRENT

### **TYPICAL CHARACTERISTICS: 5 V**

Harmonic Distortion – dBc

-90

-100

0 0.5

<u>SLOS832 – JU</u>NE 2013 www.ti.com

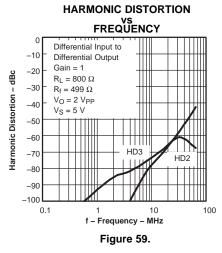

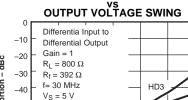

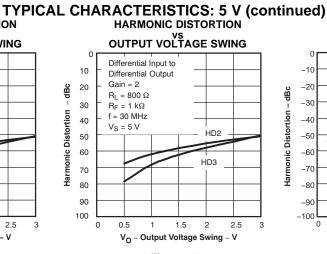

### TYPICAL CHARACTERISTICS: 5 V (continued) ON HARMONIC DISTORTION

HARMONIC DISTORTION

HARMONIC DISTORTION

Vo - Output Voltage Swing - V

Figure 61.

HD2

2.5

2

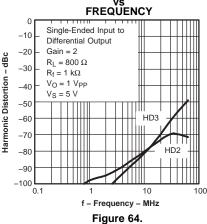

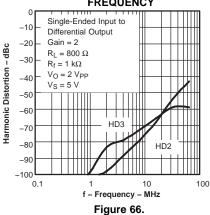

HARMONIC DISTORTION VS FREQUENCY

HARMONIC DISTORTION FREQUENCY

HARMONIC DISTORTION

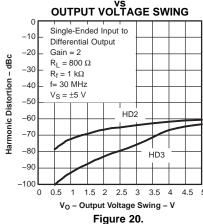

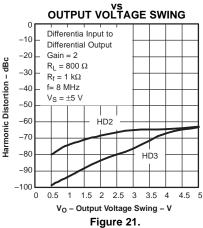

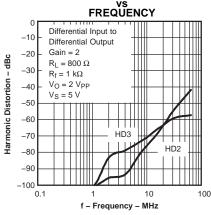

HARMONIC DISTORTION OUTPUT VOLTAGE SWING

Figure 68.

HARMONIC DISTORTION OUTPUT VOLTAGE SWING

Figure 69.

Submit Documentation Feedback

Figure 67.

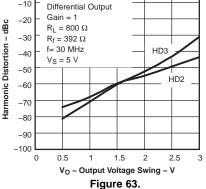

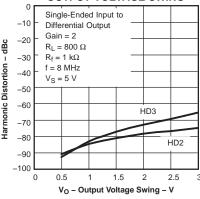

#### HARMONIC DISTORTION OUTPUT VOLTAGE SWING Single-Ended Input to Differential Output Gain = 2 -20 $R_L = 800 \Omega$ Harmonic Distortion – dBc -30 $R_f = 1 k\Omega$ f = 30 MHz -40 $V_S = 5 V$ HD2 -50 -60 HD3 -70 -80 -90 -100 0 2 2.5

Vo - Output Voltage Swing - V Figure 70.

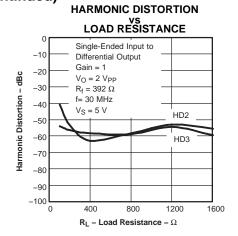

Figure 71.

Figure 72.

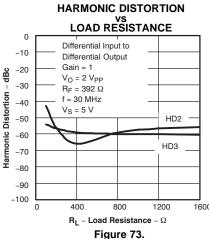

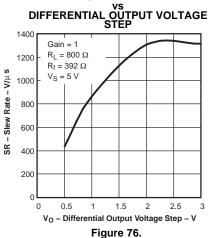

Figure 73. **SLEW RATE**

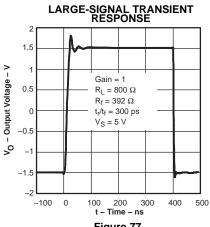

SMALL-SIGNAL TRANSIENT RESPONSE 0.4 0.3 0.2 Output Voltage – V Gain = 10.1  $R_1 = 800 \Omega$  $R_f = 392 \Omega$ 0  $t_r/t_f = 300 \text{ ps}$  $V_S = 5 V$ -0.1 Ş -0.2 -0.3 -0.4 -100 0 100 200 300 400 500 t - Time - ns

Figure 78.

Figure 85.

Case Temperature - °C

Figure 87.

V<sub>S</sub> - Supply Voltage - ±V

Figure 86.

### TYPICAL CHARACTERISTICS: 5 V (continued) N RATIO OUTPUT DRIVE

100.5 101

t - Time - ms Figure 94. 102

Signal - V

-Down

0 0.5 1 1.5 2 2.5 3

Copyright © 2013, Texas Instruments Incorporated

### TYPICAL CHARACTERISTICS: 5 V (continued) POWER-DOWN QUIESCENT CURRENT

Figure 97.

#### APPLICATION INFORMATION

#### **FULLY DIFFERENTIAL AMPLIFIERS**

Differential signaling offers a number of performance advantages in high-speed analog signal processing systems, including immunity to external commonmode noise, suppression of even-order nonlinearities, and increased dynamic range. Fully differential amplifiers not only serve as the primary means of providing gain to a differential signal chain, but also provide a monolithic solution for converting singleended signals into differential signals for easier, higher performance processing. The THS4500 family of amplifiers contains products in Texas Instruments' expanding line of high-performance, fully differential amplifiers. Information on fully differential amplifier fundamentals, as well as implementation specific information, is presented in the Applications Section of this data sheet to provide a better understanding of the operation of the THS4500 family of devices, and to simplify the design process for designs using these amplifiers.

### **APPLICATIONS SECTION**

- Fully Differential Amplifier Terminal Functions

- Input Common-Mode Voltage Range and the THS4500 Family

- Choosing the Proper Value for the Feedback and Gain Resistors

- Application Circuits Using Fully Differential Amplifiers

- Key Design Considerations for Interfacing to an Analog-to-Digital Converter

- Setting the Output Common-Mode Voltage With the V<sub>OCM</sub> Input

- Saving Power with Power-Down Functionality

- Linearity: Definitions, Terminology, Circuit Techniques, and Design Tradeoffs

- An Abbreviated Analysis of Noise in Fully Differential Amplifiers

- Printed-Circuit Board Layout Techniques for Optimal Performance

- Power Dissipation and Thermal Considerations

- Power Supply Decoupling Techniques and Recommendations

- Evaluation Fixtures, Spice Models, and Applications Support

- Additional Reference Material

### FULLY DIFFERENTIAL AMPLIFIER TERMINAL FUNCTIONS

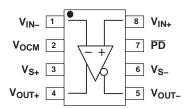

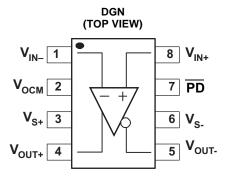

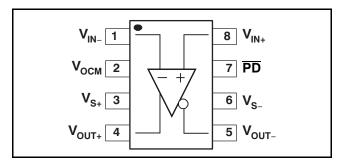

Fully differential amplifiers are typically packaged in eight-pin packages, as shown in Figure 98. The device pins include two inputs  $(V_{IN+}, V_{IN-})$ , two outputs  $(V_{OUT-}, V_{OUT+})$ , two power supplies  $(V_{S+}, V_{S-})$ , an output common-mode control pin  $(V_{OCM})$ , and an optional power-down pin (PD).

Figure 98. Fully Differential Amplifier Pin Diagram

A standard configuration for the device is shown in Figure 98. The functionality of a fully differential amplifier can be imagined as two inverting amplifiers that share a common noninverting terminal (though the voltage is not necessarily fixed). For more information on the basic theory of operation for fully differential amplifiers, refer to the Texas Instruments application note *Fully Differential Amplifiers*, literature number SLOA054.

### INPUT COMMON-MODE VOLTAGE RANGE AND THE THS4500 FAMILY

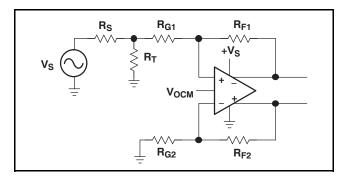

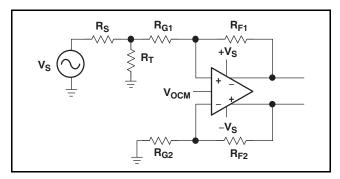

The key difference between the THS4500/1 and the THS4502/3 is the input common-mode range for the four devices. The THS4502 and THS4503 have an input common-mode range that is centered around midrail, and the THS4500 and THS4501 have an input common-mode range that is shifted to include the negative power-supply rail. Selection of one or the other amplifier is determined by the nature of the application. Specifically, the THS4500 and THS4501 are designed for use in single-supply applications where the input signal is ground-referenced, as depicted in Figure 99. The THS4502 and THS4503 are designed for use in single-supply or split-supply applications where the input signal is centered between the power-supply voltages, as depicted in Figure 100.

Product Folder Links: THS4500-EP

**NSTRUMENTS**

SLOS832 - JUNE 2013 www.ti.com

Figure 99. Application Circuit for the THS4500 and THS4501, Featuring Single-Supply Operation With a Ground-Reference Input Signal

Figure 100. Application Circuit for the THS4500 and THS4501, Featuring Split-Supply Operation With an Input Signal Referenced at the Midrail

Equation 1 through Equation 5 are used to calculate the required input common-mode range for a given set of input conditions.

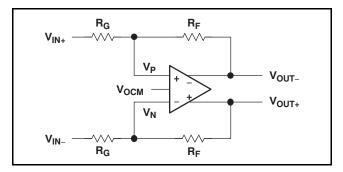

The equations allow calculation of the input commonmode range requirements, given information about the input signal, the output voltage swing, the gain, and the output common-mode voltage. Calculating the maximum and minimum voltage required for V<sub>N</sub> and V<sub>P</sub> (the amplifier input nodes) determines whether or not the input common-mode range is violated or not. Four equations are required: two calculate the output voltages and two calculate the node voltages at  $V_N$  and  $V_P$  (note that only one of these nodes needs calculation, because the amplifier forces a virtual short between the two nodes).

$$V_{OUT+} = \frac{V_{IN+}(1-\beta)-V_{IN-}(1-\beta) + 2V_{OCM}\beta}{2\beta}$$

(1)

$$V_{OUT-} = \frac{-V_{IN+}(1-\beta) + V_{IN-}(1-\beta) + 2V_{OCM}\beta}{2\beta}$$

(2)

$$V_{N} = V_{IN-}(1-\beta) + V_{OUT+}\beta$$

(3)

Where:

$$\beta = \frac{R_G}{R_F + R_G} \tag{4}$$

$$V_P = V_{IN+}(1-\beta) + V_{OIIT-}\beta$$

NOTE: The equations denote the device inputs as V<sub>N</sub> and V<sub>P</sub>, and the circuit inputs as V<sub>IN+</sub> and V<sub>IN-</sub>.

Figure 101. Diagram For Input Common-Mode Range Equations

Table 1 and Table 2 depict the input common-mode range requirements for two different input scenarios, an input referenced around the negative rail and an input referenced around midrail. The tables highlight the differing requirements on input common-mode range, and illustrate the reasoning to choose either the THS4500/1 or the THS4502/3. For signals referenced around the negative power supply, the THS4500/1 should be chosen because its input common-mode range includes the negative supply rail. For all other situations, the THS4502/3 offers slightly improved distortion and noise performance for applications with input signals centered between the power-supply rails.

**Table 1. Negative-Rail Referenced**

| Gain<br>(V/V) | V <sub>IN+</sub><br>(V) | V <sub>IN</sub> _<br>(V) | V <sub>IN</sub><br>(V <sub>PP</sub> ) | V <sub>OCM</sub><br>(V) | V <sub>OD</sub><br>(V <sub>PP</sub> ) | V <sub>NMIN</sub><br>(V) | V <sub>NMAX</sub><br>(V) |

|---------------|-------------------------|--------------------------|---------------------------------------|-------------------------|---------------------------------------|--------------------------|--------------------------|

| 1             | -2.0 to 2.0             | 0                        | 4                                     | 2.5                     | 4                                     | 0.75                     | 1.75                     |

| 2             | -1.0 to 1.0             | 0                        | 2                                     | 2.5                     | 4                                     | 0.5                      | 1.167                    |

| 4             | -0.5 to 0.5             | 0                        | 1                                     | 2.5                     | 4                                     | 0.3                      | 0.7                      |

| 8             | -0.25 to 0.25           | 0                        | 0.5                                   | 2.5                     | 4                                     | 0.167                    | 0.389                    |

| Table | 2 Mid | Irail I | Refei | renced |

|-------|-------|---------|-------|--------|

|       |       |         |       |        |

| Gain<br>(V/V) | V <sub>IN+</sub> (V) | V <sub>IN</sub> _<br>(V) | V <sub>IN</sub><br>(V <sub>PP</sub> ) | V <sub>OCM</sub> (V) | V <sub>OD</sub><br>(V <sub>PP</sub> ) | V <sub>NMIN</sub><br>(V) | V <sub>NMAX</sub> (V) |

|---------------|----------------------|--------------------------|---------------------------------------|----------------------|---------------------------------------|--------------------------|-----------------------|

| 1             | 0.5 to 4.5           | 2.5                      | 4                                     | 2.5                  | 4                                     | 2                        | 3                     |

| 2             | 1.5 to 3.5           | 2.5                      | 2                                     | 2.5                  | 4                                     | 2.16                     | 2.83                  |

| 4             | 2.0 to 3.0           | 2.5                      | 1                                     | 2.5                  | 4                                     | 2.3                      | 2.7                   |

| 8             | 2.25 to 2.75         | 2.5                      | 0.5                                   | 2.5                  | 4                                     | 2.389                    | 2.61                  |

### CHOOSING THE PROPER VALUE FOR THE FEEDBACK AND GAIN RESISTORS

The selection of feedback and gain resistors impacts circuit performance in a number of ways. The values presented in this section provide the optimum highfrequency performance (lowest distortion, frequency response). Since the THS4500 family of amplifiers is developed with a voltage feedback architecture, the choice of resistor values does not have a dominant effect on bandwidth, unlike a current-feedback amplifier. However, resistor choices second-order effects. have For optimal performance, the following feedback resistor values are recommended. In higher gain configurations (gain greater than two), the feedback resistor values have much less effect on the high-frequency performance. Example feedback and gain resistor values are given in the section on basic design considerations (Table 3).

Amplifier loading, noise, and the flatness of the frequency response are three design parameters that should be considered when selecting feedback resistors. Larger resistor values contribute more noise and can induce peaking in the ac response in low gain configurations; smaller resistor values can load the amplifier more heavily, resulting in a reduction in distortion performance. In addition, feedback resistor values, coupled with gain requirements, determine the value of the gain resistors and directly impact the input impedance of the entire circuit. While there are no strict rules about resistor selection, these trends can provide qualitative design guidance.

### APPLICATION CIRCUITS USING FULLY DIFFERENTIAL AMPLIFIERS

Fully differential amplifiers provide designers with a great deal of flexibility in a wide variety of applications. This section provides an overview of some common circuit configurations and gives some design guidelines. Designing the interface to an analog-to-digital converter (ADC), driving lines differentially, and filtering with fully differential amplifiers are a few of the circuits that are covered.

#### **BASIC DESIGN CONSIDERATIONS**

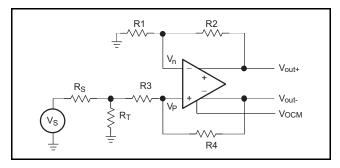

The circuits in Figure 99 through Figure 102 are used to highlight basic design considerations for fully differential amplifier circuit designs.

Table 3. Resistor Values for Balanced Operation in Various Gain Configurations

| $Gain\left(\frac{V_{OD}}{V_{IN}}\right)$ | R2 and R4<br>(Ω) | R1 (Ω) | R3 (Ω) | R <sub>T</sub> (Ω) |

|------------------------------------------|------------------|--------|--------|--------------------|

| 1                                        | 392              | 412    | 383    | 54.9               |

| 1                                        | 499              | 523    | 487    | 53.6               |

| 2                                        | 392              | 215    | 187    | 60.4               |

| 2                                        | 1.3 k            | 665    | 634    | 52.3               |

| 5                                        | 1.3 k            | 274    | 249    | 56.2               |

| 5                                        | 3.32 k           | 681    | 649    | 52.3               |

| 10                                       | 1.3 k            | 147    | 118    | 64.9               |

| 10                                       | 6.81 k           | 698    | 681    | 52.3               |

Figure 102. Diagram for Design Calculations

Equations for calculating fully differential amplifier resistor values in order to obtain balanced operation in the presence of a  $50-\Omega$  source impedance are given in Equation 6 through Equation 9.

$$R_{T} = \frac{1}{\frac{1}{R_{S}} - \frac{1 - \frac{K}{2(1 + K)}}{R3}} \qquad K = \frac{R2}{R1} \quad R2 = R4$$

$$R3 = R1 - (R_{s} || R_{T}) \qquad (6)$$

$$\beta_1 = \frac{R1}{R1 + R2} \quad \beta_2 = \frac{R3 + R_T \parallel R_S}{R3 + R_T \parallel R_S + R4}$$

(7)

$$\frac{V_{OD}}{V_{S}} = 2\left(\frac{1-\beta_{2}}{\beta_{1} + \beta_{2}}\right) \left(\frac{R_{T}}{R_{T} + R_{S}}\right) \tag{8}$$

$$\frac{V_{OD}}{V_{IN}} = 2\left(\frac{1-\beta_2}{\beta_1 + \beta_2}\right) \tag{9}$$

For more detailed information about balance in fully differential amplifiers, see the application report, *Fully Differential Amplifiers* (SLOA054), referenced at the end of this data sheet.

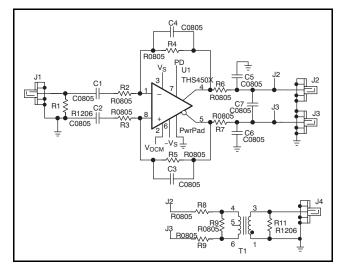

### INTERFACING TO AN ANALOG-TO-DIGITAL CONVERTER

The THS4500 family of amplifiers are designed specifically to interface to today's highest-performance ADCs. This section highlights the key concerns when interfacing to an ADC and provides example interface circuits.

There are several key design concerns when interfacing to an analog-to-digital converter:

- Terminate the input source properly. In highfrequency receiver chains, the source that feeds the fully differential amplifier requires a specific load impedance (that is, 50 Ω).

- Design a symmetric printed circuit board (PCB) layout. Even-order distortion products are heavily influenced by layout, and careful attention to a symmetric layout minimizes these distortion products.

- Minimize inductance in power-supply decoupling traces and components. Poor power-supply decoupling can have a dramatic effect on circuit performance. Since the outputs are differential, differential currents exist in the power-supply pins. Thus, decoupling capacitors should be placed in a manner that minimizes the impedance of the current loop.

- Use separate analog and digital power supplies and grounds. Noise (bounce) in the power supplies (created by digital switching currents) can couple directly into the signal path, and powersupply noise can create higher distortion products as well.

- Use care when filtering. While an RC low-pass filter may be desirable on the output of the amplifier to filter broadband noise, the excess loading can negatively impact the amplifier linearity. Filtering in the feedback path does not have this effect.

- AC-coupling allows easier circuit design. If dccoupling is required, be aware of the excess power dissipation that can occur due to levelshifting the output through the output commonmode voltage control.

- Do not terminate the output unless required. Many open-loop, class-A amplifiers require 50-Ω termination for proper operation, but closed-loop fully differential amplifiers drive a specific output

- voltage regardless of the load impedance present. Terminating the output of a fully differential amplifier with a heavy load adversely affects the amplifier linearity.

- Comprehend the V<sub>OCM</sub> input drive requirements. Determine if the ADC voltage reference can provide the required amount of current to move V<sub>OCM</sub> to the desired value. A buffer may be needed.

- Decouple the V<sub>OCM</sub> pin to eliminate the antenna effect. V<sub>OCM</sub> is a high-impedance node that can act as an antenna. A large decoupling capacitor on this node eliminates this problem.

- Know the input common-mode range. If the input signal is referenced around the negative power-supply rail (for example, around ground on a single 5 V supply), then the THS4500/1 accommodates the input signal. If the input signal is referenced around midrail, choose the THS4502/3 for the best operation.

- Packaging makes a difference at higher frequencies. If possible, choose the smaller, thermally-enhanced MSOP package for the best performance. As a rule, lower junction temperatures provide better performance. If possible, use a thermally-enhanced package, even if the power dissipation is relatively small compared to the maximum power dissipation rating to achieve the best results.

- Understand the effect of the load impedance seen by the fully differential amplifier when performing system-level intercept point calculations. Lighter loads (such as those presented by an ADC) allow smaller intercept points to support the same level of intermodulation distortion performance.

### EXAMPLE ANALOG-TO-DIGITAL CONVERTER DRIVER CIRCUITS

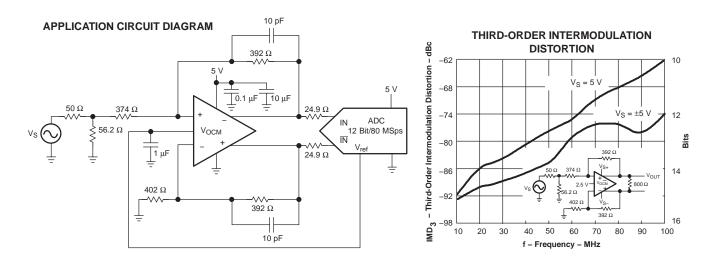

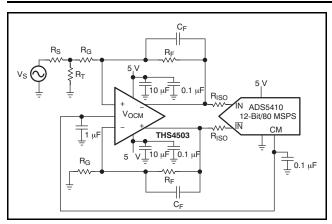

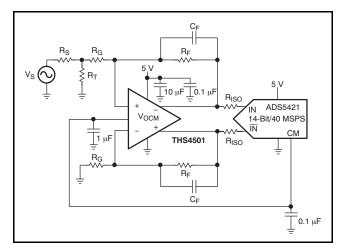

The THS4500 family of devices is designed to drive high-performance ADCs with extremely high linearity, allowing for the maximum effective number of bits at the output of the data converter. Two representative circuits shown below highlight single-supply operation and split supply operation, respectively. Specific feedback resistor, gain resistor, and feedback capacitor values are not shown, as these values depend on the frequency of interest. Information on calculating these values can be found in the applications material above.

24

Figure 103. Using the THS4503 With the ADS5410

Figure 104. Using the THS4501 With the ADS5421

#### **FULLY DIFFERENTIAL LINE DRIVERS**

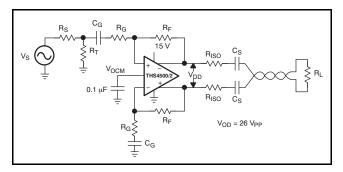

The THS4500 family of amplifiers can be used as high-frequency, high-swing differential line drivers. The high power-supply voltage rating (16.5 V absolute maximum) allows operation on a single 12-V or a single 15-V supply. The high supply voltage, coupled with the ability to provide differential outputs, enables the ability to drive 26  $V_{PP}$  into reasonably heavy loads (250  $\Omega$  or greater). The circuit in Figure 105 illustrates the THS4500 family of devices used as high-speed line drivers. For line driver applications, close attention must be paid to thermal design constraints because of the typically high level of power dissipation.

Figure 105. Fully Differential Line Driver With High Output Swing

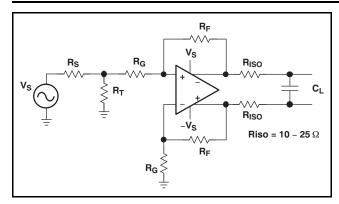

### FILTERING WITH FULLY DIFFERENTIAL AMPLIFIERS

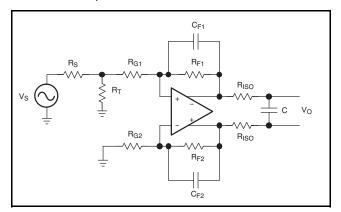

Similar to single-ended counterparts, fully differential amplifiers have the ability to couple filtering functionality with voltage gain. Numerous filter topologies can be based on fully differential amplifiers. Several of these are outlined in the application report *A Differential Circuit Collection* (literature number SLOA064), referenced at the end of this data sheet. The circuit below depicts a simple, two-pole, low-pass filter applicable to many different types of systems. The first pole is set by the resistors and capacitors in the feedback paths, and the second pole is set by the isolation resistors and the capacitor across the outputs of the isolation resistors.

Figure 106. A Two-Pole, Low-Pass Filter Design Using a Fully Differential Amplifier With Poles Located at: P1 =  $(2\pi R_F C_F)^{-1}$  in Hz and P2 =  $(4\pi R_{ISO}C)^{-1}$  in Hz

Often, filters like these are used to eliminate broadband noise and out-of-band distortion products in signal acquisition systems. It should be noted that the increased load placed on the output of the amplifier by the second low-pass filter has a

TEXAS INSTRUMENTS

SLOS832 – JUNE 2013 www.ti.com

detrimental effect on the distortion performance. The preferred method of filtering is to use the feedback network, as the typically smaller capacitances required at these points in the circuit do not load the amplifier nearly as heavily in the passband.

### SETTING THE OUTPUT COMMON-MODE VOLTAGE WITH THE $V_{\text{OCM}}$ INPUT

The output common-mode voltage pin provides a critical function to the fully differential amplifier; it accepts an input voltage and reproduces that input voltage as the output common-mode voltage. In other words, the  $V_{\rm OCM}$  input provides the ability to level-shift the outputs to any voltage inside the output voltage swing of the amplifier.

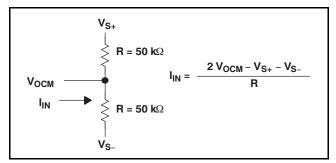

A description of the input circuitry of the  $V_{OCM}$  pin is shown in Figure 107 to facilitate an easier understanding of the  $V_{OCM}$  interface requirements. The  $V_{OCM}$  pin has two 50-k $\Omega$  resistors between the power supply rails to set the default output common-mode voltage to midrail. A voltage applied to the  $V_{OCM}$  pin alters the output common-mode voltage as long as the source has the ability to provide enough current to overdrive the two 50-k $\Omega$  resistors. This phenomenon is depicted in the  $V_{OCM}$  equivalent circuit diagram. Current drive is especially important when using the reference voltage of an analog-to-digital converter to drive  $V_{OCM}$ . Output current drive capabilities differ from part to part, so a voltage buffer may be necessary in some applications.

Figure 107. Equivalent Input Circuit for V<sub>OCM</sub>

By design, the input signal applied to the  $V_{OCM}$  pin propagates to the outputs as a common-mode signal. As shown in Figure 107, the  $V_{OCM}$  input has a high impedance associated with it, dictated by the two 50-k $\Omega$  resistors. While the high impedance allows for relaxed drive requirements, it also allows the pin and any associated PCB traces to act as an antenna. For this reason, a decoupling capacitor is recommended on this node for the sole purpose of filtering any high-

frequency noise that could couple into the signal path through the  $V_{\text{OCM}}$  circuitry. A 0.1- $\mu\text{F}$  or 1- $\mu\text{F}$  capacitance is a reasonable value for eliminating a great deal of broadband interference, but additional, tuned decoupling capacitors should be considered if a specific source of electromagnetic or radio frequency interference is present elsewhere in the system. Information on the ac performance (bandwidth, slew rate) of the  $V_{\text{OCM}}$  circuitry is included in the ELECTRICAL CHARACTERISTICS and TYPICAL CHARACTERISTICS sections.

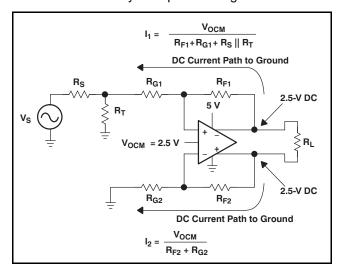

Since the V<sub>OCM</sub> pin provides the ability to set an output common-mode voltage, the ability for increased power dissipation exists. While this possibility does not pose a performance problem for the amplifier, it can cause additional power dissipation of which the system designer should be aware. The circuit shown in Figure 108 demonstrates an example of this phenomenon. For a device operating on a single 5-V supply with an input signal referenced around ground and an output commonmode voltage of 2.5 V, a dc potential exists between the outputs and the inputs of the device. The amplifier sources current into the feedback network in order to provide the circuit with the proper operating point. While there are no serious effects on the circuit performance, the extra power dissipation may need to be included in the system power budget.

Figure 108. Depiction of DC Power Dissipation Caused By Output Level-Shifting in a DC-Coupled Circuit

### SAVING POWER WITH POWER-DOWN FUNCTIONALITY

The THS4500 family of fully differential amplifiers contains devices that come with and without the power-down option. Even-numbered devices have power-down capability, which is described in detail here.

The power-down pin of the amplifiers defaults to the positive supply voltage in the absence of an applied voltage (that is, an internal pull-up resistor is present), putting the amplifier in the *power-on* mode of operation. To turn off the amplifier in an effort to conserve power, the power-down pin can be driven towards the negative rail. The threshold voltages for power-on and power-down are relative to the supply rails and given in the specification tables. Above the *enable threshold voltage*, the device is on. Below the *disable threshold voltage*, the device is off. Behavior between these threshold voltages is not specified.

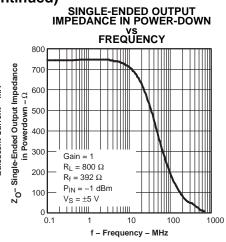

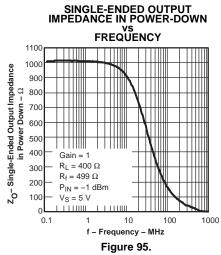

Note that this power-down functionality is just that; the amplifier consumes less power in power-down mode. The power-down mode is not intended to provide a high-impedance output. In other words, the power-down functionality is not intended to allow use as a 3-state bus driver. When in power-down mode, the impedance looking back into the output of the amplifier is dominated by the feedback and gain setting resistors.

The time delays associated with turning the device on and off are specified as the time it takes for the amplifier to reach 50% of the nominal quiescent current. The time delays are on the order of microseconds because the amplifier moves in and out of the linear mode of operation in these transitions.

# LINEARITY: DEFINITIONS, TERMINOLOGY, CIRCUIT TECHNIQUES, AND DESIGN TRADEOFFS

The THS4500 family of devices features unprecedented distortion performance for monolithic fully differential amplifiers. This section focuses on the fundamentals of distortion, circuit techniques for reducing nonlinearity, and methods for equating distortion of fully differential amplifiers to desired linearity specifications in RF receiver chains.

Amplifiers are generally thought of as *linear* devices. In other words, the output of an amplifier is a linearly scaled version of the input signal applied to it. In reality, however, amplifier transfer functions are nonlinear. Minimizing amplifier nonlinearity is a primary design goal in many applications.

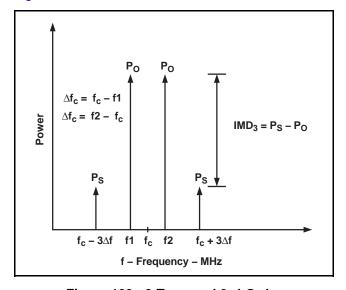

Intercept points are specifications that have long been used as key design criteria in the RF communications world as a metric for the intermodulation distortion performance of a device in the signal chain (for example, amplifiers, mixers,

etc.). Use of the intercept point, rather than strictly the intermodulation distortion, allows for simpler system-level calculations. Intercept points, like noise figures, can be easily cascaded back and forth through a signal chain to determine the overall receiver chain intermodulation distortion performance. The relationship between intermodulation distortion and intercept point is depicted in Figure 109 and Figure 110.

Figure 109. 2-Tone and 3rd-Order Intermodulation Products

Figure 110. Graphical Representation of 2-Tone and 3rd-Order Intercept Point

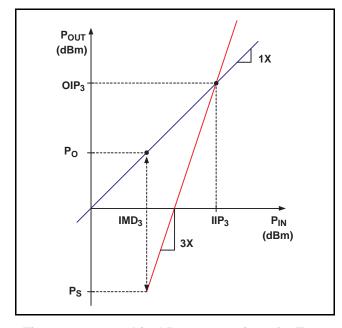

Due to the intercept point ease-of-use in system level calculations for receiver chains, it has become the specification of choice for guiding distortion-related design decisions. Traditionally, these systems use primarily class-A, single-ended RF amplifiers as gain blocks. These RF amplifiers are typically designed to operate in a 50- $\Omega$  environment, just like the rest of the receiver chain. Since intercept points are given in dBm, this implies an associated impedance (50  $\Omega$ ).

However, with a fully differential amplifier, the output does not require termination as an RF amplifier would. Because closed-loop amplifiers deliver signals to the outputs regardless of the impedance present, it is important to comprehend this feature when evaluating the intercept point of a fully differential amplifier. The THS4500 series of devices yields optimum distortion performance when loaded with 200  $\Omega$  to 1  $k\Omega$ , very similar to the input impedance of an analog-to-digital converter over its input frequency band. As a result, terminating the input of the ADC to 50  $\Omega$  can actually be detrimental to system performance.

This discontinuity between open-loop, class-A amplifiers and closed-loop, class-AB amplifiers becomes apparent when comparing the intercept points of the two types of devices. Equation 10 gives the definition of an intercept point, relative to the intermodulation distortion.

$$\begin{aligned} \text{OIP}_3 &= \text{P}_\text{O} + \left(\frac{|\text{IMD}_3|}{2}\right) \text{ where} \\ \text{P}_\text{O} &= 10 \log \left(\frac{\text{V}_{\text{Pdiff}}^2}{2\text{R}_\text{L} \times 0.001}\right) \end{aligned} \tag{10}$$

NOTE:  $P_0$  is the output power of a single tone,  $R_L$  is the differential load resistance, and  $V_{P(diff)}$  is the differential peak voltage for a single tone. (11)

As can be seen in the equations, when a higher impedance is used, the same level of intermodulation distortion performance results in a lower intercept point. Therefore, it is important to understand the impedance seen by the output of the fully differential amplifier when selecting a minimum intercept point. Figure 111 shows the relationship between the strict definition of an intercept point with a normalized, or equivalent, intercept point for the THS4500.

Figure 111. Equivalent 3rd-Order Intercept Point for the THS4500

Comparing specifications between different device types becomes easier when a common impedance level is assumed. For this reason, the intercept points on the THS4500 family of devices are reported normalized to a  $50-\Omega$  load impedance.

### AN ANALYSIS OF NOISE IN FULLY DIFFERENTIAL AMPLIFIERS

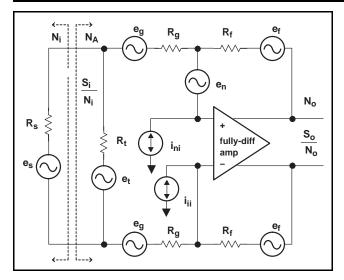

Noise analysis in fully differential amplifiers is analogous to noise analysis in single-ended amplifiers; the same concepts apply. Figure 112 shows a generic circuit diagram consisting of a voltage source, a termination resistor, two gain setting resistors, two feedback resistors, and a fully differential amplifier is shown, including all the relevant noise sources. From this circuit, the noise factor (F) and noise figure (NF) are calculated. The figures indicate the appropriate scaling factor for each of the noise sources in two different cases. The first case includes the termination resistor, and the second, simplified case assumes that the voltage source is properly terminated by the gain-setting resistors. With these scaling factors, the amplifier input noise power (N<sub>A</sub>) can be calculated by summing each individual noise source with its scaling factor. The noise delivered to the amplifier by the source  $(N_1)$ and input noise power are used to calculate the noise factor and noise figure as shown in Equation 23 through Equation 27.

Figure 112. Noise Sources in a Fully Differential Amplifier Circuit

### Scaling Factors for Individual Noise Sources Assuming a Finite Value Termination Resistor

N<sub>A</sub>: Fully Differential Amplifier

Noise

Source Scale Factor

$$(e_{ni})^2 \qquad \left[ \frac{R_g}{R_f} + \frac{R_g}{R_g + \frac{R_s R_t}{2(R_s + R_t)}} \right]^2$$

(12)

$$(i_{ni})^2 \qquad R_g^2$$

(13)

$$(i_{ij})^2 \qquad R_g^2 \tag{14}$$

$$4kTR_{t} = \left(\frac{\frac{2R_{s}R_{G}}{R_{s} + 2R_{g}}}{\frac{2R_{s}R_{g}}{R_{s} + 2R_{g}}}\right)^{2}$$

(15)

$$4kTR_{f} 2 \times \left(\frac{R_{g}}{R_{f}}\right)^{2} (16)$$

$$4kTR_g 2 \times \left[\frac{R_g}{R_g + \frac{R_sR_t}{2(R_s + R_t)}}\right]^2 (17)$$

# Scaling Factors for Individual Noise Sources Asseming No Termination Resistance is Used (that is, $R_{\mathsf{T}}$ is Open)

$N_A$ : Fully Differential Amplifier; termination =  $2R_g$

Noise

Source Scale Factor

$$(e_{ni})^2$$

$\left[\frac{R_g}{R_f} + \frac{R_g}{R_g + \frac{R_s}{2}}\right]^2$  (18)

$$(i_{ni})^2 \qquad R_g^2 \tag{19}$$

$$(i_{ij})^2 \qquad R_g^2 \tag{20}$$

$$4kTR_f$$

$2 \times \left(\frac{R_g}{R_f}\right)^2$  (21)

$$_{4kTR_g}$$

$_{2} \times \left[\frac{R_g}{R_g + \frac{R_s}{2}}\right]^2$  (22)

### **Input Noise With a Termination Resistor**

$$N_{i} = 4kTR_{s} \left[ \frac{2R_{t}R_{g}}{\frac{R_{t} + 2R_{g}}{R_{s} + \frac{2R_{t}R_{g}}{R_{t} + 2R_{g}}}} \right]^{2}$$

(23)

### **Input Noise Assuming No Termination Resistor**

$$N_{i} = 4kTR_{S} \left[ \frac{2R_{G}}{R_{S} + 2R_{G}} \right]^{2}$$

(24)

#### **Noise Factor and Noise Figure Calculations**

$$N_A = \Sigma(Noise Source \times Scale Factor)$$

(25)

$$F = 1 + \frac{N_A}{N_I} \tag{26}$$

$$NF = 10 \log (F) \tag{27}$$

## PRINTED CIRCUIT BOARD LAYOUT TECHNIQUES FOR OPTIMAL PERFORMANCE

Achieving optimum performance with high frequency amplifier-like devices in the THS4500 family requires careful attention to PCB layout parasitic and external component types.

Recommendations that optimize performance include:

- Minimize parasitic capacitance to any ac ground for all of the signal I/O pins. Parasitic capacitance on the output and input pins can cause instability. To reduce unwanted capacitance, a window around the signal I/O pins should be opened in all of the ground and power planes around those pins. Otherwise, ground and power planes should be unbroken elsewhere on the board.

- Minimize the distance (< 0.25", 6.35 mm) from the power-supply pins to high frequency 0.1-µF decoupling capacitors. At the device pins, the ground and power-plane layout should not be in close proximity to the signal I/O pins. Avoid narrow power and ground traces to minimize inductance between the pins and the decoupling capacitors. The power supply connections should always be decoupled with these capacitors. Larger (6.8 µF or more) tantalum decoupling capacitors, effective at lower frequency, should also be used on the main supply pins. These may be placed somewhat farther from the device and may be shared among several devices in the same area of the PCB. The primary goal is to minimize the impedance seen in the differentialcurrent return paths.

- Careful selection and placement of external high-frequency components preserve the performance of the THS4500 family. Resistors should be a very low reactance type. Surfacemount resistors work best and allow a tighter overall layout. Metal-film and carbon composition, axially-leaded resistors can also provide good high frequency performance. Again, keep the leads and PCB trace length as short as possible. Never use wirewound type resistors in a highfrequency application. Since the output pin and inverting input pins are the most sensitive to parasitic capacitance. always position feedback and series output resistors, if any, as close as possible to the inverting input pins and output pins. Other network components, such as input termination resistors, should be placed close to the gain-setting resistors. Even with a low parasitic capacitance shunting the external resistors, excessively high resistor values can create significant time constants that can degrade performance. Good axial metal-film or surfacemount resistors have approximately 0.2 pF in shunt with the resistor. For resistor values greater than 2.0 kΩ, this parasitic capacitance can add a

- pole and/or a zero below 400 MHz that can affect circuit operation. Keep resistor values as low as possible, consistent with load driving considerations.

- Connections to other wideband devices on the board may be made with short direct traces or through onboard transmission lines. For short connections, consider the trace and the input to the next device as a lumped capacitive load. Relatively wide traces (50 mils to 100 mils, or 1.27 mm to 2.54 mm) should be used, preferably with ground and power planes opened up around them. Estimate the total capacitive load and determine if isolation resistors on the outputs are necessary. Low parasitic capacitive loads (less than 4 pF) may not need an R<sub>S</sub> since the THS4500 family is nominally compensated to operate with a 2-pF parasitic load. Higher parasitic capacitive loads without an R<sub>S</sub> are allowed as the signal gain increases (increasing the unloaded phase margin). If a long trace is required, and the 6-dB signal loss intrinsic to a doubly-terminated transmission line is acceptable, implement a matched impedance transmission line using microstrip or stripline techniques (consult an ECL design handbook for microstrip and stripline layout techniques).

- A 50-Ω environment is normally not necessary onboard, and in fact, a higher impedance environment improves distortion as shown in the distortion versus load plots. With a characteristic board trace impedance defined based onboard material and trace dimensions, a matching series resistor into the trace from the output of the THS4500 family is used as well as a terminating shunt resistor at the input of the destination device.

- Remember also that the terminating impedance is the parallel combination of the shunt resistor and the input impedance of the destination device: this total effective impedance should be set to match the trace impedance. If the 6-dB attenuation of a doubly-terminated transmission line unacceptable, a long trace can be seriesterminated at the source end only. Treat the trace as a capacitive load in this case. configuration does not preserve signal integrity as well as a doubly-terminated line. If the input impedance of the destination device is low, there is some signal attenuation due to the voltage divider formed by the series output into the terminating impedance.

- Socketing a high-speed part such as the THS4500 family is not recommended. The additional lead length and pin-to-pin capacitance introduced by the socket can create an extremely troublesome parasitic network that can make it almost impossible to achieve a smooth, stable frequency response. Best results are obtained by soldering

the THS4500 family parts directly onto the board.

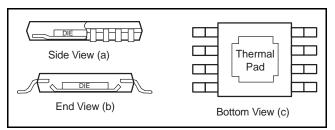

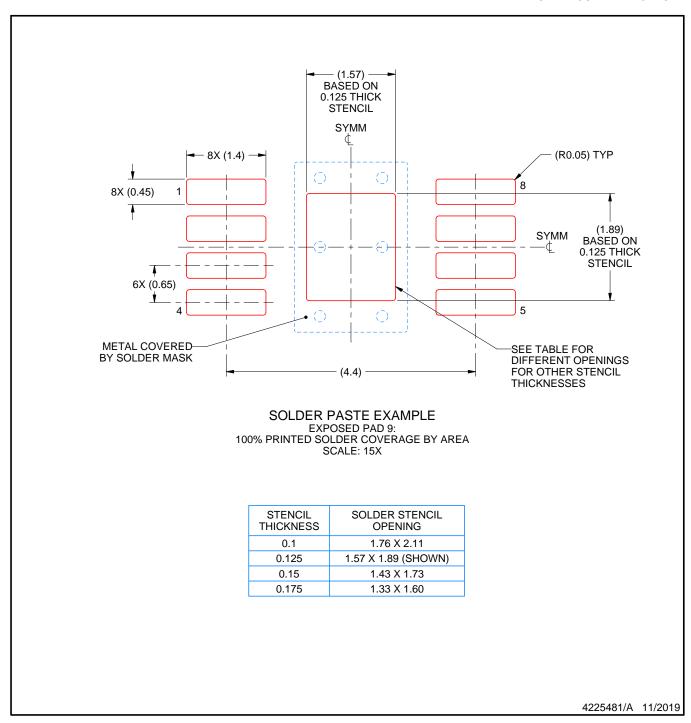

#### PowerPAD DESIGN CONSIDERATIONS

The THS4500 family is available in a thermally-enhanced PowerPAD set of packages. These packages are constructed using a downset leadframe upon which the die is mounted [see Figure 113(a) and Figure 113(b)]. This arrangement results in the lead frame being exposed as a thermal pad on the underside of the package [see Figure 113(c)]. Because this thermal pad has direct thermal contact with the die, excellent thermal performance can be achieved by providing a good thermal path away from the thermal pad.

The PowerPAD package allows for both assembly and thermal management in one manufacturing operation. During the surface-mount solder operation (when the leads are being soldered), the thermal pad can also be soldered to a copper area underneath the package. Through the use of thermal paths within this copper area, heat can be conducted away from the package into either a ground plane or other heat dissipating device.

The PowerPAD package represents a breakthrough in combining the small area and ease of assembly of surface mount with the, heretofore, awkward mechanical methods of heatsinking.

Figure 113. Views of PowerPAD, Thermally-Enhanced Package

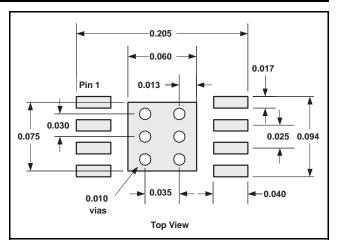

Although there are many ways to properly heatsink the PowerPAD package, the following steps illustrate the recommended approach.

Figure 114. PowerPAD PCB Etch and Via Pattern

#### PowerPAD PCB LAYOUT CONSIDERATIONS

- Prepare the PCB with a top side etch pattern as shown in Figure 114. There should be etch for the leads as well as etch for the thermal pad.

- Place five holes in the area of the thermal pad.

These holes should be 13 mils (0.33 mm) in diameter. Keep them small so that solder wicking through the holes is not a problem during reflow.

- 3. Additional vias may be placed anywhere along the thermal plane outside of the thermal pad area. These holes help dissipate the heat generated by the THS4500 family IC. These additional vias may be larger than the 13-mil diameter vias directly under the thermal pad. They can be larger because they are not in the thermal pad area to be soldered so that wicking is not a problem.

- 4. Connect all holes to the internal ground plane.

- 5. When connecting these holes to the ground plane, do not use the typical web or spoke via connection methodology. Web connections have a high thermal resistance connection that is useful for slowing the heat transfer during soldering operations. This transfer slowing makes the soldering of vias that have plane connections easier. In this application, however, low thermal resistance is desired for the most efficient heat transfer. Therefore, the holes under the THS4500 family PowerPAD package should make their connection to the internal ground plane with a connection around complete the entire circumference of the plated-through hole.

TEXAS INSTRUMENTS

SLOS832 – JUNE 2013 www.ti.com

- 6. The top-side solder mask should leave the terminals of the package and the thermal pad area with its five holes exposed. The bottom-side solder mask should cover the five holes of the thermal pad area. This configuration prevents solder from being pulled away from the thermal pad area during the reflow process.

- Apply solder paste to the exposed thermal pad area and all of the IC terminals.

- 8. With these preparatory steps in place, the IC is simply placed in position and run through the solder reflow operation as any standard surfacemount component. This process results in a part that is properly installed.

### POWER DISSIPATION AND THERMAL CONSIDERATIONS

The THS4500 family of devices does not incorporate automatic thermal shutoff protection, so the designer must take care to ensure that the design does not violate the absolute maximum junction temperature of the device. Failure may result if the absolute maximum junction temperature of +150°C is exceeded. For best performance, design for a maximum junction temperature of +125°C. Between +125°C and +150°C, damage does not occur, but the performance of the amplifier begins to degrade.

The thermal characteristics of the device are dictated by the package and the PCB. Maximum power dissipation for a given package can be calculated using the following formula.

$$P_{\text{Dmax}} = \frac{T_{\text{MAX}} - T_{\text{A}}}{\theta_{\text{JA}}}$$

Where:

$P_{\text{Dmax}}$  is the maximum power dissipation in the amplifier (W).

$T_{\text{MAX}}$  is the absolute maximum junction temperature (°C).

$T_A$  is the ambient temperature (°C).

$$\theta_{JA} = \theta_{JC} + \theta_{CA}$$

$\theta_{JC}$  is the thermal coefficient from the silicon junctions to the case (°C/W).

$\theta_{CA}$  is the thermal coefficient from the case to ambient air (°C/W). (28)

For systems where heat dissipation is more critical, the THS4500 family of devices is offered in an MSOP-8 package with PowerPAD. The thermal coefficient for the MSOP PowerPAD package is substantially improved over the traditional SOIC.

Maximum power dissipation levels are depicted in Figure 115 for the two packages. The data for the DGN package assumes a board layout that follows the PowerPAD layout guidelines referenced above and detailed in the PowerPAD application notes in the Additional Reference Material section at the end of the data sheet.

Figure 115. Maximum Power Dissipation vs

Ambient Temperature

When determining whether or not the device satisfies the maximum power dissipation requirement, it is important to not only consider quiescent power dissipation, but also dynamic power dissipation. Often times, this consideration is difficult to quantify because the signal pattern is inconsistent; an estimate of the RMS power dissipation can provide visibility into a possible problem.

#### DRIVING CAPACITIVE LOADS