# DDR2 Memory Interface Clocks and Registers – Overview

Christian Schmoeller

CDC - Clock Distribution Circuits

#### **ABSTRACT**

This application report gives an overview of the existing JEDEC DDR2 Register and PLL Buffer specifications and compliant TI devices.

#### Contents 1 1.2 1.3 Package Options 6 1.4 2 2.2 2.3 SSTUx32865 9 2.4 2.5 3 PLL Overview 12 4 5 List of Figures 1 2 3 4 5 6 7 8 9 10 CUx877 Package (40-Pad QFN and 52-Ball BGA)...... 12 **List of Tables** 1 2 3 4 5 6 7

## 1 DDR2 Buffer Components for RDIMM

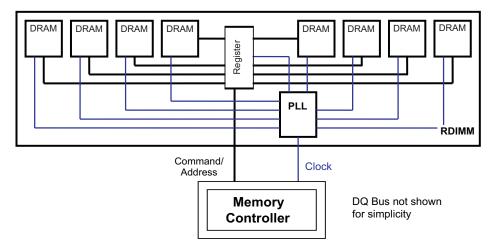

On DDR2 Registered Dual Inline Memory Modules (RDIMM) PLLs and registers are used to buffer the Clock, Command, Control, and Address signals coming from the memory controller.

Figure 1. Usage of Register and PLL Buffer on RDIMM

## 1.1 JEDEC Compliance

The register and PLL devices for DDR2 RDIMM are standardized and specified by the JEDEC community. Over the lifetime of DDR2, several generations of those specifications have evolved. Later generations have tighter specifications for performance parameters (e.g., jitter, t<sub>PDM</sub>) to support higher speed nodes.

All of TI's DDR2 interface devices are compliant to their corresponding JEDEC standards.

## 1.2 DDR2 PLL

A PLL is used to buffer the clock signals on DDR2 RDIMM. The input clock is copied to several output clock (e.g., a 1:10 buffer copies one input clock to 10 output clocks). DDR2 PLLs are used as zero delay clock buffers. For more information, review the application report *Application Examples for the CDCUx877X PLL Family* (SCAA087).

## 1.3 DDR2 Register

A synchronously latched register is used to buffer the Command, Address and Control signals on DDR2 RDIMM.

## 1.3.1 1:1 and 1:2 Modes

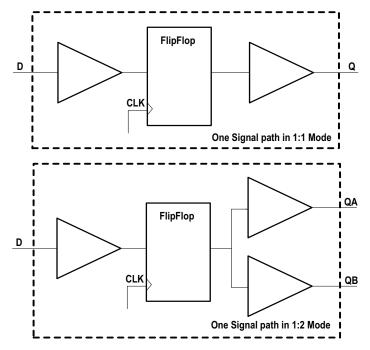

Depending on the type of register, it can be used as a 1:1 or a 1:2 buffer. The 1:1 buffer means that each input has one output copy. The 1:2 buffer means that each input has two output copies.

Figure 2. 1:1 and 1:2 Buffer Mode Example

## 1.3.2 Cascading of Registers

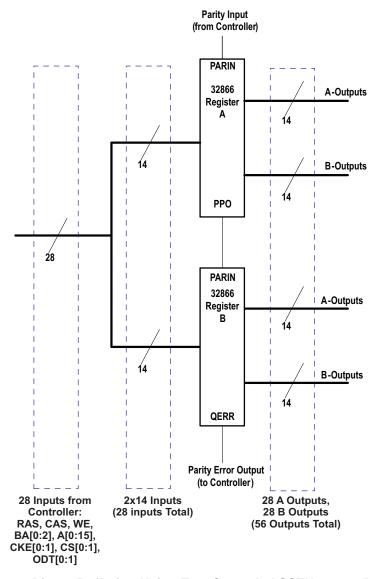

If the bit width of a register is insufficient (e.g., 28 signals need to be buffered, but the register only has 14 inputs), two devices have to be cascaded or a different type of register must be chosen.

Figure 3. 28-Bit 1:2 Buffering Using Two Cascaded SSTUx32866 Registers

#### 1.3.3 Mirror Mode

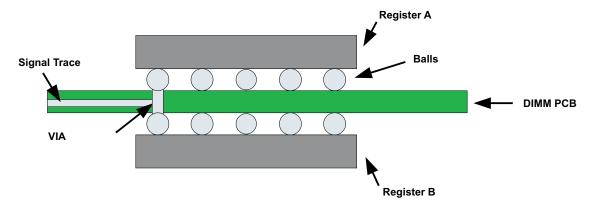

Some registers have the possibility to mirror their input ball-out. This can be used to optimize layout if two registers are used. It allows mounting the registers back to back, one on each side of the DIMM.

Figure 4. Back-to-Back Mounting of Two Registers With Mirror Ball-Out

## 1.3.4 Parity Check

Most of the register devices also offer a parity check feature. Those devices compare the parity checksum of all Command and Control signals to a parity signal. It has to be provided by the memory controller one cycle after the corresponding Command and Control signals are latched in. In case the parity does not match, the register output ERROUT is pulled low. Usually the system freezes in that case to prevent any corruption of data.

## 1.4 Package Options

DDR2 registers and PLLs are available in several package options. Each package has a individual 3-letter designator, which is part of the orderable part number.

Example for a complete part number: SN74SSTUB32866ZWLR

SN74SSTUB32866: Device Name

ZWL: 3-letter Package Designator

R: Packing option (T=Tray, R=Reel)

Table 1 is listing all the available packages and a short description.

Table 1. TI DDR2 Interface Devices Package Overview

| Designator <sup>(1)</sup> | Туре  | Balls/Pads | Devices                                                                                                                                | RoHs<br>Compliant <sup>(2)</sup> | Green<br>Compliant <sup>(3)</sup> | Comment                                      |

|---------------------------|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------|----------------------------------------------|

| GKE                       | LFBGA | 96         | SSTU32864<br>SSTU32864C<br>SSTU32864D<br>SSTU32864E<br>SSTU32866                                                                       | No                               | No                                |                                              |

| ZKE                       | LFBGA | 96         | SSTU32864<br>SSTU32864C<br>SSTU32864D<br>SSTU32864E<br>SSTUB32864<br>SSTUB32866<br>SSTU32866<br>SSTU32866A<br>SSTUB32866<br>SSTUB32866 | Yes                              | Yes                               | Same as GKE, but<br>fully green<br>compliant |

| ZWL                       | LFBGA | 96         | SSTUB32866<br>SSTEB32866                                                                                                               | Yes                              | Yes                               | Improved signal Integrity                    |

| ZJB                       | TFBGA | 160        | SSTUB32865<br>SSTUB32865A                                                                                                              | Yes                              | Yes                               |                                              |

| <u>ZRH</u>                | NFBGA | 176        | SSTUB32868<br>SSTUB32868A                                                                                                              | Yes                              | Yes                               |                                              |

| <u>GQL</u>                | BGA   | 52         | CDCU877<br>CDCU877A                                                                                                                    | No                               | No                                |                                              |

| ZQL                       | BGA   | 52         | CDCU877<br>CDCU877A<br>CDCU877B<br>CDCUA877<br>CDCU2A877                                                                               | Yes                              | Yes                               | Same as GQL, but fully green compliant       |

| RTB                       | QFN   | 40         | CDCU877<br>CDCU877A                                                                                                                    | No                               | No                                |                                              |

| RHA                       | QFN   | 40         | CDCU877<br>CDCU877A                                                                                                                    | Yes                              | Yes                               | Same as RTB, but fully green compliant       |

<sup>(1)</sup> Click on Links to open package drawings

<sup>(2)</sup> Device does not contain restricted RoHs 6 substances (Cadmium, hexavalent Chromium, Lead, Mercury, PBBs, PBDEs).

<sup>(3)</sup> RoHs compliant and also free of Halogens (Bromine and Chlorine). For more information, see the Eco-Info page on the TI Web site.

www.ti.com Register Overview

## 2 Register Overview

The register is used to buffer the Command-, Control- and Address-signals on DDR2 RDIMM.

## 2.1 SSTUx32864

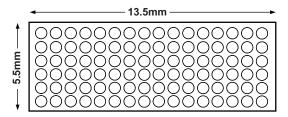

Figure 5. SSTUx32864 Package (96-Ball LFBGA)

## 2.1.1 General Information

- 25-bit 1:1 or 14-bit to 28-bit 1:2 configuration possible

- Able to cascade with a second SSTUx32864

- No parity check

- Configurable ball-out (mirror function)

- First DDR2 register specified by JEDEC (JESD82-7)

Table 2. Available SSTUx32864-Compliant Devices From TI

| SN74SSTU32864<br>Package Options: GKE, ZKE  | <ul> <li>First generation, supports DDR2-400 and DDR2-533</li> <li>Propagation delay t<sub>pdm</sub> 1.4 ns-2.5 ns</li> <li>Top marking: SU864</li> </ul>                                                                                                                                                        |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SN74SSTU32864C<br>Package Options: GKE, ZKE | <ul> <li>First generation, supports DDR2-400 and DDR2-533</li> <li>Propagation delay t<sub>pdm</sub> 1.4 ns-2.4 ns</li> <li>Top marking: S864C</li> </ul>                                                                                                                                                        |

| SN74SSTU32864D<br>Package Options: GKE, ZKE | <ul> <li>First generation, supports DDR2-400 and DDR2-533</li> <li>Propagation delay t<sub>pdm</sub> 1.4 ns-2.15 ns</li> <li>Top marking: SU864D</li> </ul>                                                                                                                                                      |

| SN74SSTU32864E<br>Package Options: GKE, ZKE | First generation, supports DDR2-400 and DDR2-533     Propagation delay t <sub>pdm</sub> 1.4 ns–2.15 ns     Improved signal integrity compared to previous versions     Top marking: S864E                                                                                                                        |

| SN74SSTUB32864 Package Options: ZKE         | - Third generation, supports DDR2-400/533/667/800 - Propagation delay t <sub>pdm</sub> 1.1 ns-1.5 ns - Improved signal integrity compared to previous versions - Fully backward-compatible - Supports industrial temperature range (-40°C-85°C) - Recommended solution for most new designs - Top marking: SB864 |

| 74SSTUB32864A Package Options: ZKE          | - Third generation, supports DDR2-400/533/667/800 - Propagation delay t <sub>pdm</sub> 1.1 ns-1.5 ns - Supports industrial temperature range (-40°C-85°C) - Basically same as SN74SSTUB32864, but with higher slew rate - Top marking: SB864A                                                                    |

Register Overview www.ti.com

## 2.2 SSTUx32866

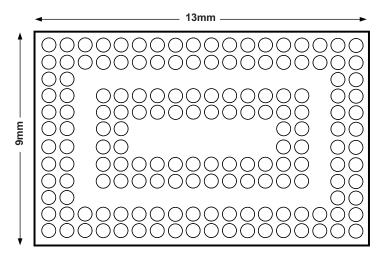

Figure 6. SSTUx32866 Package (96-Ball LFBGA)

#### 2.2.1 General Information

- 25-bit 1:1 or 14-bit to 28-bit 1:2 configuration possible

- Able to cascade with a second SSTUx32866

- Same as SSTUx32864, but additionally with parity check of Command and Address signals

- Configurable ball-out (mirror function)

- JEDEC specifications:

- SSTU32866 (JESD82-10)

- SSTUA32866 (JESD82-16)

- SSTUB32866 (JESD82-25)

Table 3. Available SSTUx32866-Compliant Devices From TI

| SN74SSTU32866<br>Package Options: GKE, ZKE            | <ul> <li>First generation, supports DDR2-400 and DDR2-533</li> <li>Propagation delay t<sub>pdm</sub> 1.4 ns-2.5 ns</li> <li>Top marking: SU866</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SN74SSTU32866A<br>Package Options: ZKE                | <ul> <li>First generation, supports DDR2-400 and DDR2-533</li> <li>Propagation delay t<sub>pdm</sub> 1.4 ns-2.15 ns</li> <li>Top marking: SU866A</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                 |

| SN74SSTUB32866 Package Options: ZKE, ZWL              | <ul> <li>Third generation, supports DDR2-400/533/667/800</li> <li>Propagation delay t<sub>pdm</sub> 1.1 ns-1.5 ns</li> <li>Improved signal integrity compared to previous versions</li> <li>Fully backward-compatible</li> <li>Parity input pulldown resistor of 150 kΩ allows usage on typical SSTUx32864 applications</li> <li>Supports industrial temperature range (-40°C-85°C)</li> <li>ZWL package option further improves signal integrity</li> <li>Recommended solution for most new designs</li> <li>Top marking: SB866</li> </ul> |

| 74SSTUB32866A<br>Package Options: ZKE                 | - Third generation, supports DDR2-400/533/667/800 - Propagation delay t <sub>pdm</sub> 1.1 ns-1.5 ns - Supports industrial temperature range (-40°C-85°C) - Basically same as SN74SSTUB32866 but with higher slew rate - Top marking: SB866A                                                                                                                                                                                                                                                                                                |

| SN74SSTEB32866 <sup>(1)</sup><br>Package Options: ZWL | - Same as SN74SSTUB32866, but supports VDD voltage range 1.425 V-1.9 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

At present, engineering samples for this device are available. Release to market is planned for June 2009.

www.ti.com Register Overview

## 2.3 SSTUx32865

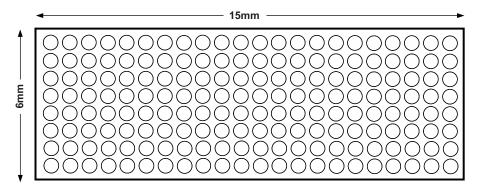

Figure 7. SSTUx32865 Package (160-Ball TFBGA)

## 2.3.1 General Information

- 28-bit to 56-bit 1:2 configuration

- With parity check of Command and Address signals

- Integrates the functionality of two SSTUx32866 into a single device

- No mirror function

- Fits on VLP DIMMs

- JEDEC Specifications:

- SSTU32868 (JESD82-9)

- SSTUA32S865/SSTUA32D865 (JESD82-19)

- SSTUB32868 (JESD82-24)

Table 4. Available SSTUx32865-Compliant Devices From TI

| 74SSTUB32865<br>Package Options: ZJB  | - Third generation, supports DDR2-400/533/667/800 - Propagation delay t <sub>pdm</sub> 1.1 ns- 1.5 ns - Fully backward-compatible - Supports industrial temperature range ( -40°C-85°C) - Top marking: SB865 |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 74SSTUB32865A<br>Package Options: ZJB | <ul><li>Same as 74SSTUB32865 but with higher drive strength and slew rate</li><li>Top marking: SB865A</li></ul>                                                                                              |

Register Overview www.ti.com

## 2.4 SSTUx32868

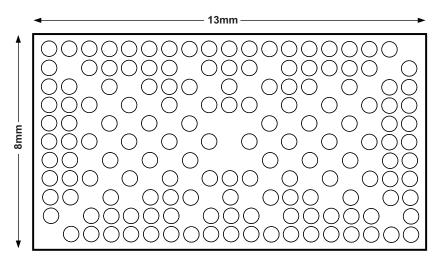

Figure 8. SSTUx32868 Package (176-Ball NFBGA)

## 2.4.1 General Information

- 28-bit to 56-bit 1:2 configuration

- With parity check of Command and Address signals

- Integrates the functionality of two SSTUx32866 into a single device

- Configurable ball-out (mirror function)

- JEDEC Specifications:

- SSTU32868 (JESD82-14)

- SSTUA32S868/SSTUA32D868 (JESD82-17)

- SSTUB32868 (JESD82-26)

## Table 5. Available SSTUx32868-Compliant Devices From TI

| Package Options: ZRH | - Third generation, supports DDR2-400/533/667/800 - Propagation delay t <sub>pdm</sub> 1.1 ns–1.5 ns - Fully backward-compatible - Supports industrial temperature range (-40°C–85°C) - Top marking: SB868 |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | <ul><li>Same as 74SSTUB32868 but with higher drive strength and slew rate</li><li>Top marking: SB868A</li></ul>                                                                                            |

www.ti.com Register Overview

## 2.5 SSTUx32869

Figure 9. SSTUx32869 Package (150-Ball TFBGA)

## 2.5.1 General Information

- 14-bit to 28-bit 1:2 configuration (no 1:1 mode available)

- With parity check of Command and Address signals

- Same as SSTUx32866, but with 50% more dynamic drive strength

- No mirror function

- Fits on VLP DIMMs

- JEDEC Specifications:

- SSTU32S869/SSTU32D869 (JESD82-12)

- SSTUB32869 (JESD82-27)

PLL Overview www.ti.com

## 3 PLL Overview

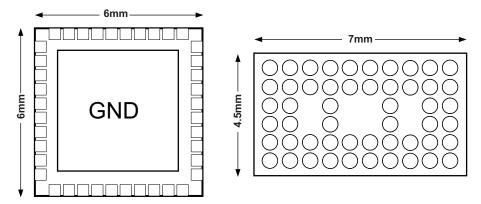

## 3.1 CUx877

Figure 10. CUx877 Package (40-Pad QFN and 52-Ball BGA)

## 3.1.1 General Information

- 1:10 PLL clock buffer

- External feedback loop for synchronizing outputs to inputs (zero delay, See application report SCAA087)

- Two package options specified

- JEDEC specifications

- CU877 (JESD82-8)

- CUA877/CU2A877 (JESD82-18)

## Table 6. Available CUx877-Compliant Devices From TI

| CDCU877<br>Package Options: RHA, RTB, GQL,<br>ZQL | <ul> <li>First generation, supports DDR2-400 and DDR2-533</li> <li>Supports industrial temperature range (-40°C-85°C)</li> <li>Top marking: CDCU877</li> </ul> |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDCU877A Package Options: RHA, RTB, GQL, ZQL      | Basically same as CDCU877     Only difference: VOX is on average 30 mV lower compared to CDCU877 (for the same application)     Top marking: CDCU877A          |

| CDCU877B<br>Package Options: ZQL                  | <ul><li>Supports DDR2-400/533/667</li><li>Supports industrial temperature range (-40°C–85°C)</li><li>Top marking: CDCU877B</li></ul>                           |

| CDCUA877<br>Package Options: ZQL                  | <ul><li>Supports DDR2-400/533/667/800</li><li>Supports industrial temperature range (-40°C–85°C)</li><li>Top marking: CDCUA877</li></ul>                       |

| CDCU2A877<br>Package Options: ZQL                 | <ul><li>Same as CDCUA877, but with higher output drive</li><li>Top marking: CDCUA877</li></ul>                                                                 |

12

# 4 Recommendations for New RDIMM Designs

Table 7. Buffer Recommendations for New RDIMMs

|         |              |                      |                |        | Recommended<br>PLL Buffer                    | Recommended Register Buffer              |                                          |                                          |

|---------|--------------|----------------------|----------------|--------|----------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| RawCard | Organization | Number of<br>SD-RAMs | Form<br>Factor | Parity | DDR2-400<br>DDR2-533<br>DDR2-667<br>DDR2-800 | DDR2-400<br>DDR2-533                     | DDR2-667                                 | DDR2-800                                 |

| Α       | 1Rx8         | 9 (planar)           | LP             | No     | CDCUA877                                     | SSTUB32864<br>SSTUB32866 <sup>(1)</sup>  | SSTUB32864<br>SSTUB32866 <sup>(1)</sup>  | SSTUB32864<br>SSTUB32866 <sup>(1)</sup>  |

| В       | 2Rx8         | 18 (planar)          | LP             | No     | CDCUA877                                     | SSTUB32864<br>SSTUB32866 <sup>(1)</sup>  | SSTUB32864<br>SSTUB32866 <sup>(1)</sup>  | SSTUB32864<br>SSTUB32866 <sup>(1)</sup>  |

| С       | 1Rx4         | 18 (planar)          | LP             | No     | CDCUA877                                     | SSTUB32864<br>SSTUB32866 <sup>(1)</sup>  | SSTUB32864<br>SSTUB32866 <sup>(1)</sup>  | SSTUB32864<br>SSTUB32866 <sup>(1)</sup>  |

| D       | 2Rx4         | 36 (stacked)         | LP             | Yes    | CDCUA877<br>CDCU2A877 <sup>(2)</sup>         | SSTUB32865<br>SSTUB32865A <sup>(2)</sup> | SSTUB32865<br>SSTUB32865A <sup>(2)</sup> | SSTUB32865<br>SSTUB32865A <sup>(2)</sup> |

| E       | 2Rx4         | 36 (stacked)         | LP             | Yes    | CDCUA877<br>CDCU2A877 <sup>(2)</sup>         | SSTUB32866                               |                                          |                                          |

| F       | 1Rx8         | 9 (planar)           | LP             | Yes    | CDCUA877                                     | SSTUB32866                               | SSTUB32866                               | SSTUB32866                               |

| G       | 2Rx8         | 18 (planar)          | LP             | Yes    | CDCUA877                                     | SSTUB32866                               | SSTUB32866                               | SSTUB32866                               |

| Н       | 1Rx4         | 18 (planar)          | LP             | Yes    | CDCUA877                                     | SSTUB32866                               | SSTUB32866                               | SSTUB32866                               |

| J       | 2Rx4         | 36 (planar)          | LP             | Yes    | CDCUA877<br>CDCU2A877 <sup>(2)</sup>         | SSTUB32866                               | SSTUB32866                               |                                          |

| К       | 2Rx4         | 36 (stacked)         | LP             | Yes    | CDCUA877<br>CDCU2A877 <sup>(2)</sup>         | SSTUB32868                               | SSTUB32868<br>SSTUB32868A                | SSTUB32868<br>SSTUB32868A <sup>(2)</sup> |

| L       | 2Rx4         | 36 (planar)          | LP             | Yes    | CDCUA877<br>CDCU2A877 <sup>(2)</sup>         | SSTUB32868                               | SSTUB32868<br>SSTUB32868A                | SSTUB32868<br>SSTUB32868A <sup>(2)</sup> |

| М       | 4Rx4         | 72 (stacked)         | LP             | Yes    | CDCU2A877                                    | SSTUB32868A                              | SSTUB32868A                              |                                          |

| N       | 4Rx8         | 36 (planar)          | LP             | Yes    | CDCUA877<br>CDCU2A877 <sup>(2)</sup>         | SSTUB32866<br>SSTUB32866A <sup>(2)</sup> | SSTUB32866<br>SSTUB32866A <sup>(2)</sup> |                                          |

| Р       | 2Rx4         | 36 (stacked)         | LP             | Yes    | CDCUA877<br>CDCU2A877 <sup>(2)</sup>         | SSTUB32868A                              | SSTUB32868A                              |                                          |

| R       | 1Rx8         | 9 (planar)           | VLP            | Yes    | CDCUA877                                     | SSTUB32866                               | SSTUB32866                               | SSTUB32866                               |

| Т       | 2Rx8         | 18 (planar)          | VLP            | Yes    | CDCUA877                                     | SSTUB32866                               | SSTUB32866                               | SSTUB32866                               |

| U       | 1Rx4         | 18 (planar)          | VLP            | Yes    | CDCUA877                                     | SSTUB32866                               | SSTUB32866                               | SSTUB32866                               |

| V       | 1Rx4         | 18 (planar)          | VLP            | Yes    | CDCUA877                                     | SSTUB32865                               | SSTUB32865                               |                                          |

| Υ       | 2Rx4         | 36 (stacked)         | VLP            | Yes    | CDCUA877<br>CDCU2A877 <sup>(2)</sup>         | SSTUB32865<br>SSTUB32865A <sup>(2)</sup> |                                          |                                          |

<sup>(1)</sup> SSTUB32866 has on on-die pulldown resistor for parity input. Therefore it can be used on RawCards which are designed for SSTUB32864 as well.

Proposed if DRAM input capacitance is on higher end of the specification for improved Signal Integrity

References www.ti.com

#### 5 References

#### Register Data Sheets

SN74SSTU32864, 25-Bit Configurable Registered Buffer With SSTL\_18 Inputs and Outputs (SCES434)

- SN74SSTU32864C, 25-Bit Configurable Registered Buffer With SSTL\_18 Inputs and Outputs (SCES542)

- 3. SN74SSTU32864D, 25-Bit Configurable Registered Buffer With SSTL\_18 Inputs and Outputs (SCES623)

- SN74SSTU32864E, 25-Bit Configurable Registered Buffer VWith SSTL\_18 Inputs and Outputs (SCAS802)

- 5. SN74SSTUB32864, 25-Bit Configurable Registered Buffer (SCAS791)

- 6. 74SSTUB32864A, 25-Bit Configurable Registered Buffer (SCAS838)

- 7. SN74SSTU32866, 25-Bit Configurable Registered Buffer With Address-Parity Test (SCES564)

- 8. SN74SSTU32866A, 25-Bit Configurable Registered Buffer With Address-Parity Test (SCAS803)

- 9. SN74SSTUB32866 25-Bit Configurable Registered Buffer With Address-Parity Test (SCAS792)

- 10. 74SSTUB32866A, 25-Bit Configurable Registered Buffer With Address-Parity Test (SCAS837)

- 11. 74SSTUB32865, 28-Bit to 56-Bit Registered Buffer with Address-Parity Test (SLAS537)

- 12. 74SSTUB32865A, 28-Bit to 56-Bit Registered Buffer With Address-Parity Test (SLAS562)

- 13. 74SSTUB32868, 28-Bit to 56-Bit Registered Buffer With Address-Parity Test (SCAS835)

- 14. 74SSTUB32868A, 28-Bit to 56-Bit Registered Buffer With Address-Parity Test (SCAS846)

#### PLL Data Sheets

- 1. CDCU877/CDCU877A, 1.8-V Phase Lock Loop Clock Driver (SCAS688)

- 2. CDCU877B, 1.8-V Phase Lock Loop Clock Driver (SCAS801)

- 3. CDCUA877, 1.8-V Phase Lock Loop Clock Driver (SCAS769)

- 4. CDCU2A877, 1.8-V Phase Lock Loop Clock Driver (SCAS827)

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com DLP® Products Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Military Interface www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated