# Application Clip

### SN74CBT34X245 Bus Switch Specially Designed for Hot Plugging ATA RAID Hard Disk

### **Overview of ATA/EIDE**

By far, the most popular interface used in modern hard disks is the one most commonly known as IDE. This interface is also known by a truly staggering variety of other names such as ATA, ATA/ATAPI, EIDE, ATA-2, Fast ATA, ATA-3, Ultra ATA, Ultra DMA and many more.

With a data bus width of 16 bits, the ATA/EIDE bus speeds are grouped into three operating frequencies: 66 MBps, 100 MBps and 133 MBps.

### **ATA/EIDE Pin Configuration**

| Drive Reset                       | 1  | 2  | Ground                    |

|-----------------------------------|----|----|---------------------------|

| Data Bit 7                        | 3  | 4  | Data Bit 8                |

| Data Bit 6                        | 5  | 6  | Data Bit 9                |

| Data Bit 5                        | 7  | 8  | Data Bit 10               |

| Data Bit 4                        | 9  | 10 | Data Bit 11               |

| Data Bit 3                        | 11 | 12 | Data Bit 12               |

| Data Bit 2                        | 13 | 14 | Data Bit 13               |

| Data Bit 1                        | 15 | 16 | Data Bit 14               |

| Data Bit 0                        | 17 | 18 | Data Bit 15               |

| Ground                            | 19 | 20 | Key (Pin Removed)         |

| DMA Request                       | 21 | 22 | Ground                    |

| I/O Write                         | 23 | 24 | Ground                    |

| I/O Read                          | 25 | 26 | Ground                    |

| I/O Channel Ready                 | 27 | 28 | Spindle Sync/Cable Select |

| DMA Acknowledge                   | 29 | 30 | Ground                    |

| Interrupt Request                 | 31 | 32 | 16 bit I/O                |

| Drive Address Bus 1               | 33 | 34 | Passed Diagnostic         |

| Drive Address Bus 0               | 35 | 36 | Drive Address Bus 2       |

| Drive Chip Select 0               | 37 | 38 | Drive Chip Select 1       |

| <b>Drive Active/Slave Present</b> | 39 | 40 | Ground                    |

|                                   |    |    |                           |

The switching level of the ATA/EIDE bus is based on a 5-V supply and is compatible with 5V TTL.

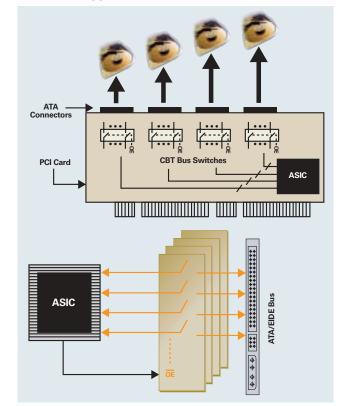

Because the IDE bus standard does not include hot plugging features (the capability to insert or remove cards without causing damage to the system and without having to disable the power), most designers use external bus switches to isolate the controller from the hard disk.

To eliminate additional delays that will impact system performance using standard logic buffers, near-zero delay bus switches are used to transmit data along the cable. For hot plug capability, all 32 bits used for data and control signaling need to be isolated before withdrawal or insertion of the hard disk.

The requirements of an ATA RAID system are such that the hard disk can be inserted or withdrawn from the bus or connector. To meet these needs, the CBT Bus Switch can provide the isolation by switching off during hot plugging through the use of the Output Enable (OE) pin.

### **CBT in ATA Raid Application**

#### **For More Information**

Product Folder: www.ti.com/sc/device/SN74CBT34X245 www.ti.com/sc/device/SN74CBT16245

Data Sheet: www-s.ti.com/sc/techlit/scds089c www-s.ti.com/sc/techlit/scds070c

CBT Bus Switch Home Page: www.ti.com/signalswitches

For up-to-date information to support your design and development needs, visit: **support.ti.com**

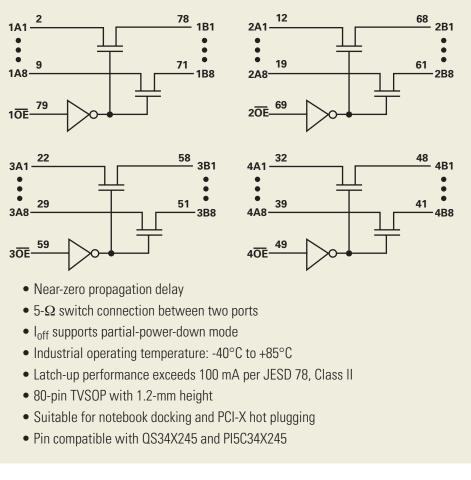

## SN74CBT34X245 Bus Switch

### **CBT Bus Switch**

TI CBT Bus Switch family is very fast and designed for hot plug and live insertion applications. The CBT product family provides many product options available in varying bit configurations.

### **Product Pin Configuration**

| NC*            | 1        | U | 80       | ] v <sub>cc</sub>        |

|----------------|----------|---|----------|--------------------------|

| 1A1            | 2        |   | 79       |                          |

| 1A2            | 3        |   | 78       | 1B1                      |

| 1A3            | 4        |   | 77       | 1B2                      |

| 1A4 [          | 5        |   | 76       | 1B3                      |

| 1A5            | 6        |   | 75       | 1B4                      |

| 1A6 🛛          | 7        |   | 74       | 1B5                      |

| 1A7 🛛          | 8        |   | 73       | 1B6                      |

| 1A8 🛛          | 9        |   | 72       | [ 1B7                    |

| GND [          | 10       |   | 71       | ] 1B8                    |

| NC*[           | 11       |   | 70       | V <sub>cc</sub>          |

| 2A1 [          | 12       |   | 69       | ] 2 <u>0</u> E           |

| 2A2 [          | 13       |   | 68       | ] 2B1                    |

| 2A3 [          | 14       |   | 67       | ] 2B2                    |

| 2A4 [          | 15       |   | 66       | ] 2B3                    |

| 2A5 [          | 16       |   | 65       | 2B4                      |

| 2A6 [          | 17       |   | 64       | 2B5                      |

| 2A7 [          | 18       |   | 63       | 2B6                      |

| 2A8 [          | 19       |   | 62       | 2B7                      |

| GND [          | 20       |   | 61       | 2B8                      |

| NC*            | 21       |   | 60       | V <sub>CC</sub>          |

| 3A1 [          | 22       |   | 59       | 3OE                      |

| 3A2 [          | 23       |   | 58       | ] 3B1                    |

| 3A3 [          | 24       |   | 57       | 3B2                      |

| 3A4 [          | 25       |   | 56       | ] 3B3                    |

| 3A5 [          | 26       |   | 55       | ] 3B4                    |

| 3A6 [          | 27       |   | 54       | 3B5                      |

| 3A7 [<br>3A8 [ | 28       |   | 53       | 3B6                      |

| GND            | 29       |   | 52       | ] 3B7<br>] 3B8           |

|                | 30       |   | 51       | 2                        |

| 4A1            | 31<br>32 |   | 50<br>49 | V <sub>CC</sub><br>  4OE |

| 4A2            | 32<br>33 |   | 49<br>48 | 4B1                      |

| 4A3 [          | 34       |   | 47       | 4B2                      |

| 4A4 [          | 35       |   | 46       | 4B3                      |

| 4A5 [          | 36       |   | 45       | 4B4                      |

| 4A6            | 37       |   | 44       | 4B5                      |

| 4A7 [          | 38       |   | 43       | 4B6                      |

| 4A8 [          | 39       |   | 42       | 4B7                      |

| GND            | 40       |   | 41       | <b>4B8</b>               |

|                |          |   |          |                          |

| Function Table<br>(Each 8-Bit Bus Switch) |                 |  |  |  |  |

|-------------------------------------------|-----------------|--|--|--|--|

| Input OE                                  | Function        |  |  |  |  |

| L                                         | A port = B port |  |  |  |  |

| Н                                         | Disconnect      |  |  |  |  |

### Logic Diagram (Positive Logic)

| Ordering Information                                                                                                                     |             |                       |                   |           |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------|-------------------|-----------|--|--|--|

| T <sub>A</sub> Package <sup>†</sup>                                                                                                      |             | Orderable Part Number | Top-Side Marking  |           |  |  |  |

| -40°C to 85°C                                                                                                                            | TVSOP (DBB) | Tape and reel         | SN74CBT34X245DBBR | CBT34X245 |  |  |  |

| <sup>†</sup> Note: Package drawings, standard packing quantities, thermal data, symbolization and PCB design guidelines are available at |             |                       |                   |           |  |  |  |

<sup>†</sup>Note: Package drawings, standard packing quantities, thermal data, symbolization and PCB design guidelines are available at www.ti.com/sc/package

#### Safe Harbor Statement

This publication contains forward-looking statements that involve a number of risks and uncertainties. These "forwardlooking statements" are intended to qualify for the safe harbor from liability established by the Private Scentrities Litigation Reform Act of 195. These forward-looking statements generally can be identified by phrases such as TI or its management "believes," "expects," "anticipates," "foresees," "forecasts," "estimates" or other words or phrases of similar import. Similarly, such statements herein that describe the company's products, business strategy, outlook, objectives, plans, intentions or goals also are forward-looking statements. All such forward-looking statements are subject to certain risks and uncertainties that could cause actual results to differ materially from those in forward-looking statements. Please refer to TI's most recent Form 10-K for more information on the risks and uncertainties that could materially affect future results of operations. We disclaim any intention or obligation to update any forward-looking statements as a result of developments occurring after the date of this publication.

\*NC = No internal connection.