# OMAP5912 Multimedia Processor Direct Memory Access (DMA) Support Reference Guide

Literature Number: SPRU755C March 2005

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated

## Preface

# **Read This First**

### About This Manual

This document describes the direct memory access (DMA) support of the OMAP5912 multimedia processor.

### Notational Conventions

This document uses the following conventions.

□ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

### **Related Documentation From Texas Instruments**

Documentation that describes the OMAP5912 devices, related peripherals, and other technical collateral, is available in the OMAP5912 Product Folder on TI's website: www.ti.com/omap5912.

### Trademarks

OMAP and the OMAP symbol are trademarks of Texas Instruments.

This page is intentionally left blank.

4 Direct Memory Access (DMA) Support

# Contents

| 1 | DMA   | Overvie | w                                                       | 13 |

|---|-------|---------|---------------------------------------------------------|----|

| 2 | GDM   | A Handl | ers                                                     | 13 |

| - | 2.1   |         | iDMA Handler                                            |    |

|   |       | 2.1.1   | MPU GDMA Handler Configuration                          |    |

|   | 2.2   | DSP G   | DMA Handler                                             |    |

|   | 2.3   |         | DMA Handler configuration                               |    |

| 3 | Syste |         | -                                                       |    |

| Ŭ | 3.1   |         | nal Description                                         |    |

|   | 0.1   | 3.1.1   | Logical Channel Types                                   |    |

|   |       | 3.1.2   | OMAP 3.2 System DMA Instances                           |    |

|   |       | 3.1.3   | Synchronized Channel                                    |    |

|   |       | 3.1.4   | Physical Ports                                          |    |

|   |       | 3.1.5   | Port Channel Scheduling                                 |    |

|   |       | 3.1.6   | Logical Channel Scheduling                              |    |

|   |       |         | Logical Channel Scheduling Scheme                       |    |

|   |       |         | Logical Channel Priorities                              |    |

|   |       | 3.1.7   | Logical Channel Interleaving For Synchronized Transfers | 39 |

|   |       | 3.1.8   | Linking Logical Channels                                |    |

|   |       | 3.1.9   | Logical Channel Preempting                              | 42 |

|   |       | 3.1.10  | Addressing Modes                                        | 43 |

|   |       |         | Data Alignment                                          | 44 |

|   |       |         | Constant Addressing Mode                                | 45 |

|   |       |         | Post-Incremented Addressing Mode                        | 45 |

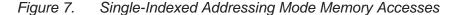

|   |       |         | Single-Indexed Addressing Mode                          | 46 |

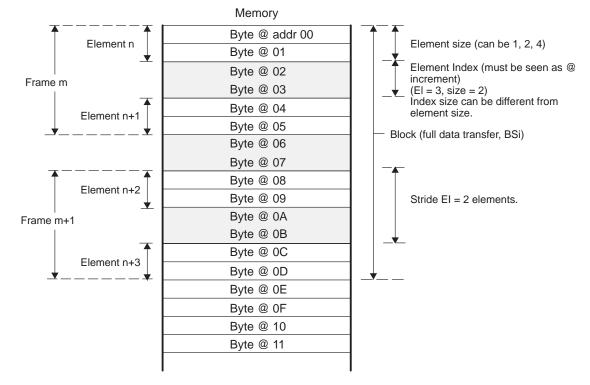

|   |       |         | Double-Indexed Addressing Mode                          | 48 |

|   |       | 3.1.11  | Data Packing and Bursting                               | 50 |

|   |       | 3.1.12  | Interrupt Generation                                    |    |

|   |       |         | System DMA Interrupt Mapping                            |    |

|   |       | 3.1.13  | DMA IDLE Modes                                          | 58 |

|   |       |         | Dynamic Idle Mode                                       |    |

|   |       |         | System IDLE Request                                     |    |

|   |       |         | DMA Debug State                                         |    |

|   |       | 3.1.15  | Other Logical Channel Features                          |    |

|   |       |         | Transparent Copy                                        |    |

|   |       |         | Constant Fill                                           |    |

|   |       |         | Rotation                                                | 62 |

|      | :       | 3.1.16  | Compatibility with OMAP 3.0 and 3.1                  | 62   |

|------|---------|---------|------------------------------------------------------|------|

|      |         |         | Autoinitialization of Logical Channels               |      |

|      |         |         | OMAP3.0/3.1 System DMA Interrupt Mapping Rule        |      |

|      |         |         | annel                                                |      |

|      |         |         | Display Logical Channel                              |      |

|      | :       | 3.2.2   | LCD Channel Addressing Modes                         |      |

|      |         |         | Source Address and Block Size Alignment              |      |

|      |         |         | Source Address Modes                                 |      |

|      |         |         | Post-Incremented Addressing Mode                     |      |

|      |         |         | Single-Indexed Addressing Mode                       |      |

|      |         |         | Double-Indexed Addressing Mode                       |      |

|      | :       | 3.2.3   | DMA LCD Channel Sharing Feature                      |      |

|      |         | 3.2.4   | DMA LCD Channel Rotation                             |      |

|      |         | 3.2.5   | DMA LCD Channel Autoinitialization Feature           | 73   |

|      |         |         | DMA_LCD_Disable/Bus Error Feature                    |      |

|      | :       | 3.2.7   | LCD Channel Usage Restrictions                       | 75   |

|      |         |         | Exclusive Blocks                                     | 75   |

|      |         |         | Both Blocks Must Belong to a Single Source           | 75   |

|      |         |         | LCD Registers Can Be Configured During a Transfer    | 75   |

|      | :       | 3.2.8   | LCD Channel OMAP 3.0/3.1 Compatible Mode Programming | 78   |

|      |         |         | Configuration Registers                              | 78   |

|      |         |         | Addressing Mode                                      | 79   |

|      |         |         | DMA LCD Channel Sharing Feature                      | 79   |

|      |         |         | Disabling Feature                                    | 79   |

|      |         |         | LCD Channel Restriction                              | 79   |

|      |         |         | DMA LCD Channel Autoinitialization Feature           | . 80 |

|      |         |         | DMA Configuration Registers I/O Space                | 80   |

|      | 3.3     | System  | DMA Registers                                        | 81   |

|      | :       | 3.3.1   | Summary DMA Global Registers                         | 82   |

|      | :       | 3.3.2   | Logical Channel Registers                            | 90   |

|      | :       | 3.3.3   | LCD Channel Dedicated Registers                      | 107  |

|      |         |         | DMA LCD Top Address B1 Registers                     | 115  |

|      |         |         | DMA LCD Bottom Address B1 Registers                  |      |

|      |         |         | DMA LCD Top Address B2 Registers                     |      |

|      |         |         | DMA LCD Bottom Address B2 Registers                  |      |

| Rov  | ision L | listory |                                                      | 122  |

| 1104 |         |         |                                                      | . 20 |

# Figures

| 1  | MPU GDMA Handler                                                        | 14 |

|----|-------------------------------------------------------------------------|----|

| 2  | DSP GDMA Handler                                                        | 22 |

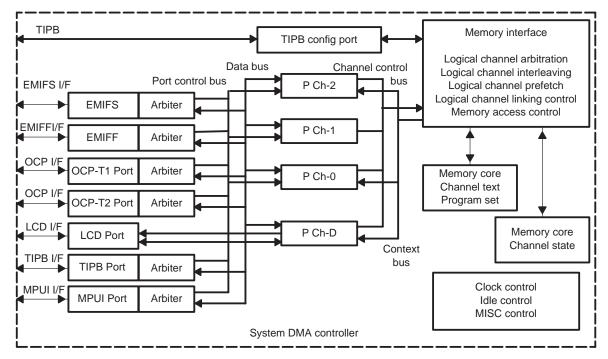

| 3  | System DMA Controller Simplified Block Diagram                          | 29 |

| 4  | Time Sharing Access on a System DMA Port                                | 36 |

| 5  | Logical Channel Interleaving on Channel Boundary With the Same Priority | 39 |

| 6  | Post-Incremented Addressing Mode Memory Accesses                        | 46 |

| 7  | Single-Indexed Addressing Mode Memory Accesses                          | 47 |

| 8  | Double-Indexed Addressing Mode Memory Accesses                          | 49 |

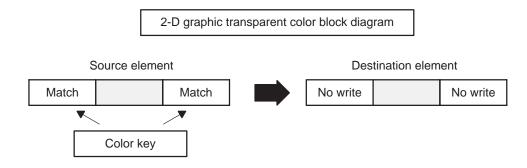

| 9  | 2-D Transparent Color Block Diagram                                     | 61 |

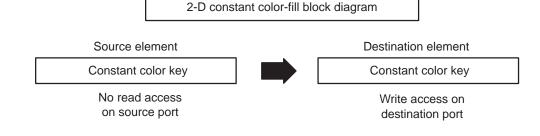

| 10 | 2-D Constant Color Fill Block Diagram                                   | 61 |

| 11 | DMA Packed Channel Status Register for Compatible Mode                  | 65 |

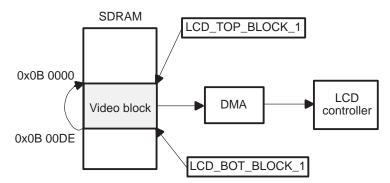

| 12 | LCD One-Block Mode Transfer Scheme                                      | 76 |

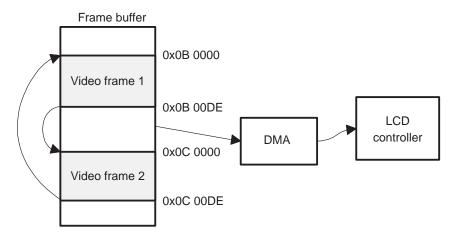

| 13 | LCD Dual-Block Mode Transfer Scheme                                     | 78 |

|    |                                                                         |    |

# **Tables**

| 1  | MPU GDMA Handler Mapping                                                                | . 14 |

|----|-----------------------------------------------------------------------------------------|------|

| 2  | MPU GDMA Handler Control Registers                                                      |      |

| 3  | Functional Multiplexing MPU DMA A Register (FUNC_MUX_MPU_DMA_A)                         | . 17 |

| 4  | Functional Multiplexing MPU DMA B Register (FUNC_MUX_MPU_DMA_B)                         |      |

| 5  | Functional Multiplexing MPU DMA C Register (FUNC_MUX_MPU_DMA_C)                         | . 18 |

| 6  | Functional Multiplexing MPU DMA D Register(FUNC_MUX_MPU_DMA_D)                          | . 19 |

| 7  | Functional Multiplexing MPU DMA E Register (FUNC_MUX_MPU_DMA_E)                         | . 20 |

| 8  | Functional Multiplexing MPU DMA F Register (FUNC_MUX_ARM_DMA_F)                         | . 20 |

| 9  | Functional Multiplexing MPU DMA G Register (FUNC_MUX_ARM_DMA_G)                         | . 21 |

| 10 | DSP GDMA Mapping                                                                        | . 22 |

| 11 | DSP DMA Handler Control Registers                                                       | . 23 |

| 12 | Functional Multiplexing DSP DMA A Register (FUNC_MUX_DSP_DMA_A)                         | . 24 |

| 13 | Functional Multiplexing DSP DMA B Register (FUNC_MUX_DSP_DMA_B)                         | . 25 |

| 14 | Functional Multiplexing DSP DMA C Register (FUNC_MUX_DSP_DMA_C                          | . 26 |

| 15 | Functional Multiplexing DSP DMA D Register (FUNC_MUX_DSP_DMA_D)                         | . 26 |

| 16 | Summary of Features Per Logical Channel Type (Without LCh-D)                            | . 31 |

| 17 | Associated Physical Channels Per Logical Channel Type                                   | . 32 |

| 18 | OMAP3.2 System DMA Supported Interface Port Type Table                                  | . 34 |

| 19 | Possible Data Transfer                                                                  | . 36 |

| 20 | Logical Channel Type Address Mode Summary                                               |      |

| 21 | Packing and Splitting Summary                                                           | . 51 |

| 22 | Channel Data Block to Transfer                                                          | . 54 |

| 23 | Channel Addresses and Access Types                                                      |      |

| 24 | Channel Data Block to Transfer                                                          | . 55 |

| 25 | Channel Addresses and Access Types                                                      | . 56 |

| 26 | Summary Table of Different Compatibility Modes                                          |      |

| 27 | Autoinitialization Configuration Bits Summary                                           |      |

| 28 | Interrupt Mapping per LCh for Both Compatible Modes                                     |      |

| 29 | Features Summary for LCh-D                                                              |      |

| 30 | Autoinitialization Bits Summary for LCD Channel in Noncompatible Mode                   | . 74 |

| 31 | Autoinitialization Configuration Bits Summary for LCD Channel in Compatible Mode        | . 80 |

| 32 | LCD Channel Register Mapping for OMAP 3.2 Respectively OMAP 3.0/3.1<br>Compatible Modes |      |

| 33 | DMA Global Control Registers                                                            |      |

| 34 | DMA Global Control Register (DMA_GCR)                                                   |      |

| 35 | DMA Software Compatible Register (DMA_GSCR)                                             |      |

Direct Memory Access (DMA) Support

8

SPRU755C

| 36 | DMA Software Reset Control Register (DMA_GRST)                         |     |

|----|------------------------------------------------------------------------|-----|

| 37 | DMA Hardware Version ID Register (DMA_HW_ID)                           |     |

| 38 | PCh-2 Version ID Register (DMA_PCh2_ID)                                |     |

| 39 | PCh-0 Version ID Register (DMA_PCh0_ID)                                |     |

| 40 | PCh-1 Version ID Register (DMA_PCh1_ID)                                |     |

| 41 | PCh-G Version ID Register (DMA_PChG_ID)                                |     |

| 42 | PCh-D Version ID Register (DMA_PChD_ID)                                |     |

| 43 | Global DMA Capability U Register 0 (DMA_ CAPS_0_U)                     |     |

| 44 | Global DMA Capability L Register 0 (DMA_ CAPS_0_L)                     |     |

| 45 | Global DMA Capability U Register 1 (DMA_CAPS_1_U)                      |     |

| 46 | Global DMA Capability L Register 1 (DMA_CAPS_1_L)                      |     |

| 47 | Global DMA Capability Register 2 (DMA_CAPS_2)                          |     |

| 48 | Global DMA Capability Register 3 (DMA_CAPS_3)                          |     |

| 49 | Global DMA Capability Register 4 (DMA_CAPS_4)                          |     |

| 50 | Physical Channel-x Status Registers (DMA_PCh2_SRDMA_PHhD_SR_0)         |     |

| 51 | DMA Logical Channel Configuration Registers                            |     |

| 52 | Channel Source Destination Parameters Register (DMA_CSDP)              |     |

| 53 | Data Types                                                             |     |

| 54 | DMA Channel Control Register (DMA_CCR)                                 |     |

| 55 | DMA Channel Interrupt Control Register(DMA_CICR)                       |     |

| 56 | DMA Channel Status Register (DMA_CSR)                                  |     |

| 57 | DMA Channel Source Start Address Lower Bits Register (DMA_CSSA_L)      |     |

| 58 | DMA Channel Source Start Address Upper Bits Register (DMA_CSSA_U)      |     |

| 59 | DMA Channel Destination Start Address Lower Bits Register (DMA_CDSA_L) |     |

| 60 | DMA Channel Destination Start Address Upper Bits Register (DMA_CDSA_U) |     |

| 61 | DMA Channel Element Number Register (DMA_CEN)                          |     |

| 62 | DMA Channel Frame Number Register (DMA_CFN)                            |     |

| 63 | DMA Channel Source Frame Index Register (DMA_CSFI)                     |     |

| 64 | DMA Channel Source Element Index Register (DMA_CSEI)                   |     |

| 65 | DMA Channel Source Element Index Register (DMA_CSAC)                   | 103 |

| 66 | DMA Channel Destination Address Counter Register (DMA_CDAC)            | 103 |

| 67 | DMA Channel Destination Element Index Register (DMA_CDEI)              | 103 |

| 68 | DMA Channel Destination Frame Index Register (DMA_CDFI)                | 104 |

| 69 | DMA COLOR Parameter Register (DMA_COLOR_L)                             | 104 |

| 70 | DMA COLOR Parameter Register (DMA_COLOR_U)                             | 105 |

| 71 | DMA Channel Control Register 2 (DMA_CCR2)                              | 105 |

| 72 | DMA Logical Channel Link Control Register (DMA_CLNK_CTRL)              | 106 |

| 73 | DMA Logical Channel Control Register (DMA_LCH_CTRL)                    | 107 |

| 74 | DMA Logical Channel Configuration Registers                            |     |

| 75 | DMA LCD Channel Source Destination Parameters Register (DMA_LCD_CSDP)  | 109 |

| 76 | DMA LCD Channel Control Register (DMA_LCD_CCR)                         | 110 |

| 77 | DMA LCD Control Register (DMA_LCD_CTRL)                                |     |

| 78 | DMA LCD Top Address B1 L Register (TOP_B1_L)                           | 116 |

| 79 | DMA LCD Top Address B1 U Register (TOP_B1_U)                           | 116 |

### Tables

| DMA LCD Bottom Address B1 L Register (BOT_B1_L)                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA LCD Bottom Address B1 U Register (BOT_B1_U)                | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Top Address B2 L Register (TOP_B2_L)                   | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Top Address B2 U Register (TOP_B2_U)                   | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Bottom Address B2 L Register (BOT_B2_L)                | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Bottom Address B2 U Register (BOT_B2_U)                | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Source Element Index B1 Register (DMA_LCD_SRC_EI_B1)   | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Source Frame Index B1 Register L (DMA_LCD_SRC_FI_B1_L) | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Source Frame Index B1 Register U (DMA_LCD_SRC_FI_B1_U) | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Source Element Index B2 Register (DMA_LCD_SRC_EI_B2)   | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Source Frame Index B2 Register L (DMA_LCD_SRC_FI_B2_L) | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Source Frame Index B2 Register U (DMA_LCD_SRC_FI_B2_U) | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Source Element Number B1 Register (DMA_LCD_SRC_EN_B1)  | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Source Frame Number B1 Register (DMA_LCD_SRC_FN_B1)    | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Source Element Number B2 Register (DMA_LCD_SRC_EN_B2)  | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Source Frame Number B2 Register (DMA_LCD_SRC_FN_B2)    | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA LCD Logical Channel Control Register (DMA_LCD_LCH_CTRL)    | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Document Revision History                                      | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                | DMA LCD Bottom Address B1 U Register (BOT_B1_U)<br>DMA LCD Top Address B2 L Register (TOP_B2_L)<br>DMA LCD Top Address B2 U Register (TOP_B2_U)<br>DMA LCD Bottom Address B2 L Register (BOT_B2_L)<br>DMA LCD Bottom Address B2 U Register (BOT_B2_U)<br>DMA LCD Source Element Index B1 Register (DMA_LCD_SRC_EI_B1)<br>DMA LCD Source Frame Index B1 Register L (DMA_LCD_SRC_FI_B1_L)<br>DMA LCD Source Frame Index B1 Register U (DMA_LCD_SRC_FI_B1_U)<br>DMA LCD Source Element Index B2 Register U (DMA_LCD_SRC_FI_B1_U)<br>DMA LCD Source Frame Index B2 Register L (DMA_LCD_SRC_FI_B2_L)<br>DMA LCD Source Frame Index B2 Register L (DMA_LCD_SRC_FI_B2_L)<br>DMA LCD Source Frame Index B2 Register U (DMA_LCD_SRC_FI_B2_U)<br>DMA LCD Source Element Number B1 Register (DMA_LCD_SRC_FN_B1)<br>DMA LCD Source Frame Number B2 Register (DMA_LCD_SRC_FN_B2)<br>DMA LCD Logical Channel Control Register (DMA_LCD_LCH_CTRL) |

# Examples

| 1 | Packing Enabled                                               | 53 |

|---|---------------------------------------------------------------|----|

| 2 | Packing and Burst Enabled                                     | 54 |

| 3 | LCD Transfer: EMIFF (SDRAM) $\rightarrow$ LCD, One Block      | 75 |

| 4 | LCD Transfer: OCP_T1 (Test RAM) $\rightarrow$ LCD, Two Blocks | 77 |

This page is intentionally left blank.

12 Direct Memory Access (DMA) Support

This document describes the direct memory access (DMA) support of the OMAP5912 multimedia processor.

### 1 DMA Overview

The processor has two DMAs:

- □ The system DMA is embedded in OMAP3.2. It handles DMA transfers associated with MPU and shared peripherals.

- □ The DSP DMA is embedded in OMAP3.2. It handles DMA transfers associated with DSP peripherals. See the *OMAP5910/5912 Multimedia Processor DSP Subsystem Reference Guide* (SPRU890) for information on the DSP DMA.

The system DMA can support up to 31 hardware DMA requests. The DSP DMA supports 19 hardware DMA requests.

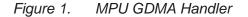

In OMAP5912, up to 56 different hardware DMA requests can be generated by MPU and shared peripherals. An embedded crossbar, called MPU GDMA handler, allows mapping any of these 56 requests to any of 31 the system DMA request.

Similarly, DSP and shared peripherals can generate up to 28 hardware DMA requests. An embedded crossbar, called DSP GDMA handler allows mapping any of these 28 requests to any of the 19 DSP DMA requests.

Both MPU and DSP GDMA handlers are configured through registers implemented in the configuration module.

### 2 GDMA Handlers

MPU and DSP peripherals DMA request mapping is configurable through two blocks called GDMA handlers. MPU GDMA handler is described in section 2.1. DSP GDMA handler is described in section 2.2.

### 2.1 MPU GDMA Handler

The MPU and shared peripherals control up to 56 DMA requests, whereas the system DMA can handle only 31 DMA requests.

The GDMA handler acts as a crossbar so that each of the incoming DMA requests can be remapped to any of the system DMA requests.

The mapping of each DMA request is done through the FUNC\_MPU\_DMA\_x registers located in the configuration module.

SPRU755C

A 6-bit field is associated with each system channel so that any incoming DMA request is remapped to the proper system DMA request. See Figure 1 for a description of the MPU GDMA handler.

The default configuration after reset ensures compatibility with the previous OMAP5912 generation. Programmers have flexibility to remap up to 31 requests according to the application task requirements. Table 1 describes the mapping between MPU and shared peripherals DMA requests and the MPU GDMA handler inputs.

Table 1.

MPU GDMA Handler Mapping

| MPU GDMA Handler Input Line | Peripheral Request     |

|-----------------------------|------------------------|

| REQ1                        | MCSI1 TX               |

| REQ2                        | MCSI1 RX               |

| REQ3                        | I <sup>2</sup> C RX    |

| REQ4                        | I <sup>2</sup> C TX    |

| REQ5                        | External DMA request 0 |

| REQ6                        | External DMA request 1 |

| REQ7                        | μWire TX               |

| REQ8                        | McBSP1 DMA TX          |

| REQ9                        | McBSP1 DMA RX          |

| REQ10                       | McBSP3 DMA TX          |

| MPU GDMA Handler Input Line | Peripheral Request     |

|-----------------------------|------------------------|

| REQ11                       | McBSP3 DMA RX          |

| REQ12                       | UART1 TX               |

| REQ13                       | UART1 RX               |

| REQ14                       | UART2 TX               |

| REQ15                       | UART2 RX               |

| REQ16                       | McBSP2 TX              |

| REQ17                       | McBSP2 RX              |

| REQ18                       | UART3 TX               |

| REQ19                       | UART3 RX               |

| REQ20                       | Camera IF RX           |

| REQ21                       | MMC/SDIO1 TX           |

| REQ22                       | MMC/SDIO1 RX           |

| REQ24                       | IRQ_LCD_LINE           |

| REQ26                       | USB W2FC RX0           |

| REQ27                       | USB W2FC RX1           |

| REQ28                       | USB W2FC RX2           |

| REQ29                       | USB W2FC TX0           |

| REQ30                       | USB W2FC TX1           |

| REQ31                       | USB W2FC TX2           |

| REQ33                       | SPI TX                 |

| REQ34                       | SPI RX                 |

| REQ38                       | CMT-APE TX (channel 0) |

| REQ39                       | CMT-APE RV (channel 0) |

| REQ40                       | CMT-APE TX (channel 1) |

| REQ41                       | CMT-APE RV (channel 1) |

| REQ42                       | CMT-APE TX (channel 2) |

### Table 1. MPU GDMA Handler Mapping (Continued)

SPRU755C

Direct Memory Access (DMA) Support

#### **GDMA Handlers**

| MPU GDMA Handler Input Line | Peripheral Request     |

|-----------------------------|------------------------|

| REQ43                       | CMT-APE RV (channel 2) |

| REQ44                       | CMT-APE TX (channel 3) |

| REQ45                       | CMT-APE RV (channel 3) |

| REQ46                       | CMT-APE TX (channel 4) |

| REQ47                       | CMT-APE RV (channel 4) |

| REQ48                       | CMT-APE TX (channel 5) |

| REQ49                       | CMT-APE RV (channel 5) |

| REQ50                       | CMT-APE TX (channel 6) |

| REQ51                       | CMT-APE RV (channel 6) |

| REQ52                       | CMT-APE TX (channel 7) |

| REQ53                       | CMT-APE RV (channel 7) |

| REQ54                       | MMC/SDIO2 TX           |

| REQ55                       | MMC/SDIO2 RX           |

| REQ58                       | Unconnected            |

| REQ59                       | Unconnected            |

| REQ60                       | Unconnected            |

| REQ61                       | Unconnected            |

| REQ62                       | Unconnected            |

| REQ63                       | Unconnected            |

| REQ64                       | Unconnected            |

MPU GDMA Handler Mapping (Continued) Table 1.

#### 2.1.1 **MPU GDMA Handler Configuration**

The mapping of the system DMA requests is done through the GDMA registers (shown in Table 2), which are implemented in the configuration module. Table 3 through Table 9 describe the register bits.

The values programmed into these registers represent a zero-based numbering of the DMA request. Thus, peripheral request number n is programmed as *n-1*, not *n*.

Direct Memory Access (DMA) Support

Table 2. MPU GDMA Handler Control Registers

| Base Address = 0xFFFE 1000 |                                                    |     |        |  |

|----------------------------|----------------------------------------------------|-----|--------|--|

| Name                       | Description                                        | R/W | Offset |  |

| FUNC_MUX_MPU_DMA_A         | Controls mapping for system DMA requests 1 to 5.   | R/W | 0xEC   |  |

| FUNC_MUX_MPU_DMA_B         | Controls mapping for system DMA requests 6 to 10.  | R/W | 0xF0   |  |

| FUNC_MUX_MPU_DMA_C         | Controls mapping for system DMA requests 11 to 15. | R/W | 0xF4   |  |

| FUNC_MUX_MPU_DMA_D         | Controls mapping for system DMA requests 16 to 20. | R/W | 0xF8   |  |

| FUNC_MUX_ARM_DMA_E         | Controls mapping for system DMA requests 21 to 25. | R/W | 0xFC   |  |

| FUNC_MUX_ARM_DMA_F         | Controls mapping for system DMA requests 26 to 30. | R/W | 0x100  |  |

| FUNC_MUX_ARM_DMA_G         | Controls mapping for system DMA request 31.        | R/W | 0x104  |  |

Table 3.

Functional Multiplexing MPU DMA A Register (FUNC\_MUX\_MPU\_DMA\_A)

| Base Address = 0xFFFE 1000, Offset Address = 0xEC |                     |                                                                                                                                          |     |       |

|---------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| Bit                                               | Name                | Function                                                                                                                                 | R/W | Reset |

| 31:30                                             | RESERVED            | Reserved.                                                                                                                                | R/W | 0x0   |

| 29:24                                             | CONF_ARM_DMA_REQ_05 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(5). $n$ is between 0 and 55.           | R/W | 0x04  |

| 23:18                                             | CONF_ARM_DMA_REQ_04 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(4). $n$ is between 0 and 55.           | R/W | 0x03  |

| 17:12                                             | CONF_ARM_DMA_REQ_03 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(3). $n$ is between 0 and 55.           | R/W | 0x02  |

| 11:6                                              | CONF_ARM_DMA_REQ_02 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(2). $n$ is between 0 and 55.           | R/W | 0x01  |

| 5:0                                               | CONF_ARM_DMA_REQ_01 | Writing value <i>n</i> in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(1). <i>n</i> is between 0 and 55. | R/W | 0x00  |

This register controls the system DMA crossbar and defines the mapping of MPU peripheral DMA requests 1 through 5 to system DMA requests. 56 MPU peripheral DMA requests can be mapped to the 31 system DMA controller requests. The values programmed in the register represent a zero-based numbering of peripheral DMA\_REQn (starting with 1). Peripheral DMA\_REQ1

is written as zero. For example, if bits 5:0 are equal to 3, then n+1 = 4, and DMA MPU peripheral request source 4 ( $I^{2}C TX$ ) is connected to system DMA\_REQ(1).

| Base Address = 0xFFFE 1000, Offset Address = 0xF0 |                     |                                                                                                                                 |     |       |

|---------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| Bit                                               | Name                | Function                                                                                                                        | R/W | Reset |

| 31:30                                             | RESERVED            | Reserved.                                                                                                                       | R/W | 0x0   |

| 29:24                                             | CONF_ARM_DMA_REQ_10 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(10). $n$ is between 0 and 55. | R/W | 0x09  |

| 23:18                                             | CONF_ARM_DMA_REQ_09 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(9). $n$ is between 0 and 55.  | R/W | 0x08  |

| 17:12                                             | CONF_ARM_DMA_REQ_08 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(8). $n$ is between 0 and 55.  | R/W | 0x07  |

| 11:6                                              | CONF_ARM_DMA_REQ_07 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(7). $n$ is between 0 and 55.  | R/W | 0x06  |

| 5:0                                               | CONF_ARM_DMA_REQ_06 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(6). $n$ is between 0 and 55.  | R/W | 0x05  |

Table 4.

Functional Multiplexing MPU DMA B Register (FUNC\_MUX\_MPU\_DMA\_B)

| Table 5. | Functional Multiplexing MPU DMA C Register |

|----------|--------------------------------------------|

|          | (FUNC_MUX_MPU_DMA_C)                       |

|       | Base Address = 0xFFFE 1000, Offset Address = 0xF4 |                                                                                                                                 |     |       |

|-------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| Bit   | Name                                              | Function                                                                                                                        | R/W | Reset |

| 31:30 | RESERVED                                          | Reserved.                                                                                                                       | R/W | 0x0   |

| 29:24 | CONF_ARM_DMA_REQ_15                               | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(15). $n$ is between 0 and 55. | R/W | 0x0E  |

Table 5.Functional Multiplexing MPU DMA C Register<br/>(FUNC\_MUX\_MPU\_DMA\_C) (Continued)

| Bit   | Name                | Function                                                                                                                        | R/W | Reset |

|-------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 23:18 | CONF_ARM_DMA_REQ_14 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(14). $n$ is between 0 and 55. | R/W | 0x0D  |

| 17:12 | CONF_ARM_DMA_REQ_13 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(13). $n$ is between 0 and 55. | R/W | 0x0C  |

| 11:6  | CONF_ARM_DMA_REQ_12 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(12). $n$ is between 0 and 55. | R/W | 0x0B  |

| 5:0   | CONF_ARM_DMA_REQ_11 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(11). $n$ is between 0 and 55. | R/W | 0x0A  |

Table 6.

Functional Multiplexing MPU DMA D Register(FUNC\_MUX\_MPU\_DMA\_D)

| Base Address = 0xFFFE 1000, Offset Address = 0xF8 |                     |                                                                                                                                 |     |       |

|---------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| Bit                                               | Name                | Function                                                                                                                        | R/W | Reset |

| 31:30                                             | RESERVED            | Reserved.                                                                                                                       | R/W | 0x0   |

| 29:24                                             | CONF_ARM_DMA_REQ_20 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(20). $n$ is between 0 and 55. | R/W | 0x13  |

| 23:18                                             | CONF_ARM_DMA_REQ_19 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(19). $n$ is between 0 and 55. | R/W | 0x12  |

| 17:12                                             | CONF_ARM_DMA_REQ_18 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(18). $n$ is between 0 and 55. | R/W | 0x11  |

| 11:6                                              | CONF_ARM_DMA_REQ_17 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(17). $n$ is between 0 and 55. | R/W | 0x10  |

| 5:0                                               | CONF_ARM_DMA_REQ_16 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(16). $n$ is between 0 and 55. | R/W | 0x0F  |

# Table 7.Functional Multiplexing MPU DMA E Register<br/>(FUNC\_MUX\_MPU\_DMA\_E)

|       | Base Address = 0xFFFE 1000, Offset Address = 0xFC |                                                                                                                                 |     |       |  |

|-------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-------|--|

| Bit   | Name                                              | Function                                                                                                                        | R/W | Reset |  |

| 31:30 | RESERVED                                          | Reserved.                                                                                                                       | R/W | 0x0   |  |

| 29:24 | CONF_ARM_DMA_REQ_25                               | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(25). $n$ is between 0 and 55. | R/W | 0x18  |  |

| 23:18 | CONF_ARM_DMA_REQ_24                               | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(24). $n$ is between 0 and 55. | R/W | 0x17  |  |

| 17:12 | CONF_ARM_DMA_REQ_23                               | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(23). $n$ is between 0 and 55. | R/W | 0x16  |  |

| 11:6  | CONF_ARM_DMA_REQ_22                               | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(22). $n$ is between 0 and 55. | R/W | 0x15  |  |

| 5:0   | CONF_ARM_DMA_REQ_21                               | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(21). $n$ is between 0 and 55. | R/W | 0x14  |  |

# Table 8.Functional Multiplexing MPU DMA F Register<br/>(FUNC\_MUX\_ARM\_DMA\_F)

| Base Address = 0xFFFE 1000, Offset Address = 0x100 |                     |                                                                                                                                 |     |       |

|----------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| Bit                                                | Name                | Function                                                                                                                        | R/W | Reset |

| 31:30                                              | RESERVED            | Reserved.                                                                                                                       | R/W | 0x0   |

| 29:24                                              | CONF_ARM_DMA_REQ_30 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(30). $n$ is between 0 and 55. | R/W | 0x1D  |

| 23:18                                              | CONF_ARM_DMA_REQ_29 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(29). $n$ is between 0 and 55. | R/W | 0x1C  |

| 17:12                                              | CONF_ARM_DMA_REQ_28 | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(28). $n$ is between 0 and 55. | R/W | 0x1B  |

|      | (rente_mex_nnm_p) (continued) |                                                                                                                                 |     |       |

|------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| Bit  | Name                          | Function                                                                                                                        | R/W | Reset |

| 11:6 | CONF_ARM_DMA_REQ_27           | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(27). $n$ is between 0 and 55. | R/W | 0x1A  |

| 5:0  | CONF_ARM_DMA_REQ_26           | Writing value $n$ in this register maps DMA request source $n+1$ to system DMA controller DMA_REQ(26). $n$ is between 0 and 55. | R/W | 0x19  |

Table 8.Functional Multiplexing MPU DMA F Register<br/>(FUNC\_MUX\_ARM\_DMA\_F) (Continued)

Table 9.

Functional Multiplexing MPU DMA G Register (FUNC\_MUX\_ARM\_DMA\_G)

| Base Address = 0xFFFE 1000, Offset Address = 0x104 |                     |                                                                                                                                          |     |           |

|----------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| Bit                                                | Name                | Function                                                                                                                                 | R/W | Reset     |

| 31:6                                               | RESERVED            | Reserved.                                                                                                                                | R/W | 0x0000000 |

| 5:0                                                | CONF_ARM_DMA_REQ_31 | Writing value $n$ in this register maps<br>DMA request source $n+1$ to system<br>DMA controller DMA_REQ(31). $n$ is<br>between 0 and 55. | R/W | 0x1E      |

### 2.2 DSP GDMA Handler

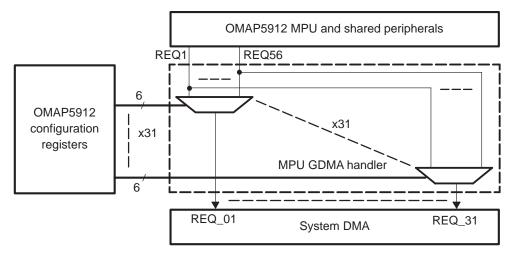

The various DSP and shared peripherals control up to 28 DMA requests, whereas the DSP DMA in the OMAP3.2 can handle only 19 DMA requests.

The DSP GDMA handler acts as a crossbar so that each of the incoming DMA requests can be remapped to any of the DSP DMA requests.

The mapping of each DMA request is done through the FUNC\_DSP\_DMA\_x registers located in the configuration module.

A 5-bit field is associated with each DSP channel so that any incoming DMA request is remapped to the proper DSP DMA request.

The default configuration from reset ensures compatibility with the previous OMAP5912 generation. Programmers have the flexibility to remap up to 19 requests according to the application task requirements. See Figure 2 for a description of the DSP GDMA handler and Table 10 for DSP GDMA mapping.

### Figure 2. DSP GDMA Handler

| DSP GDMA Handler Input Line | Peripheral Request  |

|-----------------------------|---------------------|

| REQ1                        | MCSI1 TX            |

| REQ2                        | MCSI1 RX            |

| REQ3                        | MCSI2 TX            |

| REQ4                        | MCSI2 RX            |

| REQ5                        | MMC/SDIO2 TX        |

| REQ6                        | MMC/SDIO2 RX        |

| REQ7                        | Reserved            |

| REQ8                        | McBSP1 TX           |

| REQ9                        | McBSP1 RX           |

| REQ10                       | McBSP3 TX           |

| REQ11                       | McBSP3 RX           |

| REQ12                       | UART1 TX            |

| REQ13                       | UART1 RX            |

| REQ14                       | UART2 TX            |

| REQ15                       | UART2 RX            |

| REQ16                       | I <sup>2</sup> C RX |

| REQ17                       | I <sup>2</sup> C TX |

| DSP GDMA Handler Input Line | Peripheral Request     |

|-----------------------------|------------------------|

| REQ18                       | UART3 TX               |

| REQ19                       | UART3 RX               |

| REQ20                       | CMT-APE TX (channel 1) |

| REQ21                       | CMT-APE RV (channel 1) |

| REQ22                       | CMT-APE TX (channel 2) |

| REQ23                       | CMT-APE RV (channel 2) |

| REQ25                       | SPI TX                 |

| REQ26                       | SPI RX                 |

| REQ27                       | McBSP2 TX              |

| REQ28                       | McBSP2 RX              |

| REQ29                       | Unconnected            |

| REQ30                       | Unconnected            |

| REQ31                       | Unconnected            |

| REQ32                       | Unconnected            |

Table 10. DSP GDMA Mapping (Continued)

### 2.3 DSP GDMA Handler configuration

The mapping of the DSP DMA requests is done through the FUNC\_MUX\_DSP\_DMA\_X registers (shown in Table 11), which are implemented in the configuration module. Table 12 through Table 15 describe the register bits.

The values programmed into these registers represent a zero-based numbering of the DMA request. Thus, peripheral request number n is programmed as n-1, not n.

| Table 11. | DSP DMA | Handler Control | ol Registers |

|-----------|---------|-----------------|--------------|

|-----------|---------|-----------------|--------------|

| Base Address = 0xFFFE 1000 |                                                |     |        |  |  |

|----------------------------|------------------------------------------------|-----|--------|--|--|

| Name                       | Description                                    | R/W | Offset |  |  |

| FUNC_MUX_DSP_DMA_A         | Controls mapping for DSP DMA requests 1 to 6   | R/W | 0xD0   |  |  |

| FUNC_MUX_DSP_DMA_B         | Controls mapping for DSP DMA requests 7 to 12  | R/W | 0xD4   |  |  |

| FUNC_MUX_DSP_DMA_C         | Controls mapping for DSP DMA requests 13 to 18 | R/W | 0xD8   |  |  |

| FUNC_MUX_DSP_DMA_D         | Controls mapping for DSP DMA request 19        | R/W | 0xDC   |  |  |

SPRU755C

Direct Memory Access (DMA) Support

| Table 12. | Functional Multiplexing I | DSP DMA A Register ( | (FUNC_MUX_DSP_DMA_A) |

|-----------|---------------------------|----------------------|----------------------|

|           |                           |                      |                      |

|       | Base Address = 0xFFFE 1000, Offset Address = 0xD0 |                                                                                                                                       |     |       |  |

|-------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--|

| Bit   | Name                                              | Function                                                                                                                              | R/W | Reset |  |

| 31:30 | RESERVED                                          | Reserved                                                                                                                              | R/W | 0x0   |  |

| 29:25 | CONF_DSP_DMA_REQ_06                               | Writing value $n$ in this register maps DMA request source $n+1$ to DSP DMA controller DMA_REQ(6). $n$ is between 0 and 27.           | R/W | 0x05  |  |

| 24:20 | CONF_DSP_DMA_REQ_05                               | Writing value $n$ in this register maps DMA request source $n+1$ to DSP DMA controller DMA_REQ(5). $n$ is between 0 and 27.           | R/W | 0x04  |  |

| 19:15 | CONF_DSP_DMA_REQ_04                               | Writing value $n$ in this register maps DMA request source $n+1$ to DSP DMA controller DMA_REQ(4). $n$ is between 0 and 27.           | R/W | 0x03  |  |

| 14:10 | CONF_DSP_DMA_REQ_03                               | Writing value $n$ in this register maps DMA request source $n+1$ to DSP DMA controller DMA_REQ(3). $n$ is between 0 and 27.           | R/W | 0x02  |  |

| 9:5   | CONF_DSP_DMA_REQ_02                               | Writing value $n$ in this register maps DMA request source $n+1$ to DSP DMA controller DMA_REQ(2). $n$ is between 0 and 27.           | R/W | 0x01  |  |

| 4:0   | CONF_DSP_DMA_REQ_01                               | Writing value <i>n</i> in this register maps DMA request source $n+1$ to DSP DMA controller DMA_REQ(1). <i>n</i> is between 0 and 27. | R/W | 0x00  |  |

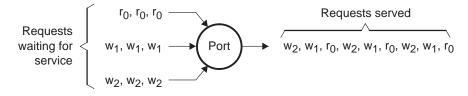

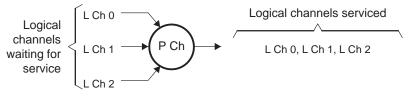

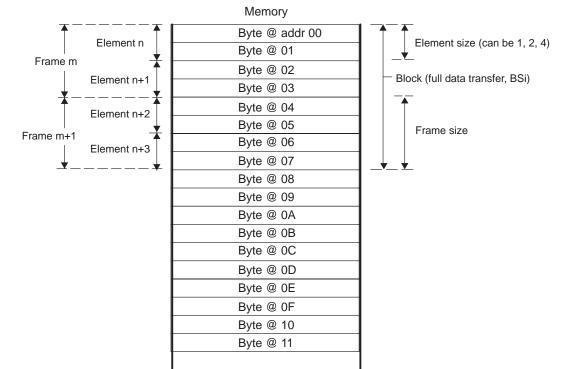

This register controls the DSP DMA crossbar and defines the mapping of DSP peripheral DMA requests 1 through 6 to OMAP3.2 DSP DMA requests. 28 DSP peripheral DMA requests can be mapped to the 19 DSP DMA controller requests. The values programmed in the register represent a zero-based numbering of DMA\_REQn (starting with 1). Thus, peripheral DMA\_REQ1 is written as zero. For example, if bits 4:0 are equal to 3, then n+1=4, and DSP DMA\_REQ(1) maps to DMA DSP peripheral request source 4 (MCSI2 RX).