# **KeyStone I Architecture Antenna Interface 2 (AIF2)**

# **User's Guide**

Literature Number: SPRUGV7E November 2010–Revised February 2015

# **Contents**

| Prefa | ce    |                                                                    | 28        |

|-------|-------|--------------------------------------------------------------------|-----------|

| 1     | Intro | duction                                                            | 30        |

|       | 1.1   | Purpose                                                            |           |

|       | 1.2   | Scope                                                              | 31        |

|       | 1.3   | Terminology                                                        | 31        |

|       |       | 1.3.1 Abbreviations and Acronyms                                   |           |

|       |       | 1.3.2 Definitions                                                  |           |

|       | 1.4   | Features                                                           |           |

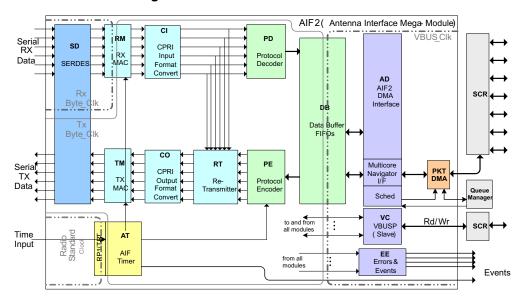

| 2     | Overv | view of AIF2 Hardware and Software Components                      | <b>37</b> |

| 3     | Radio | o Standard Requirements and AIF2 Handling                          | 40        |

|       | 3.1   | WCDMA Requirements and Handling                                    |           |

|       | 3.2   | OFDM Requirements and Handling (LTE FDD, LTE TDD, WiMax, TD-SCDMA) | 41        |

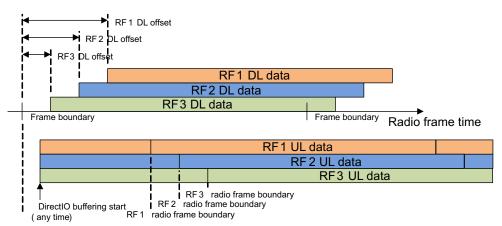

|       |       | 3.2.1 OFDM DMA                                                     | 41        |

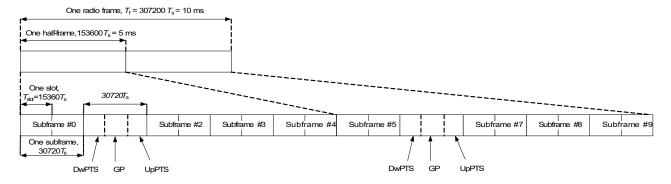

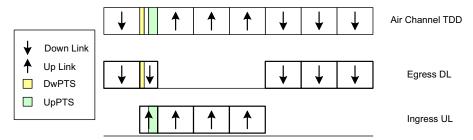

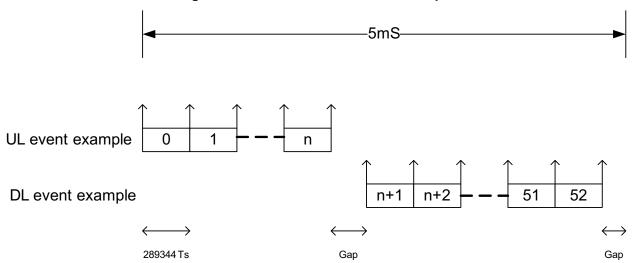

|       |       | 3.2.1.1 OFDM TDD DMA {LTE TDD, WiMax, TD-SCDMA}                    | 43        |

|       |       | 3.2.2 LTE                                                          | 43        |

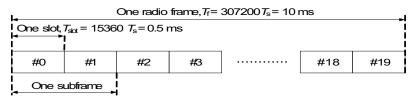

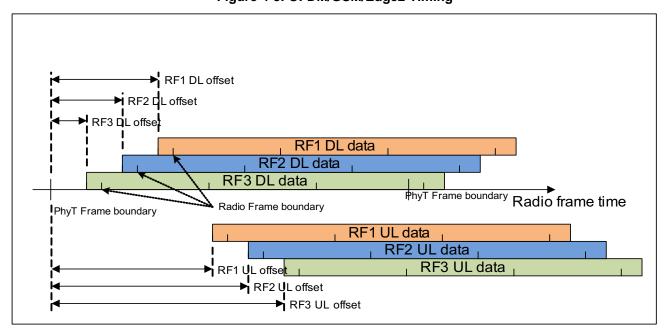

|       |       | 3.2.2.1 LTE Framing                                                | 44        |

|       |       | 3.2.2.2 CPRI LTE (FDD and TDD)                                     | 46        |

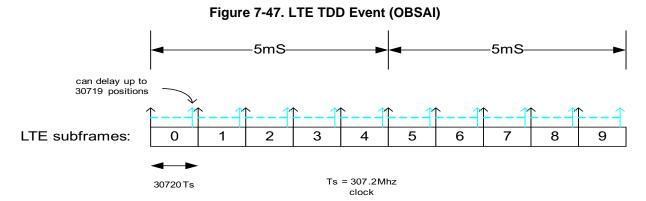

|       |       | 3.2.2.3 OBSAI LTE (FDD and TDD)                                    | 47        |

|       |       | 3.2.3 LTE 80 MHz and 100MHz Support                                | 48        |

|       |       | 3.2.3.1 80 MHz                                                     | 48        |

|       |       | 3.2.3.2 100 MHz                                                    | 48        |

|       |       | 3.2.4 TD-SCDMA.                                                    | 48        |

|       |       | 3.2.4.1 TD-SCDMA Framing.                                          | 48        |

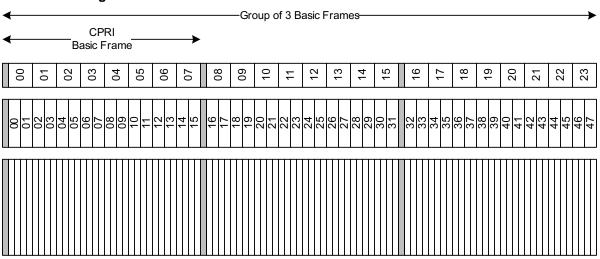

|       |       | 3.2.4.2 CPRI TD-SCDMA                                              | <b>50</b> |

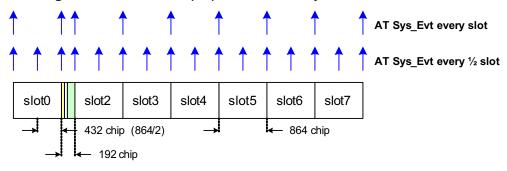

|       |       | 3.2.4.3 TD-SCDMA DMA                                               | 51        |

|       |       | 3.2.4.4 TD-SCMDA Timer (AT) Operation                              | 52        |

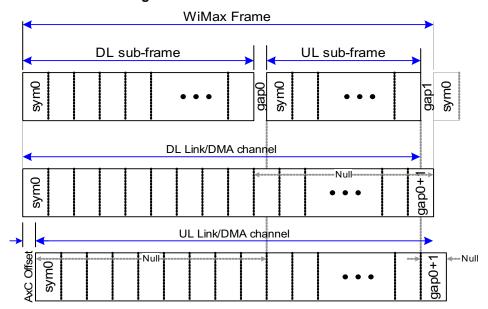

|       |       | 3.2.5 WiMax                                                        |           |

|       |       | 3.2.5.1 WiMax Framing                                              |           |

|       |       | 3.2.5.2 WiMax, AIF2 Implementation                                 |           |

|       |       | 3.2.5.3 OBSAI WiMax                                                |           |

|       |       | 3.2.5.4 CPRI WiMax                                                 |           |

|       |       | 3.2.6 GSM/Edge Requirement and Handling                            |           |

|       |       | 3.2.6.1 GSM Base Band Hopping                                      |           |

|       |       | 3.2.6.2 AxC Compression (Time Slot DTX)                            |           |

|       |       | 3.2.6.3 Dynamic Configuration                                      | 56        |

| 4     | AIF2  | Timing Information                                                 | <b>60</b> |

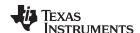

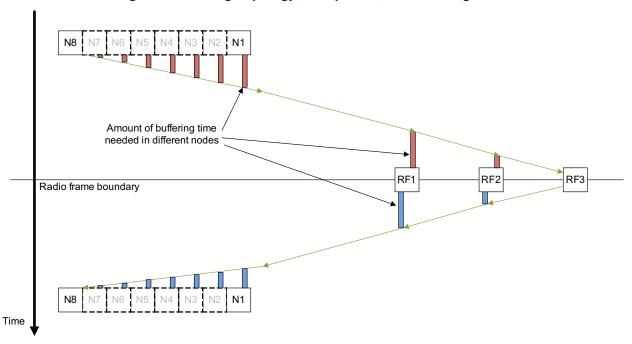

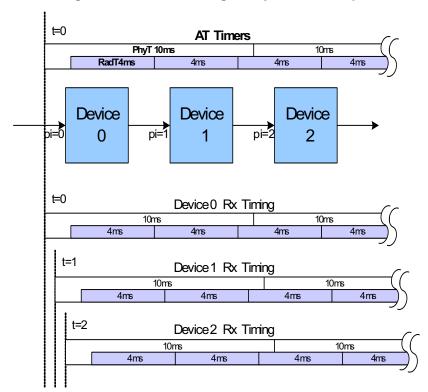

|       | 4.1   | Timing and Topology                                                | 61        |

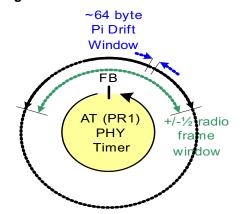

|       |       | 4.1.1 Synchronization and Resynchronization                        | 63        |

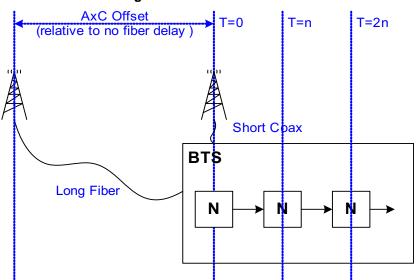

|       | 4.2   | AxC Offset                                                         |           |

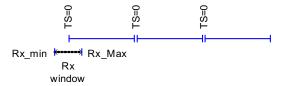

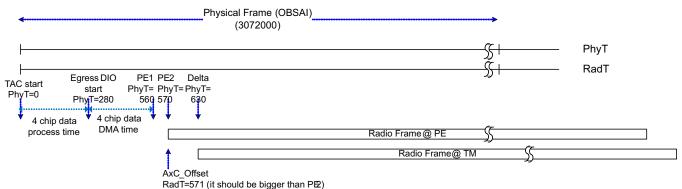

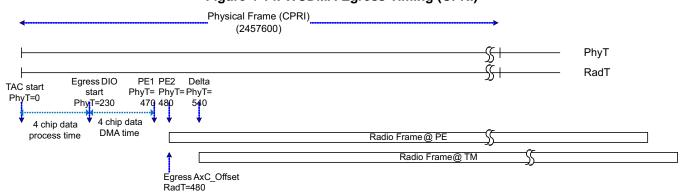

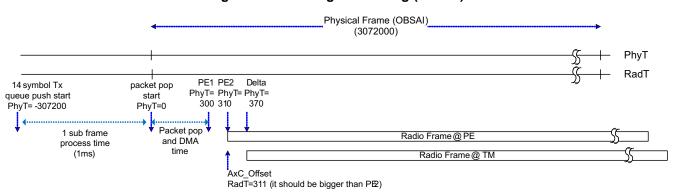

|       | 4.3   | OBSAI Reception Timing                                             |           |

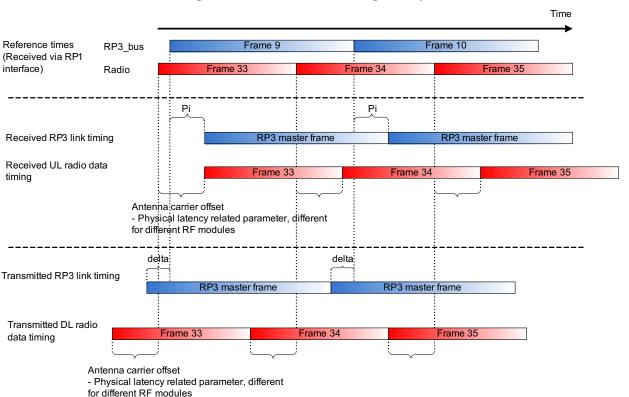

|       |       | 4.3.1 Pi and Delta Timing                                          |           |

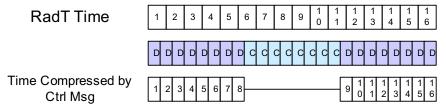

|       |       | 4.3.2 OBSAI Radio Timing                                           |           |

|       |       | 4.3.3 Tx Timing Message Construction: Radio Counter                |           |

|       |       | 4.3.4 AIF2 Implementation of OBSAI Radio Timing                    | 67        |

2

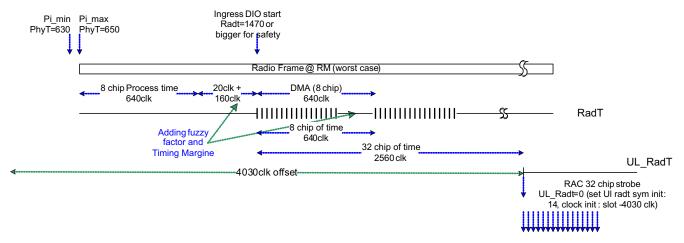

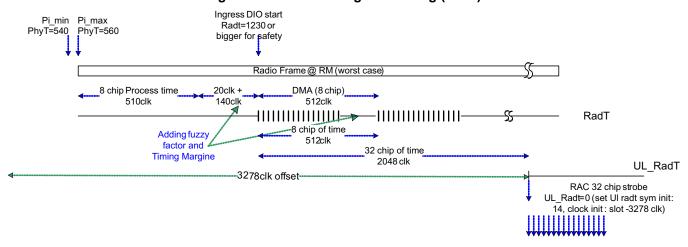

|   |            | 4.3.4.1   | AIF2 OBSAI Ingress Reception Timing Implementation   |              |

|---|------------|-----------|------------------------------------------------------|--------------|

|   |            | 4.3.4.2   | AIF2 OBSAI Egress Transmission Timing Implementation |              |

|   | 4.4        | -         | RadT Timers                                          |              |

|   | 4.5        |           | g Details                                            |              |

|   |            |           | IA Timing                                            |              |

|   |            | 4.5.1.1   | PKTDMA Timing                                        |              |

|   |            | 4.5.1.2   | AD DIO DMA Timing                                    |              |

|   |            |           | <sup>2</sup> Internal Delay                          |              |

|   |            | 4.5.2.1   | DB =>PE Timing                                       |              |

|   |            | 4.5.2.2   | PE=>TM Timing                                        |              |

|   |            | 4.5.2.3   | Delta and PE Event Offset Calculation                | . 74         |

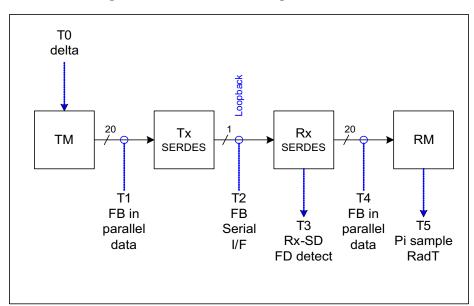

|   |            | 4.5.2.4   | TM =>RM SerDes Loopback Timing                       | . 74         |

|   |            | 4.5.2.5   | TM =>RM Timing                                       |              |

|   |            | 4.5.2.6   | RM => RT timing (Retransmission or Aggregation)      | . 75         |

|   |            | 4.5.2.7   | RM =>PD =>DB Timing (UL Case)                        | . 75         |

|   |            | 4.5.2.8   | MAC Timing (SerDes Timing)                           | . 76         |

|   |            | 4.5.3 WC  | CDMA Timing Example                                  | . 77         |

|   |            | 4.5.4 LTI | E Timing Example                                     | . <b>7</b> 8 |

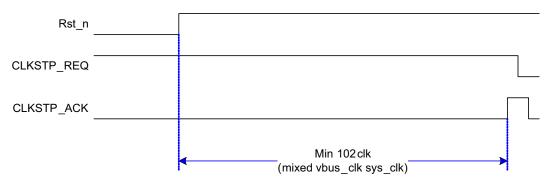

|   |            | 4.5.5 CL  | KSTP_REQ Min Timing                                  | <b>7</b> 9   |

| 5 | Interf     | ace Stand | ards CPRI, OBSAI Specifics                           | 81           |

|   | 5.1        |           | Al Overlay of Functionality                          |              |

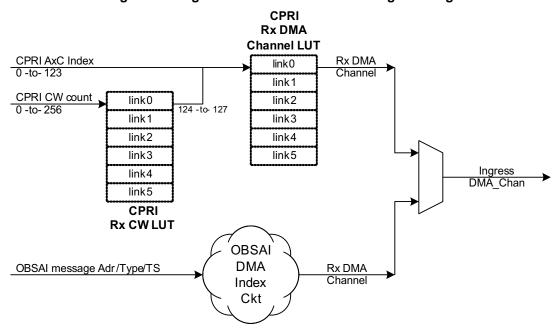

|   | 0          |           | RI/OBSAI Ingress DMA Channel Addressing/Indexing     |              |

|   |            | 5.1.1.1   | CPRI                                                 |              |

|   |            | 5.1.1.2   | OBSAI                                                |              |

|   |            |           | ception Timing                                       |              |

|   |            |           | Insmission Based Timing                              |              |

|   |            |           | ort Frame Mode                                       |              |

|   |            | 5.1.4.1   | OBSAI                                                |              |

|   |            | 5.1.4.2   | CPRI                                                 |              |

|   | 5.2        | _         | cifics                                               |              |

|   | 0.2        | •         | RI Control Data Flow                                 |              |

|   |            | 5.2.1.1   | Fast Ethernet                                        |              |

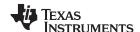

|   |            | 5.2.1.2   | 4B/5B Encoding                                       |              |

|   |            | 5.2.1.3   | Interleave/Deinterleave                              |              |

|   |            | 5.2.1.4   | Packet Parsing                                       |              |

|   |            | 5.2.1.4   | Control Packet DMA                                   |              |

|   |            |           |                                                      |              |

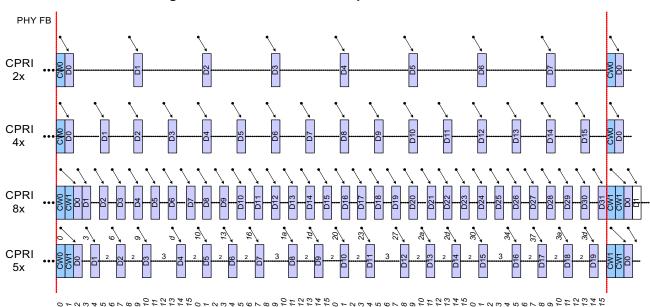

|   |            |           | RI Physical Interface (Phy) Timing                   |              |

|   |            |           | RI Link Maintenance {LOS, LOF, RAI, SDI}             |              |

|   | <i>-</i> 2 |           | RI AIF2 Timer Startup                                |              |

|   | 5.3        |           | ecifics                                              |              |

|   |            |           | SAI Standard Overview                                |              |

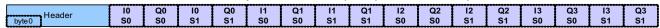

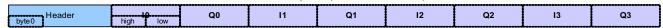

|   |            | 5.3.1.1   | OBSAI Overview: Frame/Message Structure              |              |

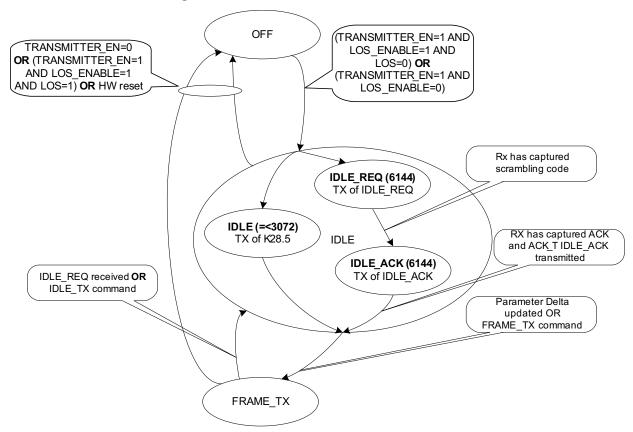

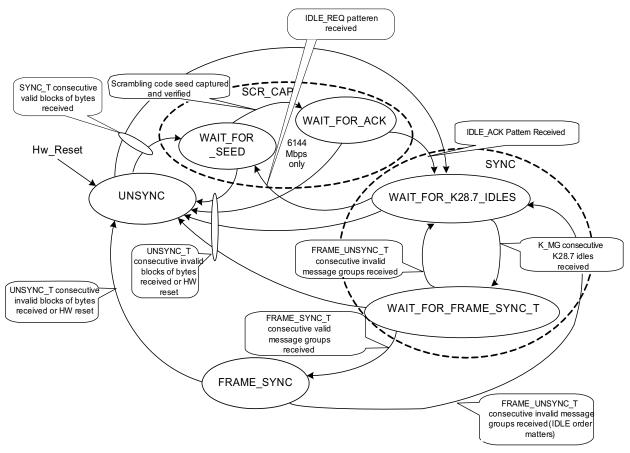

|   |            | 5.3.1.2   | OBSAI Overview: RP3 Tx and Rx FSMs                   |              |

|   |            | 5.3.1.3   | OBSAI Overview: Timestamp                            |              |

|   |            | 5.3.1.4   | OBSAI Overview: Message Payload Formats              |              |

|   |            |           | SAI: Header Based Processing                         |              |

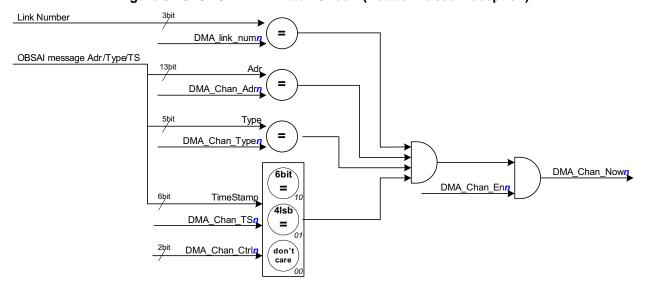

|   |            | 5.3.2.1   | DMA Channel Index                                    |              |

|   |            | 5.3.2.2   | 8B/10B Code Violation and Bad OBSAI Message Header   |              |

|   |            | 5.3.2.3   | OBSAI: Missing Timestamp                             |              |

|   |            |           | SAI: 6 GHz Scrambling                                |              |

|   |            |           | SAI: Generic Packet Mode                             | 101          |

|   |            |           | SAI: RP3 Transmission                                | 102          |

|   |            | 5.3.5.1   | OBSAI Tx: Modulo Rules                               | 102          |

|   |       | 5.3.5.           | 2 OBSAI Tx: Dual-Bit Map Rules                    | 02               |

|---|-------|------------------|---------------------------------------------------|------------------|

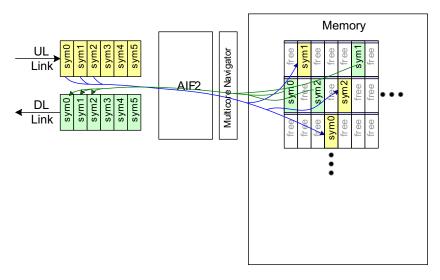

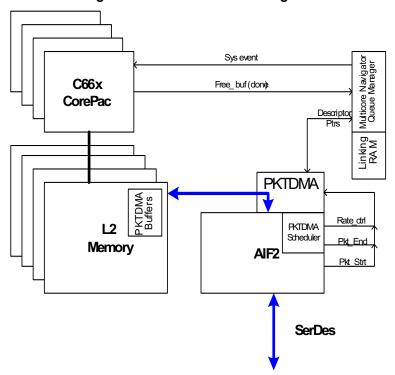

| 6 | AIF2  | DMA (M           | ulticore Navigator and DIO) Information10         | 04               |

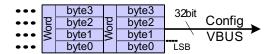

|   | 6.1   | •                | Pata Formats                                      |                  |

|   |       | 6.1.1            | AIF2 16-Bit Sample DMA (OFDM and WCDMA DL)        | 05               |

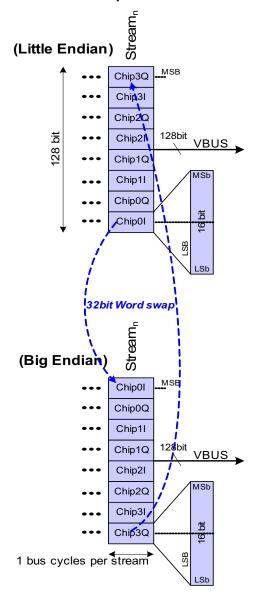

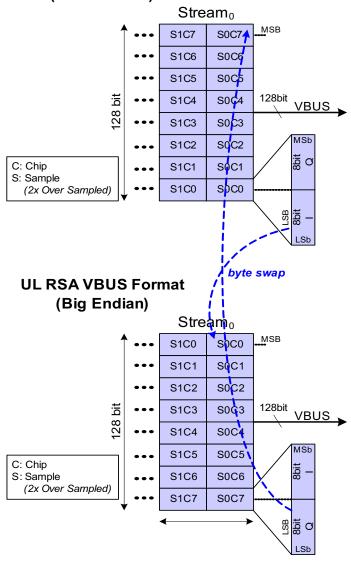

|   |       | 6.1.2            | NCDMA UL DMA                                      | 06               |

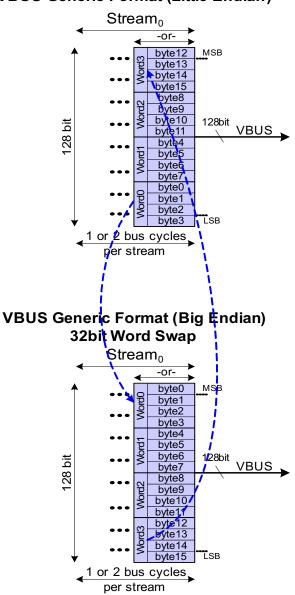

|   |       | 6.1.3            | Generic Format DMA10                              | 07               |

|   |       | 6.1.4            | VBUS Config Bus                                   | 80               |

|   | 6.2   | AIF2 Di          | rect IO                                           | 80               |

|   |       | 6.2.1            | AIF2 Direct IO                                    | 09               |

|   |       | 6.2.2            | AIF2 Direct IO Link Data Trace                    | 10               |

|   | 6.3   | PKTDM            | A 1 <sup>2</sup>                                  | 11               |

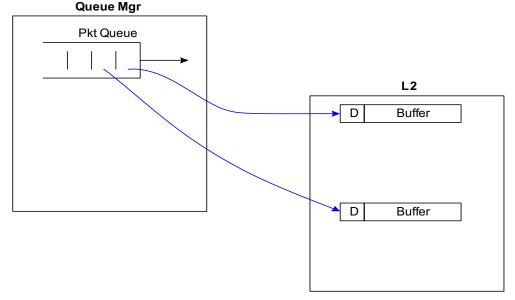

|   |       | 6.3.1            | Multicore Navigator Buffers and Descriptors1      | 12               |

|   |       | 6.3.2            | Multicore Navigator Queues1                       | 13               |

|   |       |                  | Multicore Navigator and DIO Scheduling            |                  |

|   |       |                  | Multicore Navigator Packet Types1                 |                  |

|   | 6.4   |                  | e Navigator Examples                              |                  |

|   |       | 6.4.1            | ngress (AIF2 Reception DMA-to-L2 RAM)             | 17               |

|   |       |                  | Egress (L2 RAM DMA-to-AIF2 Transmission)          |                  |

| 7 | Imple |                  | on Details and Application for Internal Modules12 |                  |

| • | 7.1   |                  | chitecture                                        |                  |

|   | 7.1   |                  | USP Configuration Bus Interface)                  |                  |

|   | 1.2   | ,                | Clock Stop and Emulation                          |                  |

|   |       |                  | Emulation Control                                 |                  |

|   |       |                  | AIF2 Reset.                                       |                  |

|   | 7.3   | -                | Des)                                              |                  |

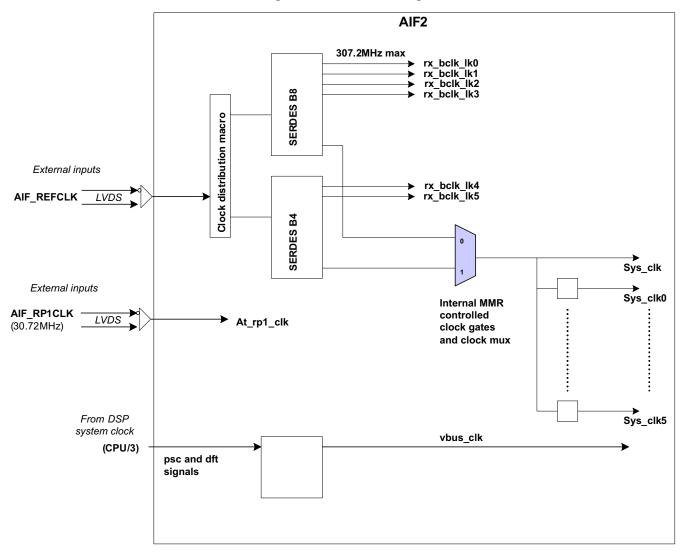

|   | 7.3   | •                | AIF2 Clock Strategy                               |                  |

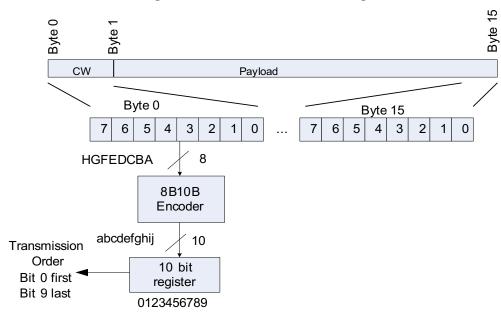

|   |       |                  | SerDes Serial Bit Ordering                        |                  |

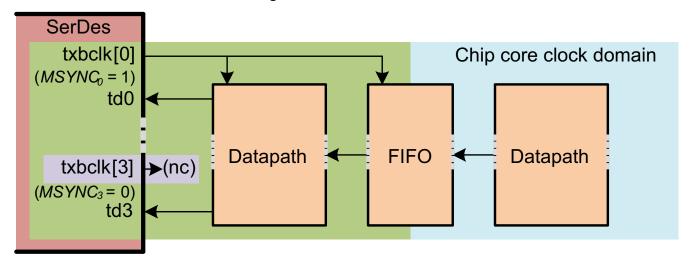

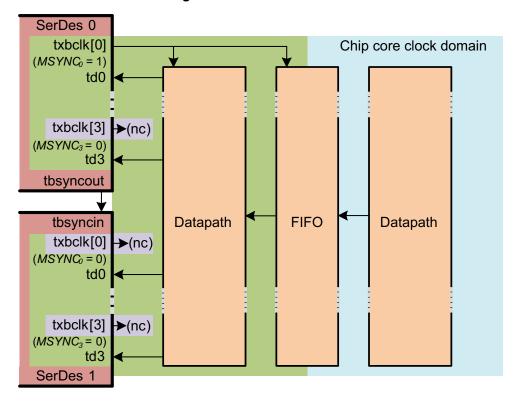

|   |       |                  | SerDes Common Configuration                       |                  |

|   |       | 7.3.3            |                                                   | 21<br>27         |

|   |       | 7.3.3.<br>7.3.3. | ·                                                 | 21<br>27         |

|   |       | 7.3.3.           |                                                   |                  |

|   |       | 7.3.3.<br>7.3.3. | ·                                                 | 2 <i>1</i><br>28 |

|   |       |                  | 4 Clock Bypass                                    |                  |

|   |       | 7.3.4            | 3                                                 |                  |

|   |       | 7.3.4.<br>7.3.4. |                                                   |                  |

|   |       | _                | , ,                                               | 20<br>28         |

|   |       | 7.3.4.           | o clock recovery / agont me                       |                  |

|   |       | 7.3.4.<br>7.3.4. |                                                   |                  |

|   |       | _                | 1,,                                               |                  |

|   |       | 7.3.4.           |                                                   |                  |

|   |       |                  | 3                                                 | 29               |

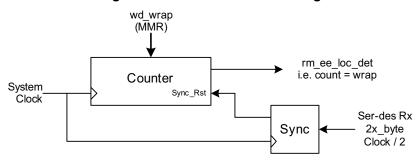

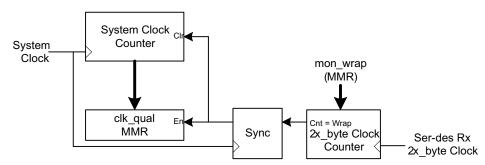

|   |       | 7.3.5.           |                                                   | 29               |

|   |       | 7.3.5.           |                                                   | 29               |

|   |       | 7.3.5.<br>7.3.5. |                                                   | 30               |

|   |       |                  |                                                   | 31               |

|   | 7.4   | 7.3.5.           |                                                   | 31               |

|   | 7.4   |                  | ,                                                 | 31               |

|   |       |                  |                                                   | 31               |

|   |       | 7.4.1.           |                                                   | 31               |

|   |       |                  | ,                                                 | 33               |

|   |       | 7.4.2.           | ,                                                 | 33               |

|   |       |                  | 3                                                 | 36               |

|   |       | 7.4.3.           | 3                                                 |                  |

|   |       | 7.4.3.           | 2 Received K character Handling 13                | 36               |

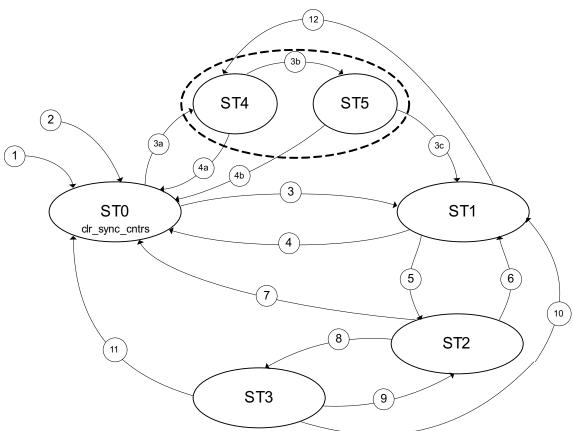

| 7.4.4 RM                         | Programming                                                                                                                                                                                                                                                                                                                                                                                            | 137                                                                                                                                                                        |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.4.4.1                          | RM Link Configuration                                                                                                                                                                                                                                                                                                                                                                                  | 137                                                                                                                                                                        |

| 7.4.4.2                          | RM FSM Sync Count Configuration                                                                                                                                                                                                                                                                                                                                                                        | 138                                                                                                                                                                        |

| 7.4.4.3                          | RM FSM Unsync Count Configuration                                                                                                                                                                                                                                                                                                                                                                      | 138                                                                                                                                                                        |

| 7.4.4.4                          | Clock Detection Configuration                                                                                                                                                                                                                                                                                                                                                                          | 138                                                                                                                                                                        |

| 7.4.4.5                          | RM Status                                                                                                                                                                                                                                                                                                                                                                                              | 138                                                                                                                                                                        |

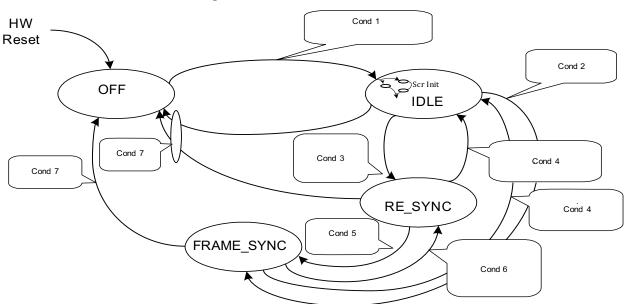

| TM (TX Ma                        | nc)                                                                                                                                                                                                                                                                                                                                                                                                    | 139                                                                                                                                                                        |

| 7.5.1 Trai                       | nsmit Frame Synchronization and Formatting                                                                                                                                                                                                                                                                                                                                                             | 139                                                                                                                                                                        |

| 7.5.1.1                          | Frame Construction                                                                                                                                                                                                                                                                                                                                                                                     | 140                                                                                                                                                                        |

| 7.5.1.2                          | Transmit Frame Control                                                                                                                                                                                                                                                                                                                                                                                 | 140                                                                                                                                                                        |

| 7.5.2 Trai                       | nsmit FIFO                                                                                                                                                                                                                                                                                                                                                                                             | 141                                                                                                                                                                        |

| 7.5.3 Tx N                       |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                            |

| 7.5.3.1                          | TM State Machine Control Register (AIF2_TM_CTRL[0-5])                                                                                                                                                                                                                                                                                                                                                  | 141                                                                                                                                                                        |

| 7.5.3.2                          | TM Scrambler Control Register (AIF2_TM_SCR_CTRL[0-5])                                                                                                                                                                                                                                                                                                                                                  | 142                                                                                                                                                                        |

| 7.5.3.3                          | TM CPRI L1 Inband Configuration Register (AIF2_TM_L1_CFG[0-5])                                                                                                                                                                                                                                                                                                                                         | 142                                                                                                                                                                        |

| 7.5.3.4                          | TM CPRI L1 Inband Enable Register (AIF2_TM_L1_EN[0-5])                                                                                                                                                                                                                                                                                                                                                 | 142                                                                                                                                                                        |

| 7.5.3.5                          | TM CPRI L1 Inband LOSERR Link Select Register (AIF2_TM_LOSERR[0-5])                                                                                                                                                                                                                                                                                                                                    | 143                                                                                                                                                                        |

| 7.5.3.6                          | TM CPRI L1 Inband LOFERR Link Select Register (AIF2_TM_LOFERR[0-5])                                                                                                                                                                                                                                                                                                                                    | 143                                                                                                                                                                        |

| 7.5.3.7                          | TM CPRI L1 Inband LOSRx Link Select Register (AIF2_TM_LOSRx[0-5])                                                                                                                                                                                                                                                                                                                                      | 143                                                                                                                                                                        |

| 7.5.3.8                          | TM CPRI L1 Inband LOFRx Link Select Register (AIF2_TM_LOFRx[0-5])                                                                                                                                                                                                                                                                                                                                      | 143                                                                                                                                                                        |

| 7.5.3.9                          | TM CPRI L1 Inband RAIRx Link Select Register (AIF2_TM_RAIRx[0-5])                                                                                                                                                                                                                                                                                                                                      | 144                                                                                                                                                                        |

| 7.5.3.10                         | TM CPRI Pointer P Configuration Register (AIF2_TM_PTRP[0-5])                                                                                                                                                                                                                                                                                                                                           | 144                                                                                                                                                                        |

| 7.5.3.11                         |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                            |

| 7.5.3.12                         |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                            |

| CI and CO                        |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                            |

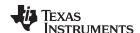

| 7.6.1 CPF                        | RI Data Formats                                                                                                                                                                                                                                                                                                                                                                                        | 144                                                                                                                                                                        |

| RT (Retran                       | smitter)                                                                                                                                                                                                                                                                                                                                                                                               | 150                                                                                                                                                                        |

| 7.7.1 15-k                       | bit Saturation Operation for CPRI (7-bit follows the same rule)                                                                                                                                                                                                                                                                                                                                        | 151                                                                                                                                                                        |

| 7.7.2 16-b                       | bit Saturation Operation (8-bit follows the same rule)                                                                                                                                                                                                                                                                                                                                                 | 151                                                                                                                                                                        |

| PD (Protoc                       | ol Decoder)                                                                                                                                                                                                                                                                                                                                                                                            | 151                                                                                                                                                                        |

| 7.8.1 PD                         | Route Module                                                                                                                                                                                                                                                                                                                                                                                           | 151                                                                                                                                                                        |

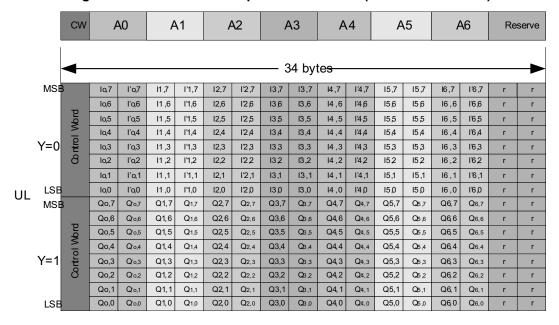

| 7.8.1.1                          | OBSAI Route and DB buffer Channel Number                                                                                                                                                                                                                                                                                                                                                               | 151                                                                                                                                                                        |

| 7.8.1.2                          | CPRI Route (DBM) and DB Buffer Channel Number                                                                                                                                                                                                                                                                                                                                                          | 152                                                                                                                                                                        |

| 7.8.2 PD                         | Pack Module                                                                                                                                                                                                                                                                                                                                                                                            | 153                                                                                                                                                                        |

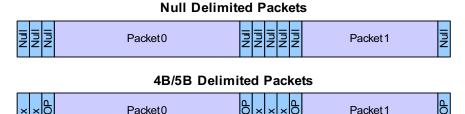

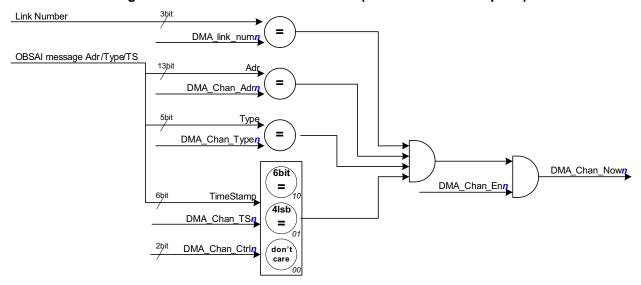

| 7.8.2.1                          | PD Pack CPRI Packet Delimitation                                                                                                                                                                                                                                                                                                                                                                       | 153                                                                                                                                                                        |

| 7.8.2.2                          | PD Pack CPRI Null Delimitation                                                                                                                                                                                                                                                                                                                                                                         | 154                                                                                                                                                                        |

| 7.8.2.3                          | PD Pack OBSAI Packet Delimitation                                                                                                                                                                                                                                                                                                                                                                      | 155                                                                                                                                                                        |

| 7.8.2.4                          | PD Pack 4 Channel Map                                                                                                                                                                                                                                                                                                                                                                                  | 156                                                                                                                                                                        |

| 7.8.2.5                          | PD Pack Ethernet Header Strip                                                                                                                                                                                                                                                                                                                                                                          | 156                                                                                                                                                                        |

| 7.8.2.6                          | PD CRC                                                                                                                                                                                                                                                                                                                                                                                                 | 157                                                                                                                                                                        |

| 7.8.3 PD                         | Stage Module                                                                                                                                                                                                                                                                                                                                                                                           | 158                                                                                                                                                                        |

| 7.8.3.1                          | PD Stage                                                                                                                                                                                                                                                                                                                                                                                               | 158                                                                                                                                                                        |

| 7.8.3.2                          | PD FRAME                                                                                                                                                                                                                                                                                                                                                                                               | 158                                                                                                                                                                        |

| 7.8.3.3                          | PD DMA_IF                                                                                                                                                                                                                                                                                                                                                                                              | 162                                                                                                                                                                        |

| PE (Protoco                      | ol Encoder)                                                                                                                                                                                                                                                                                                                                                                                            | 162                                                                                                                                                                        |

| 7.9.1 OBS                        | SAI Transmission Rules                                                                                                                                                                                                                                                                                                                                                                                 | 162                                                                                                                                                                        |

| 7.9.1.1                          | PE OBSAI Modulo Transmission Rules                                                                                                                                                                                                                                                                                                                                                                     | 163                                                                                                                                                                        |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                            |

| 7.9.1.2                          | PE OBSAI Dual Bit Map Tx Rules                                                                                                                                                                                                                                                                                                                                                                         | 164                                                                                                                                                                        |

| 7.9.1.2<br>7.9.1.3               | PE OBSAI Dual Bit Map Tx Rules PE Transmission Rules Channel LUT                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                            |

| 7.9.1.3                          | ·                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                            |

| 7.9.1.3<br>7.9.2 CPF             | PE Transmission Rules Channel LUT                                                                                                                                                                                                                                                                                                                                                                      | 165                                                                                                                                                                        |

| 7.9.1.3<br>7.9.2 CPF<br>7.9.3 PE | PE Transmission Rules Channel LUT                                                                                                                                                                                                                                                                                                                                                                      | 165<br>166                                                                                                                                                                 |

|                                  | 7.4.4.1 7.4.4.2 7.4.4.3 7.4.4.4 7.4.4.5 TM (TX Marth 1988) 7.5.1 Tra 7.5.1.1 7.5.1.2 7.5.2 Tra 7.5.3.1 7.5.3.2 7.5.3.3 7.5.3.4 7.5.3.5 7.5.3.6 7.5.3.7 7.5.3.8 7.5.3.9 7.5.3.10 7.5.3.11 7.5.3.12 Cl and CO 7.6.1 CPI RT (Retran 7.7.1 15- 7.7.2 16- PD (Protoc 7.8.1 PD 7.8.1.1 7.8.1.2 7.8.2 PD 7.8.1.1 7.8.2.2 7.8.2.3 7.8.2.4 7.8.2.5 7.8.2.6 7.8.3 PD 7.8.3.1 7.8.3.2 7.8.3.3 PE (Protoc 7.9.1 OB | 7.4.4.2         RM FSM Unsync Count Configuration.           7.4.4.3         RM FSM Unsync Count Configuration.           7.4.4.5         RM Status.           TM (TX Mac) |

|      | 7.9.5.1    | AxC Frame Counter                          | 168 |

|------|------------|--------------------------------------------|-----|

|      | 7.9.5.2    | Channel and Packet State                   | 169 |

|      | 7.9.6 PE I | DB Interface                               | 169 |

|      | 7.9.6.1    | CPRI Data Request I/F                      | 169 |

|      | 7.9.6.2    | OBSAI Data Request I/F                     | 170 |

|      | 7.9.6.3    | DIO Data Request I/F                       | 170 |

|      | 7.9.6.4    | PE DB Token Request I/F                    |     |

|      | 7.9.7 PE I | Message Construction                       |     |

|      | 7.9.7.1    | PE_MC_ENET                                 |     |

|      | 7.9.7.2    | PE_MC_CRC                                  |     |

|      | 7.9.7.3    | PE_MC_OBSAI_HEADER                         |     |

|      |            | RT Interface                               |     |

|      | 7.9.8.1    | PE_RT_SYNC                                 |     |

| 7.10 |            |                                            |     |

| 7.10 | · ·        | uffer)                                     |     |

|      |            | dressing                                   |     |

|      | -          | gnment Logic                               |     |

|      |            | ffer Channel Enables                       |     |

|      |            | ner Functionality                          |     |

|      | 7.10.4.1   | Protocol-Specific Data                     |     |

|      | 7.10.4.2   | Packet Type                                |     |

|      | 7.10.4.3   | Egress DIO offset                          | 175 |

|      | 7.10.4.4   | EDB Packet Mode Control                    |     |

|      | 7.10.4.5   | Consumption-Based Scheduling               | 176 |

|      | 7.10.5 DB  | Debug                                      | 176 |

|      | 7.10.5.1   | Overview                                   | 176 |

|      | 7.10.5.2   | Ingress DB Debug                           | 176 |

|      | 7.10.5.3   | Ingress DB Activity Monitoring             | 178 |

|      | 7.10.5.4   | Egress DB Debug                            | 178 |

|      | 7.10.5.5   | Egress DB Activity Monitoring              | 179 |

|      | 7.10.6 DB  | Data Trace Feature                         | 180 |

| 7.11 |            | MA)                                        |     |

|      |            | ress Scheduler (ISCH)                      |     |

|      |            | ress Scheduler (ESCH)                      |     |

|      | _          | ect IO                                     |     |

|      | 7.11.3.1   |                                            |     |

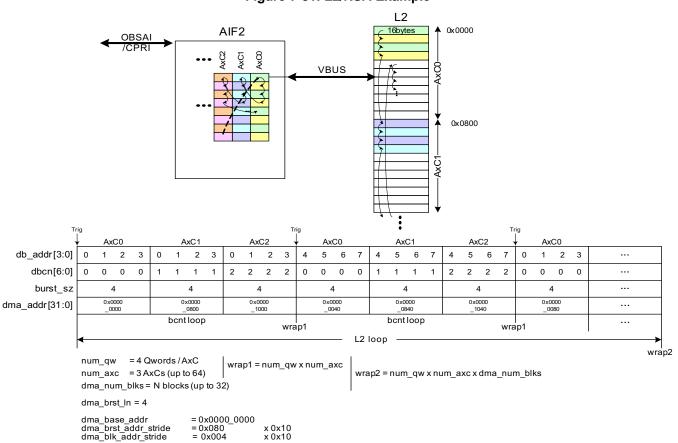

|      | _          | L2 Example                                 |     |

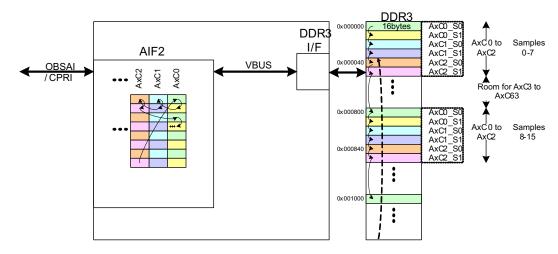

|      | 7.11.3.2   | DDR3 Example                               | 186 |

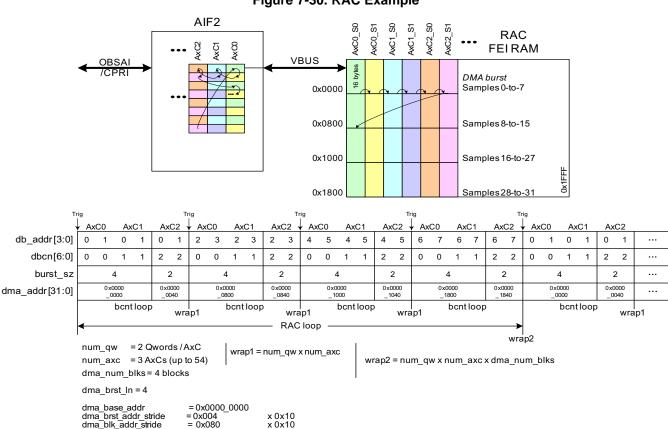

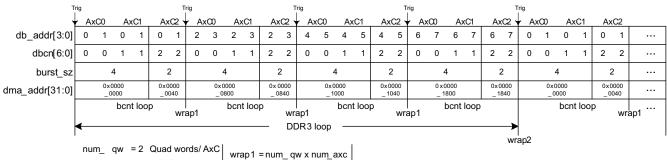

|      | 7.11.3.4   | TAC Example                                | 188 |

|      | 7.11.3.4   | Configuration Registers                    | 188 |

|      |            |                                            |     |

| 7.40 | 7.11.3.6   | Data Trace DIO                             | 189 |

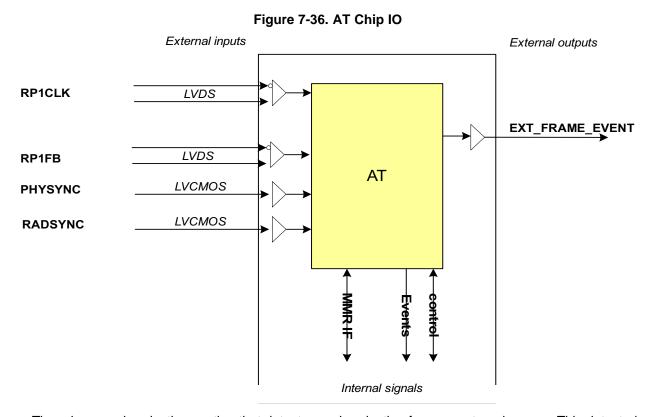

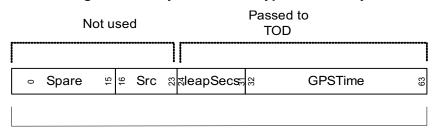

| 7.12 | •          | imer)                                      | 190 |

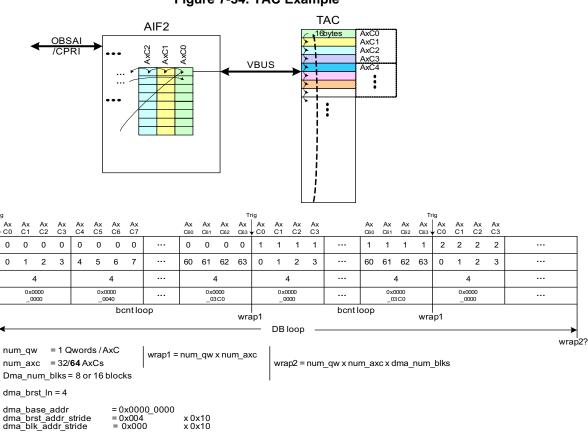

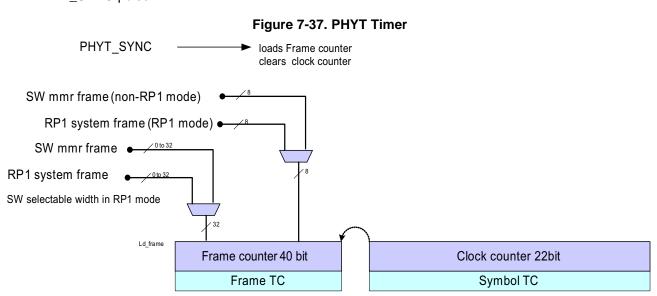

|      |            | Phy Timer (PHYT RP3 Timer)                 | 192 |

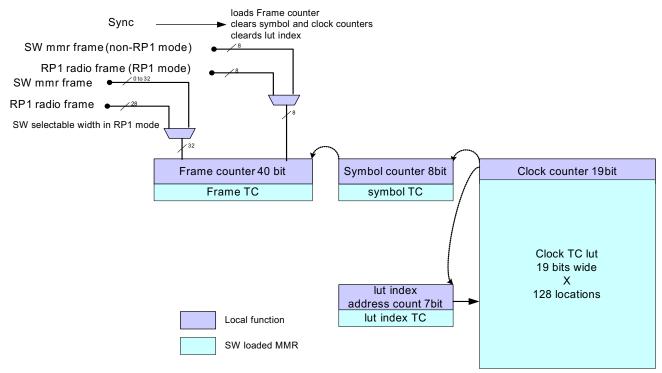

|      |            | Radio Timer (RADT RP1 Timer)               |     |

|      |            | OBSAI RP1 Synchronization                  | 196 |

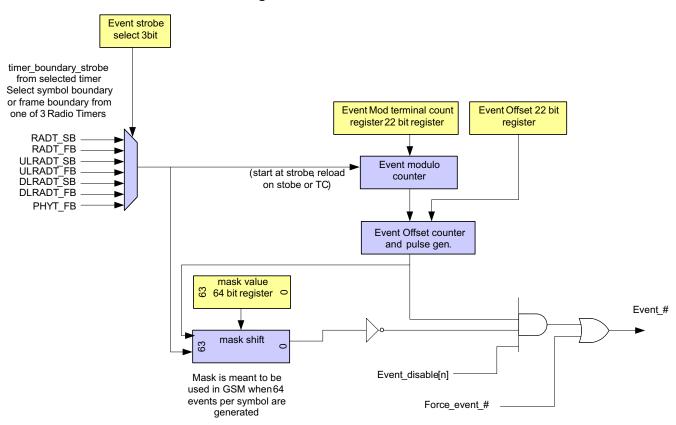

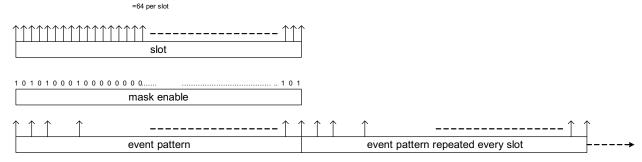

|      |            | Event Generation                           | 199 |

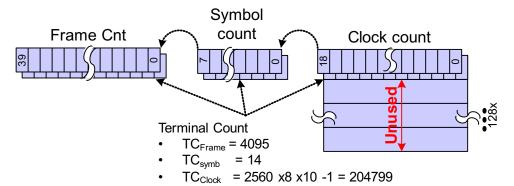

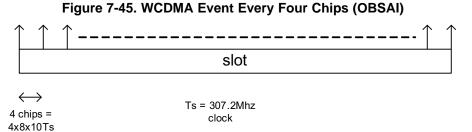

|      |            | WCDMA Counter                              | 201 |

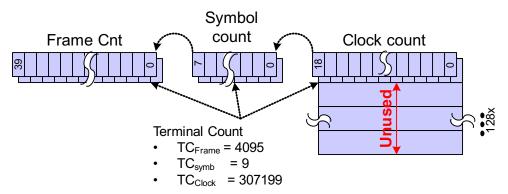

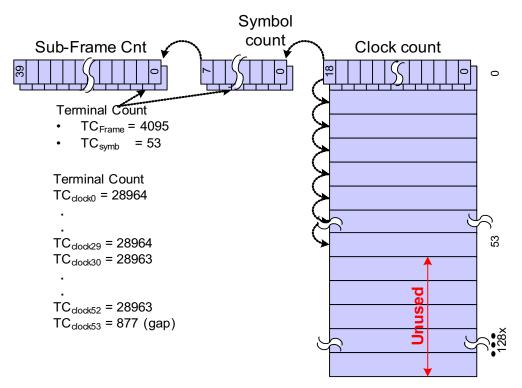

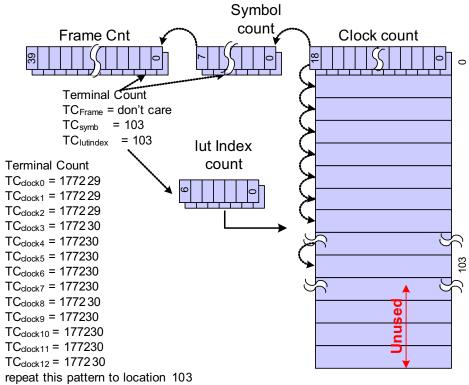

|      |            | LTE Counter                                | 202 |

|      |            | WiMAX Counter                              | 203 |

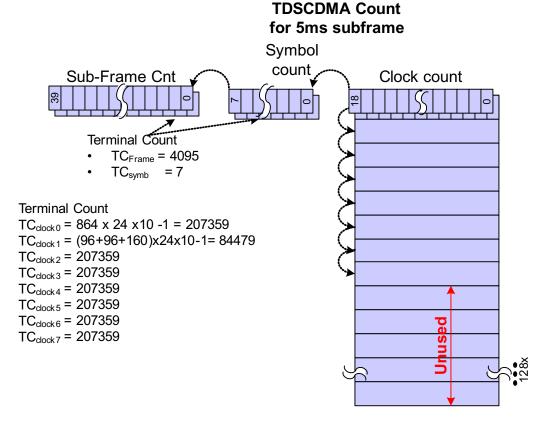

|      | 7.12.8 AT  | TD-SCDMA                                   | 204 |

|      |            | GSM Counter                                | 205 |

| 7.13 | •          | nd Exception Handler)                      | 208 |

|      | 7.13.1 EE  | Interrupt Support                          | 209 |

|      | 7.13.2 Ma  | pping Error/Alarm Conditions to Interrupts | 211 |

|      |            |                                            |     |

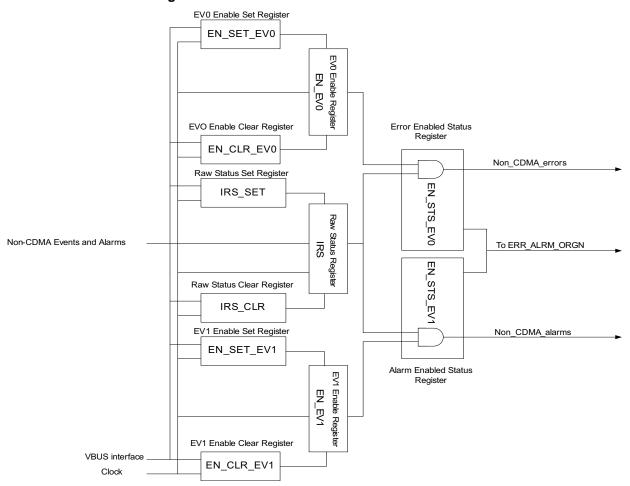

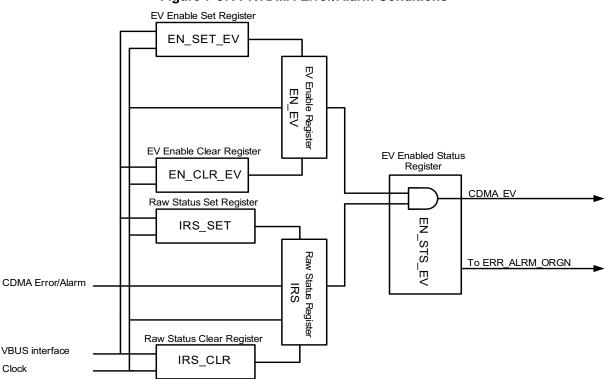

|   |      | 7.13.2.1   | Non-PKTDMA Error/Alarm Condition Mapping      | 211 |

|---|------|------------|-----------------------------------------------|-----|

|   |      | 7.13.2.2   | PKTDMA Error/Alarm Condition Mapping          | 212 |

|   |      | 7.13.3 En  | d-of-Interrupt Support (EOI)                  | 212 |

|   |      | 7.13.4 EE  | Run (EE_AIF2_RUN)                             | 213 |

|   |      | 7.13.5 Err | or/Alarm Condition Force Support              | 213 |

|   |      | 7.13.6 Err | or/Alarm Condition Origination Support        | 213 |

| 8 | Reai | ster Map   |                                               | 216 |

|   | 8.1  | •          | rs                                            |     |

|   |      |            | uped Common Registers Details                 |     |

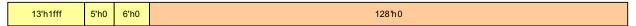

|   |      | 8.1.1.1    | aif2_pid Register (Address = 0x0000)          |     |

|   |      | 8.1.1.2    | aif2_scratch Register (Address = 0x0004)      |     |

|   |      | 8.1.1.3    | aif2_reset Register (Address = 0x0008)        |     |

|   |      | 8.1.1.4    | aif2_emu Register (Address = 0x000C)          |     |

|   |      | 8.1.1.5    | vc_stat Register (Address = 0x0010)           |     |

|   | 8.2  | SD Registe | ers                                           |     |

|   |      | -          | uped Common Registers Details                 |     |

|   |      | 8.2.1.1    | SD_RX_EN_CFG[0] Register (offset = 0x8000)    |     |

|   |      | 8.2.1.2    | SD_RX_R1_CFG[0] Register (offset = 0x8004)    |     |

|   |      | 8.2.1.3    | SD_RX_R2_CFG[0] Register (offset = 0x8008)    |     |

|   |      | 8.2.1.4    | SD_RX_STS[0] Register (offset = 0x800C)       | 227 |

|   |      | 8.2.1.5    | SD_TX_EN_CFG[0] Register (offset = 0x8010)    | 228 |

|   |      | 8.2.1.6    | SD_TX_R1_CFG[0] Register (offset = 0x8014)    | 229 |

|   |      | 8.2.1.7    | SD_TX_R2_CFG[0] Register (offset = 0x8018)    | 230 |

|   |      | 8.2.1.8    | SD_TX_STS[0] Register (offset = 0x801C)       | 232 |

|   |      | 8.2.1.9    | SD_PLL_B8_EN_CFG Register (offset = 0xB000)   | 233 |

|   |      | 8.2.1.10   | SD_PLL_B4_EN_CFG Register (offset = 0xB004)   | 234 |

|   |      | 8.2.1.11   | SD_PLL_B8_CFG Register (offset = 0xB008)      | 235 |

|   |      | 8.2.1.12   | SD_PLL_B4_CFG Register (offset = 0xB00C)      | 236 |

|   |      | 8.2.1.13   | SD_PLL_B8_STS Register (offset = 0xB010)      | 237 |

|   |      | 8.2.1.14   | SD_PLL_B4_STS Register (offset = 0xB014)      | 238 |

|   |      | 8.2.1.15   | SD_CLK_SEL_CFG Register (offset = 0xB018)     |     |

|   |      | 8.2.1.16   | SD_LK_CLK_DIS_CFG Register (offset = 0xB01C)  | 240 |

|   | 8.3  | RM Registe | ers                                           | 241 |

|   |      | 8.3.1 Link | Registers Details                             |     |

|   |      | 8.3.1.1    | RM_LK_CFG0[0] Register (offset = 0x50000)     |     |

|   |      | 8.3.1.2    | RM_LK_CFG1[0] Register (offset = 0x50004)     |     |

|   |      | 8.3.1.3    | RM_LK_CFG2[0] Register (offset = 0x50008)     |     |

|   |      | 8.3.1.4    | RM_LK_CFG3[0] Register (offset = 0x5000C)     |     |

|   |      | 8.3.1.5    | RM_LK_CFG4[0] Register (offset = 0x50010)     |     |

|   |      | 8.3.1.6    | RM_LK_STS0[0] Register (offset = 0x50014)     |     |

|   |      | 8.3.1.7    | RM_LK_STS1[0] Register (offset = 0x50018)     |     |

|   |      | 8.3.1.8    | RM_LK_STS2[0] Register (offset = 0x5001C)     |     |

|   |      | 8.3.1.9    | RM_LK_STS3[0] Register (offset = 0x50020)     |     |

|   |      | 8.3.1.10   | RM_LK_STS4[0] Register (offset = 0x50024)     |     |

|   |      | 8.3.1.11   | RM_CFG Register (offset = 0x53000)            |     |

|   | 8.4  |            | ers                                           |     |

|   |      |            | Registers Details                             |     |

|   |      | 8.4.1.1    | TM_LK_CFG[0] Register (offset = 0x4C000)      |     |

|   |      | 8.4.1.2    | TM_LK_CTRL[0] Register (offset = 0x4C004)     |     |

|   |      | 8.4.1.3    | TM_LK_SCR_CTRL[0] Register (offset = 0x4C008) |     |

|   |      | 8.4.1.4    | TM_LK_L1_CFG[0] Register (offset = 0x4C00C)   |     |

|   |      | 8.4.1.5    | TM_LK_L1_EN[0] Register (offset = 0x4C010)    |     |

|   |      | 8.4.1.6    | TM_LK_LOSERR[0] Register (offset = 0x4C014)   | 263 |

|     | 8.4.1.7  | IM_LK_LOFERR[0] Register (offset = 0x4C018)          | 264 |

|-----|----------|------------------------------------------------------|-----|

|     | 8.4.1.8  | TM_LK_LOSRx[0] Register (offset = 0x4C01C)           | 265 |

|     | 8.4.1.9  | TM_LK_LOFRx[0] Register (offset = 0x4C020)           | 266 |

|     | 8.4.1.10 | TM_LK_RAIRx[0] Register (offset = 0x4C024)           | 267 |

|     | 8.4.1.11 | TM_LK_HFN[0] Register (offset = 0x4C028)             | 268 |

|     | 8.4.1.12 | TM_LK_PTRP[0] Register (offset = 0x4C02C)            | 269 |

|     | 8.4.1.13 | TM_LK_STRT[0] Register (offset = 0x4C030)            | 270 |

|     | 8.4.1.14 | TM_LK_PROT[0] Register (offset = 0x4C034)            |     |

|     | 8.4.1.15 | TM_LK_STAT[0] Register (offset = 0x4C038)            |     |

|     | 8.4.1.16 | TM_FRM_MODE[0] Register (offset = 0x4C03C)           |     |

| 8.5 |          | S                                                    |     |

|     |          | Registers Details                                    |     |

|     | 8.5.1.1  | CI_LK_CFG[0] Register (offset = 0x58000)             |     |

| 8.6 |          | ors                                                  |     |

| 0.0 | -        | Registers Details                                    |     |

|     | 8.6.1.1  | CO_LK_CFG[0] Register (offset = 0x5C000)             |     |

| 8.7 |          | rs                                                   |     |

| 0.7 | •        | Registers Details                                    |     |

|     | 8.7.1.1  | RT_LK_CFG[0] Register (offset = 0x54000)             |     |

|     | 8.7.1.2  | RT_LK_DPTH[0] Register (offset = 0x54000)            |     |

|     |          | · · · · · · · · · · · · · · · · · · ·                |     |

|     | 8.7.1.3  | RT_HDR_ERR[0] Register (offset = 0x54008)            |     |

| 0.0 | 8.7.1.4  | RT_LK_STAT[0] Register (offset = 0x5400C)            |     |

| 8.8 | •        | rs                                                   |     |

|     |          | Registers Details                                    |     |

|     | 8.8.1.1  | pd_link_a[0] Register (offset = 0x60000)             |     |

|     | 8.8.1.2  | pd_link_b[0] Register (offset = 0x60004)             |     |

|     | 8.8.1.3  | pd_lk_pack_cpri[0] Register (offset = 0x60008)       |     |

|     | 8.8.1.4  | pd_cpri_crc[0] Register (offset = 0x60014)           |     |

|     | 8.8.1.5  | pd_pack_map[0] Register (offset = 0x60018)           |     |

|     | 8.8.1.6  | pd_dbm[0] Register (offset = 0x6001C)                |     |

|     | 8.8.1.7  | pd_dbm_1map[0][0-3] Register (offset = 0x60020)      |     |

|     | 8.8.1.8  | pd_dbm_2map[0][0-2] Register (offset = 0x60030)      |     |

|     | 8.8.1.9  | pd_type_lut[0][0-31] Register (offset = 0x60080)     |     |

|     | 8.8.1.10 | pd_cpri_id_lut[0][0-127] Register (offset = 0x60200) | 294 |

|     | 8.8.1.11 | pd_cw_lut[0][0-255] Register (offset = 0x60400)      | 295 |

|     | 8.8.1.12 | pd_global Register (offset = 063000)                 | 296 |

|     | 8.8.1.13 | pd_global_en_set Register (0x63004)                  | 297 |

|     | 8.8.1.14 | pd_global_en_clr Register (offset = 0x63008)         | 298 |

|     | 8.8.1.15 | pd_global_en_sts Register (offset = 0x6300C)         | 299 |

|     | 8.8.1.16 | pd_dma Register (offset = 0x63010)                   | 300 |

|     | 8.8.1.17 | pd_radt_tc Register (offset = 0x63014)               | 301 |

|     | 8.8.1.18 | pd_chan_sts[4] Register (offset = 0x63020)           |     |

|     | 8.8.1.19 | pd_pkt_sts[4] Register (offset = 0x63030)            |     |

|     | 8.8.1.20 | pd_frm_tc[6] Register (offset = 0x63040)             |     |

|     | 8.8.1.21 | pd_route[128] Register (offset = 0x63400)            |     |

|     | 8.8.1.22 | pd_dmachan[128] Register (offset = 0x63600)          |     |

|     | 8.8.1.23 | pd_dmachan_a[128] Register (offset = 0x64000)        |     |

|     | 8.8.1.24 | pd_dmachan_b[128] Register (offset = 0x64200)        |     |

|     | 8.8.1.25 | pd_dmachan_c[128] Register (offset = 0x64400)        |     |

|     | 8.8.1.26 | pd_dmachan_d[128] Register (offset = 0x64600)        |     |

|     | 8.8.1.27 | pd_dmachan_e[128] Register (offset = 0x64800)        |     |

|     | 8.8.1.28 | pd_dmachan_f[128] Register (offset = 0x64A00)        |     |

|     | 8.8.1.29 | pd_trm_msg_tc[128] Register (offset = 0x04A00)       |     |

|     | 0.0.1.29 | pa_iiii_iiisg_tc[120]                                | 313 |

| 8.9  | PE Register | 'S                                                  | 314 |

|------|-------------|-----------------------------------------------------|-----|

|      | 8.9.1 Link  | Registers Details                                   | 317 |

|      | 8.9.1.1     | pe_link[0] Register (offset = 0x68000)              | 317 |

|      | 8.9.1.2     | pe_crc[0] Register (offset = 0x68004)               | 318 |

|      | 8.9.1.3     | pe_cpri_dbm[0] Register (offset = 0x68008)          | 319 |

|      | 8.9.1.4     | pe_cpri_bitswap[0] Register (offset = 0x6800C)      | 320 |

|      | 8.9.1.5     | pe_cpridbm_1map[0][0-3] Register (offset = 0x68010) | 321 |

|      | 8.9.1.6     | pe_cpridbm_2map[0][0-2] Register (offset = 0x68020) | 322 |

|      | 8.9.1.7     | pe_cpri0[0] Register (offset = 0x6802C)             | 323 |

|      | 8.9.1.8     | pe_cpri1[0] Register (offset = 0x68030)             | 324 |

|      | 8.9.1.9     | pe_cw_lut[0][0-255] Register (offset = 0x68400)     | 325 |

|      | 8.9.1.10    | pe_global Register (offset = 0x6C000)               | 326 |

|      | 8.9.1.11    | pe_global_en_set Register (offset = 0x6C004)        | 327 |

|      | 8.9.1.12    | pe_global_en_clr (offset = 0x6C008)                 | 327 |

|      | 8.9.1.13    | pe_global_en_sts Register (offset = 0x6C00C)        | 328 |

|      | 8.9.1.14    | pe_chan_sts[4] Register (offset = 0x6C010)          | 329 |

|      | 8.9.1.15    | pe_pkt_sts[4] Register (offset = 0x6C020)           |     |

|      | 8.9.1.16    | pe_frm_tc[6] Register (offset = 0x6C080)            |     |

|      | 8.9.1.17    | pe_dmachan_en[128] Register (offset = 0x6C200)      |     |

|      | 8.9.1.18    | pe_dma0chan[128] Register (offset = 0x6C400)        | 333 |

|      | 8.9.1.19    | pe_in_fifo[128] Register (offset = 0x6C600)         |     |

|      | 8.9.1.20    | pe_axc_offset[128] Register (offset = 0x6C800)      |     |

|      | 8.9.1.21    | pe_frm_msg_tc[128] Register (offset = 0x6CA00)      | 336 |

|      | 8.9.1.22    | pe_modtxrule[64] Register (offset = 0x6CC00)        |     |

|      | 8.9.1.23    | pe_obsai_hdr[0-127] Register (offset = 0x6CE00)     |     |

|      | 8.9.1.24    | pe_obsai_dbm[64] Register (offset = 0x70000)        |     |

|      | 8.9.1.25    | pe_dbm_map[512] Register (offset = 0x70800)         |     |

|      | 8.9.1.26    | pe_rule_chanlut0[512] Register (offset = 0x74000)   |     |

|      | 8.9.1.27    | pe_rule_chanlut1[512] Register (offset = 0x74800)   |     |

|      | 8.9.1.28    | pe_rule_chanlut2[512] Register (offset = 0x75000)   |     |

|      | 8.9.1.29    | pe_rule_chanlut3[512] Register (offset = 0x75800)   |     |

|      | 8.9.1.30    | pe_rule_chanlut4[512] Register (offset = 0x76000)   |     |

|      | 8.9.1.31    | pe_rule_chanlut5[512] Register (offset = 0x76800)   |     |

|      | 8.9.1.32    | pe_rule_chanlut6[512] Register (offset = 0x77000)   |     |

|      |             | pe_rule_chanlut7[512] Register (offset = 0x77800)   |     |

| 8.10 | -           | 'S                                                  |     |

|      |             | uped Common Registers Details                       |     |

|      | 8.10.1.1    | DB_IDB_CFG Register (offset = 0x10000)              |     |

|      | 8.10.1.2    | DB_IDB_GLOBAL_EN_SET Register (offset = 0x10004)    |     |

|      | 8.10.1.3    | DB_IDB_GLOBAL_EN_CLR Register (offset = 0x10008)    |     |

|      | 8.10.1.4    | DB_IDB_GLOBAL_EN_STS Register (offset = 0x1000C)    |     |

|      | 8.10.1.5    | DB_IDB_CH_EN[4] Register (offset = 0x10010)         |     |

|      | 8.10.1.6    | DB_IDB_DEBUG_D0 Register (offset = 0x10100)         |     |

|      | 8.10.1.7    | DB_IDB_DEBUG_D1 Register (offset = 0x10104)         |     |

|      | 8.10.1.8    | DB_IDB_DEBUG_D2 Register (offset = 0x10108)         |     |

|      | 8.10.1.9    | DB_IDB_DEBUG_D3 Register (offset = 0x1010C)         |     |

|      |             | DB_IDB_DEBUG_SBND Register (offset = 0x10110)       |     |

|      |             | ,                                                   |     |

|      |             | DB_IDB_DEBUG_OFS Register (offset = 0x10118)        |     |

|      |             | DB_IDB_DEBUG_OFS_DAT Register (offset = 0x1011C)    |     |

|      |             | DB_IDB_PTR_CH[128] Register (offset = 0x10200)      |     |

|      |             | DB_IDB_CFG_CH[128] Register (offset = 0x10400)      |     |

|      | ö.1U.1.16   | DB_IDB_CH_EMPTY[4] Register (offset = 0x10600)      | 300 |

|      | 0.40.4.47                           | DD 5DD 050 D 11 / 11 0 11000)                                                                                                                        |                   |

|------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|      |                                     | DB_EDB_CFG Register (offset = 0x11000)                                                                                                               |                   |

|      | 8.10.1.18                           | = = = 5 ( )                                                                                                                                          |                   |

|      | 8.10.1.19                           | /                                                                                                                                                    |                   |

|      | 8.10.1.20                           | ,                                                                                                                                                    |                   |

|      | 8.10.1.21                           | DB_EDB_CH_EN[4] Register (offset = 0x11010)                                                                                                          |                   |

|      | 8.10.1.22                           | ,                                                                                                                                                    |                   |

|      | 8.10.1.23                           | · · · · · · · · · · · · · · · · · · ·                                                                                                                |                   |

|      | 8.10.1.24                           | DB_EDB_DEBUG_D2 Register (offset = 0x11108)                                                                                                          | 374               |

|      | 8.10.1.25                           | = ==9 ( /                                                                                                                                            |                   |

|      | 8.10.1.26                           | ,                                                                                                                                                    |                   |

|      | 8.10.1.27                           | DB_EDB_DEBUG_RD_CNTL Register (offset = 0x11114)                                                                                                     | 377               |

|      | 8.10.1.28                           | DB_EDB_DEBUG_DB_RD Register (offset = 0x1111C)                                                                                                       | 378               |

|      | 8.10.1.29                           | DB_EDB_DEBUG_OFS Register (offset = 0x11120)                                                                                                         | 379               |

|      | 8.10.1.30                           | DB_EDB_DEBUG_OFS_DAT Register (offset = 0x11124)                                                                                                     | 380               |

|      | 8.10.1.31                           | DB_EDB_DEBUG_WR_TOK Register (offset = 0x11128)                                                                                                      | 381               |

|      | 8.10.1.32                           | DB_EDB_EOP_CNT Register (offset = 0x1112C)                                                                                                           | 382               |

|      | 8.10.1.33                           | DB_EDB_PTR_CH[128] Register (offset = 0x11200)                                                                                                       | 383               |

|      | 8.10.1.34                           | DB_EDB_CFG_CH[128] Register (offset = 0x11400)                                                                                                       | 384               |

| 8.11 | AD Register                         | 'S                                                                                                                                                   | 385               |

|      |                                     | uped Common Registers Details                                                                                                                        |                   |

|      | 8.11.1.1                            | AD_DIO_I_TABLE_SEL[0] Register (offset = 0xC000)                                                                                                     | 388               |

|      |                                     | AD_DIO_I_TABLE_LOOP_CFG[0] Register (offset = 0xC004)                                                                                                |                   |

|      |                                     | AD_DIO_I_DMA_CFG0[0] Register (offset = 0xC008)                                                                                                      |                   |

|      |                                     | AD_DIO_I_DMA_CFG1[0] Register (offset = 0xC00C)                                                                                                      |                   |

|      |                                     | AD_DIO_I_DMA_CFG2[0] Register (offset = 0xC010)                                                                                                      |                   |

|      |                                     | AD_DIO_I_BCN_TABLE0_ROW0[0] to AD_DIO_I_BCN_TABLE0_ROW15[0] Register (offset                                                                         |                   |

|      |                                     | 0xC014 to 0xC050)                                                                                                                                    | 393               |

|      |                                     | AD_DIO_I_BCN_TABLE1_ROW0[0] to AD_DIO_I_BCN_TABLE1_ROW15[0] Register (offset 0xC054 to 0xC090)                                                       | 394               |

|      |                                     | AD_DIO_E_TABLE_SEL[0] Register (offset = 0xC300)                                                                                                     |                   |

|      |                                     | AD_DIO_E_TABLE_LOOP_CFG[0] Register (offset = 0xC304)                                                                                                |                   |

|      |                                     | AD_DIO_E_DMA_CFG0[0] Register (offset = 0xC308)                                                                                                      |                   |

|      |                                     | AD_DIO_E_DMA_CFG1[0] Register (offset = 0xC30C)                                                                                                      |                   |

|      | 8.11.1.12                           | AD_DIO_E_DMA_CFG2[0] Register (offset = 0xC310)                                                                                                      | 399               |

|      | 8.11.1.13                           | AD_DIO_E_BCN_TABLE0_ROW0[0] to AD_DIO_E_BCN_TABLE0_ROW15[0] Register (offs 0xC314 to 0xC350)                                                         | set =<br>400      |

|      | 8.11.1.14                           | AD_DIO_E_BCN_TABLE1_ROW0[0] to AD_DIO_E_BCN_TABLE1_ROW15[0] Register (offs                                                                           | set =             |

|      |                                     | 0xC354 to 0xC390)                                                                                                                                    |                   |

|      | 8.11.1.15                           | = = = = • • • • • • • • • • • • • • • •                                                                                                              |                   |

|      | 8.11.1.16                           | ,                                                                                                                                                    |                   |

|      | 8.11.1.17                           | = = = = • • • • • • • • • • • • • • • •                                                                                                              |                   |

|      | 8.11.1.18                           | ,                                                                                                                                                    |                   |

|      | 8.11.1.19                           |                                                                                                                                                      |                   |

|      | 8.11.1.20                           | ,                                                                                                                                                    |                   |

|      | 8.11.1.21                           | AD_ DIO_I _GLOBAL_EN_STS Register (offset = 0xC618)                                                                                                  |                   |

|      | 8.11.1.22                           | /                                                                                                                                                    |                   |

|      |                                     | AD_ DIO_E _GLOBAL_EN_CLR Register (offset = 0xC620)                                                                                                  |                   |

|      | 8.11.1.24                           | AD_ DIO_E_GLOBAL_EN_STS Register (offset = 0xC624)                                                                                                   | 411               |

|      |                                     |                                                                                                                                                      |                   |