TI Designs: TIDA-01567

# Voltage-Margining Power Supply for USB Type-C<sup>™</sup> Ports in Docking Stations Reference Design

## Description

This reference design allows easy system integration of a USB Type-C™ power supply that supports voltage margining. Efficiently converting power from a common 9-, 12- or 15-V adaptor to the USB Type-C port, the TPS62136 step-down converter directly accepts the digital signal of a microcontroller (MCU) to change its output voltage from the USB standard 5 V to a higher, programmable voltage. This output-voltage slew rate meets USB Type-C specifications. Especially useful for smartphone battery fast-charging applications in docking stations, this higher voltage allows more power at up to 4 A of current to be delivered across the USB Type-C cable.

#### Resources

TIDA-01567 Design Folder

TPS62136 Product Folder

ASK Our E2E Experts

#### **Features**

- Easily Adjustable V<sub>OUT</sub> With Slew Rate Control

- V<sub>OUT</sub> Margining With Single Digital Input Pin

- 4-A Output Current

- More than 90% Efficiency (99% Peak)

- 9- to 17-V Input Voltage Range

# **Applications**

- Docking Stations

- Smartphone Fast-Charging

- USB Type-C Ports

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

System Description www.ti.com

# 1 System Description

The USB Type-C™ specification allows the USB host to adjust the voltage on the USB cable to meet the instantaneous application demands. A common application for USB Type-C ports, especially in docking stations, is fast-charging batteries in smartphones and other portable devices. In fast-charging, the USB voltage is increased to deliver more power to the battery while maintaining the same current in the USB cable. This design uses the TPS62136 step-down converter, which operates from common 9-, 12-, and 15-V adaptors and outputs up to 4 A of current.

This reference design switches between the common 5- and 9-V output voltages with a single digital input pin of the TPS62136 step-down converter. This voltage is fully adjustable from 0.8 V to 12 V to meet specific application requirements, which result from voltage drops across cables, USB protection switches, connectors, PCB traces, and so on. The system MCU drives the VSEL (voltage select) pin of the TPS62136 device to change the output voltage between the two levels.

This design uses simple circuitry to intentionally slow down the output voltage slew rate to meet the USB Type-C specification of slower than 30 mV/µsec. This output voltage margining is smooth and controlled.

# 1.1 Key System Specifications

**Table 1. Key System Specifications**

| PARAMETER                                                 | SPECIFICATIONS |

|-----------------------------------------------------------|----------------|

| Input voltage range (V <sub>IN</sub> )                    | 9 V to 17 V    |

| Output voltage (VSEL = Low)                               | 5 V            |

| Output voltage (VSEL = High)                              | 9 V            |

| Output voltage range (adjustable by R1, R2, R3, and Radd) | 0.8 V to 12 V  |

| Output current                                            | 4 A            |

| Output voltage slew rate                                  | < 30 mV/µsec   |

www.ti.com System Overview

# 2 System Overview

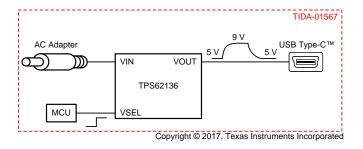

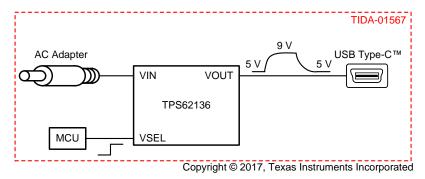

# 2.1 Block Diagram

Figure 1. TIDA-01567 Block Diagram

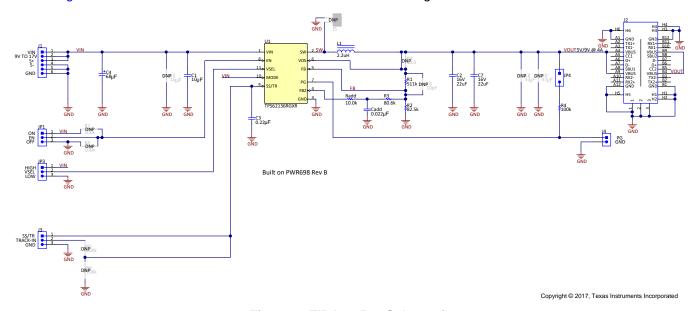

# 2.2 Schematic Reference

Figure 2 shows a schematic of the TIDA-01567 reference design.

Figure 2. TIDA-01567 Schematic

System Overview www.ti.com

# 2.3 Design Considerations

### 2.3.1 Output Voltage Slew Rate Control

The TPS62136 regulates the voltage at its feedback (FB) pin to 0.7 V. Typically, two resistors (R1 and R2) set the output voltage based on their gain from the FB pin to the output voltage. For a voltage-margining power supply, a third resistor (R3) connects the FB pin to GND through the FB2 pin of the integrated circuit (IC). FB2 is an output pin and is either floating or connected to GND based on the state of the VSEL input pin.

Changing VSEL immediately changes the state of FB2, which immediately changes the operating point of the TPS62136 device. Due to the very-fast transient response of the TPS62136, the output voltage quickly moves to the new operating point. This output voltage slew rate is way faster than what the USB Type-C specification allows; therefore, implement an RC filter, Radd and Cadd, to slow down this output voltage transition.

Choose empirical values for Radd and Cadd to sufficiently slow down the output voltage slew rate. As a starting point, choose Radd and Cadd values whose product (time constant) is in the range of the desired slew time. After choosing values and verifying that the slew rate is slow enough, be sure to measure the final circuit for sufficient control-loop stability and transient response. Set the lower output voltage level as described in the device data sheet and as calculated in Equation 1, by the choice of R1 and R2. Also set the higher output voltage level as described in the device data sheet and as calculated in Equation 2, by the choice of R1, R2, and R3. The same equations can be used, if the sum of R3 and Radd in the design is used in place of R3 in the data sheet equation.

$$R1 = R2 \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

(1)

$$R3 = \frac{V_{O1} \times R1 \times R2^{2}}{(V_{O2} - V_{O1}) \times (R1 \times R2 + R2^{2})}$$

for  $V_{O2} > V_{O1}$  (2)

Operate the TPS62136 device in forced pulse-width modulation (PWM) mode to control the output voltage slew rate from the higher voltage back down to the lower voltage. In forced PWM mode, the TPS62136 actively sinks the output voltage by moving energy from the output to the input to bring the output voltage back down. Alternatively, if using power save mode, the TPS62136 device does not sink the output voltage. Instead, the output voltage remains at the higher voltage, even after being configured to return to the lower voltage, and only decreases due to outside effects such as the external load and leakage currents.

#### 2.3.2 Soft-Start Time

The selection of capacitor C3 controls the soft-start time. Choosing a larger C3 value increases the soft-start time to be much longer than the time constant formed by R3 and Cadd. Because Cadd must be charged to the 0.7-V FB pin voltage during start-up, the output voltage may overshoot its 5-V target if the soft-start time is not sufficiently long.

# 2.4 Highlighted Products

#### 2.4.1 TPS62136

The TPS62136 is an efficient, small, and easy-to-use synchronous step-down converter that converts input voltages up to 17 V down to output voltages from 0.8 to 12 V at up to 4 A of current. Its VSEL pin allows easy adjustment of the output voltage by a single digital input, which typically comes from the system MCU. Hiccup overcurrent protection and output discharge enable safe system integration.

### 3 Hardware and Test Results

#### 3.1 Hardware

The TIDA-01567 design is built on the TPS62136EVM-698 with the minimal changes as indicated in the TIDA-01567 *Schematics* and *Bill of Materials*. On the TPS62136EVM-698 device, change the inductor, output capacitors, FB resistors, soft-start capacitor, and add Radd and Cadd. Then, set the shunt on JP1 to enable the device, the shunt on JP2 to operate in PWM mode, and remove the shunt on JP3. Drive JP3 with a function generator to achieve voltage margining.

#### 3.2 Test Results

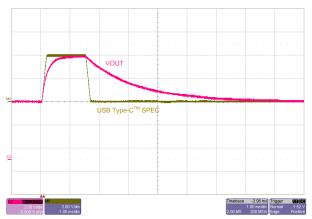

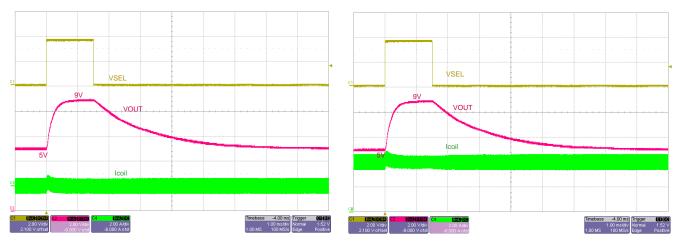

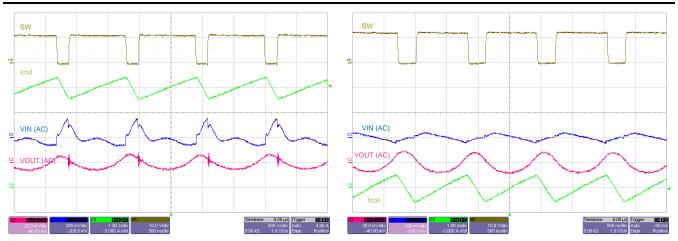

## 3.2.1 Voltage Margining Slew Rate

Figure 3 and Figure 4 show the voltage margining slew rate at both no load and full load, respectively. Each meets the USB Type-C specification.

Figure 3. Voltage Margining Slew Rate (Load = 0 A)

Figure 4. Voltage Margining Slew Rate (Load = 4 A)

Hardware and Test Results www.ti.com

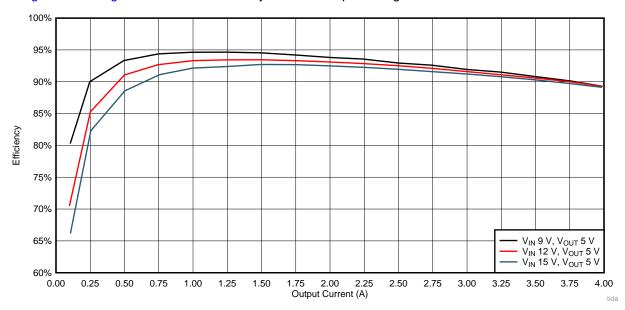

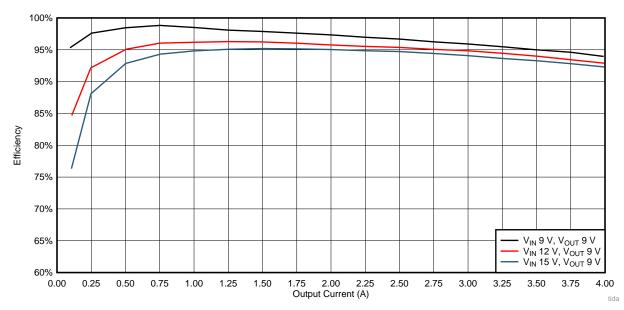

# 3.2.2 Efficiency

Figure 5 and Figure 6 show the efficiency at various input voltages.

Figure 5. Efficiency  $(V_{OUT} = 5 V)$

Figure 6. Efficiency  $(V_{OUT} = 9 V)$

www.ti.com Hardware and Test Results

## 3.2.3 Load Transient Response

Figure 7 and Figure 8 show the load transient response. The lack of ringing in the output voltage indicates sufficient stability.

Figure 7. Load Transient Response (V<sub>OUT</sub> = 5 V, 1-A to 3-A Load Step)

Figure 8. Load Transient Response (V<sub>OUT</sub> = 9 V, 1-A to 3-A Load Step)

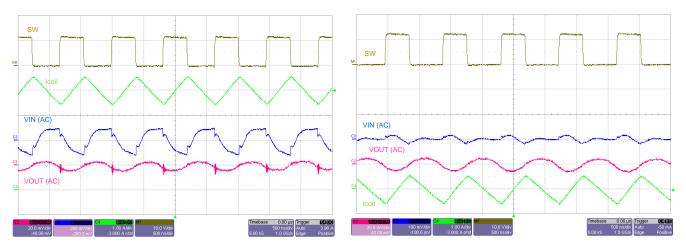

# 3.2.4 Output and Input Voltage Ripple

Figure 9 through Figure 12 show the output and input voltage ripple.

Figure 9. Output and Input Voltage Ripple (V<sub>out</sub> = 5 V, Load = 4 A)

Figure 10. Output and Input Voltage Ripple  $(V_{OUT} = 5 \text{ V}, \text{Load} = 0 \text{ A})$

Hardware and Test Results www.ti.com

Figure 11. Output and Input Voltage Ripple  $(V_{OUT} = 9 \text{ V}, \text{Load} = 4 \text{ A})$

Figure 12. Output and Input Voltage Ripple (V<sub>OUT</sub> = 9 V, Load = 0 A)

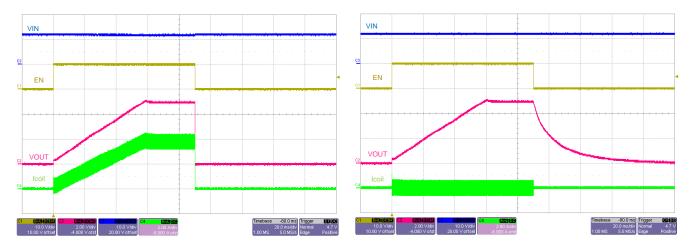

# 3.2.5 Start-Up and Shutdown

Figure 13 and Figure 14 show the start-up and shutdown behavior.

Figure 13. Start-Up and Shutdown  $(V_{OUT} = 5 \text{ V}, \text{Load} = 4 \text{ A})$

Figure 14. Start-Up and Shutdown  $(V_{OUT} = 5 \text{ V, Load} = 0 \text{ A})$

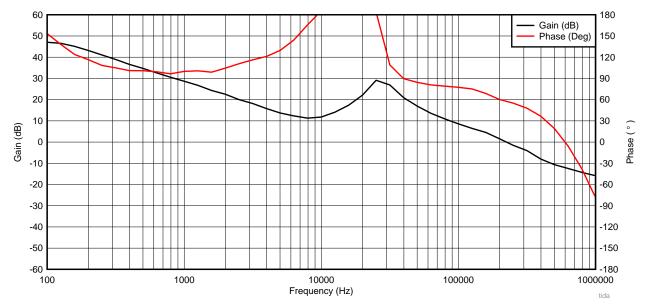

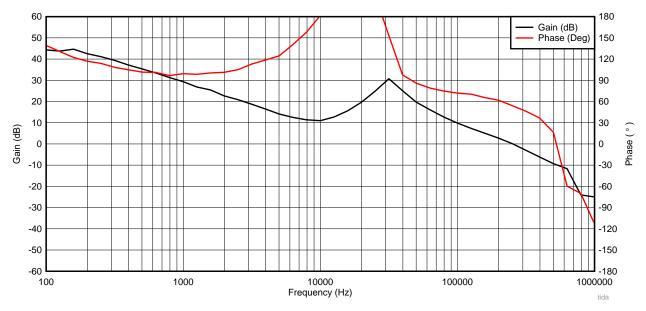

#### 3.2.6 Bode Plots

Figure 15 and Figure 16 show the bode plot (loop response) of both output voltages. The phase margin is well above 30°, which indicates stability.

Figure 15. Bode Plot (V<sub>OUT</sub> = 5 V, Load = 4 A), Bandwidth = 224 kHz, Phase Margin = 58°

Figure 16. Bode Plot (V<sub>OUT</sub> = 9 V, Load = 4 A), Bandwidth = 254 kHz, Phase Margin = 54°

Hardware and Test Results www.ti.com

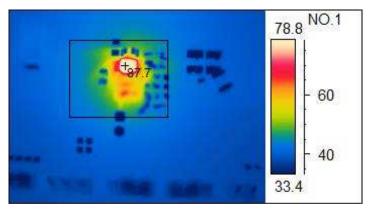

# 3.2.7 Thermal Performance

Figure 17 shows the thermal performance at full load.

Figure 17. Thermal Performance ( $V_{OUT} = 5 \text{ V}$ , Load = 4 A)

www.ti.com Design Files

# 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01567.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01567.

# 4.3 PCB Layout Recommendations

# 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01567.

## 4.4 Gerber Files

To download the Gerber files, see the design files at TIDA-01567.

# 4.5 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01567.

## 5 Related Documentation

Texas Instruments, TPS62136, TPS621361 1-MHz High Accuracy 3-V to 17-V 4-A Step-Down Converters with DCS-Control™

## 5.1 Trademarks

USB Type-C is a trademark of USB Implementers Forum, Inc. All other trademarks are the property of their respective owners.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated