TI Designs: TIDA-01056

# 20-Bit, 1-MSPS DAQ Reference Design for Optimizing Power Supply Efficiency While Minimizing EMI

# Description

This high-performance data acquisition (DAQ) system reference design optimizes the power stage to reduce power consumption and minimize the effect of electromagnetic interference (EMI). By using the LMS3635-Q1 buck converter, this design achieves high efficiency (even at light loads) and very-low EMI due to the HotRod™ package utilizing a symmetrical or butterfly layout. Also, due to the lower switching frequency of the LMS3635-Q1, the designer can more effectively filter the output voltage ripple with the use of low-dropout linear regulators (LDOs). This reference design yields a 7.2% efficiency improvement at light load current as compared to the LM53635 buck converter, which achieves 125.25-dB spurious-free dynamic range (SFDR), 99-dB signal-to-noise ratio (SNR), and 16.1 effective number of bits (ENOB).

#### Resources

TIDA-01056 Design Folder

LMS3635-Q1 Product Folder

TPS7A47 Product Folders

ASK Our E2E Experts

#### **Features**

- Power Design Minimizes DC-to-DC EMI Impact on System Performance

- Two 20-Bit SAR Analog-to-Digital Converter (ADC) Channels

- Modular Front-End Reference Design for High-Channel-Count Systems (Repeatable)

- Up to ±4-V Input Signal (8-V<sub>PP</sub> Differential)

# **Applications**

- Data Acquisition (DAQ)

- Semiconductor Test Equipment

- LCD Test Equipment

- Lab Instrumentation

- Battery Test

Copyright © 2017, Texas Instruments Incorporate

System Description www.ti.com

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

Multi-input systems requiring the simultaneous or parallel sampling of many data channels present design challenges to engineers developing data acquisition (DAQ) modules and automatic testers for applications such as semiconductor tests, memory tests, liquid-crystal display (LCD) tests, and battery tests. In these systems, often hundreds or thousands of data channels are required; thus, maximizing SNR performance while minimizing power, component count, and cost are all key design criteria. These systems have some type of power generator that typically includes DC-to-DC converters to provide the voltage levels required to power each device in the analog front end (AFE). These converters have switching components that cause EMI emission and harm the system performance.

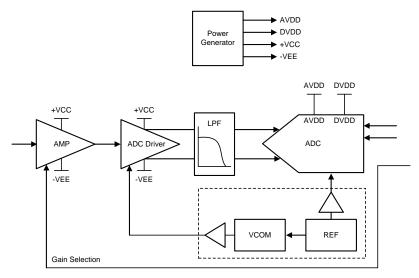

Figure 1 shows a block diagram of a generic AFE circuit.

Figure 1. Generic AFE

# 1.1 Key System Specifications

**Table 1. Key System Specifications**

| PARAMETER           | SPECIFICATIONS                       | MEASUREMENT                          |  |

|---------------------|--------------------------------------|--------------------------------------|--|

| Number of channels  | Dual                                 | Dual                                 |  |

| Input type          | Differential                         | Differential                         |  |

| Input range         | 8-V <sub>PP</sub> fully differential | 8-V <sub>PP</sub> fully differential |  |

| Resolution          | 20 bits                              | 20 bits                              |  |

| SNR                 | > 96 dB                              | 99 dB                                |  |

| THD                 | < -120 dB                            | -126.7 dB                            |  |

| ENOB                | > 16 bit                             | 16.16 bits                           |  |

| System power        | < 2.5 W                              | 1.92 W                               |  |

| Form factor (L × W) | 120 mm × 100 mm                      | 112.98 × 99.82 mm                    |  |

www.ti.com System Overview

# 2 System Overview

## 2.1 Block Diagram

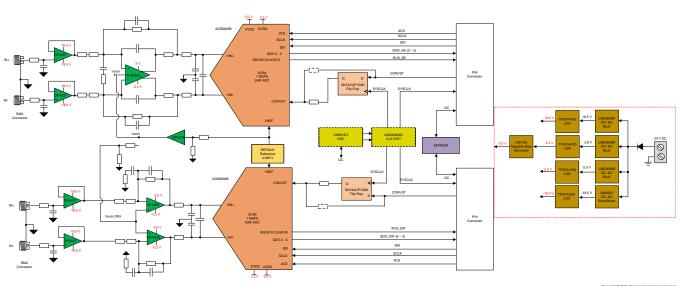

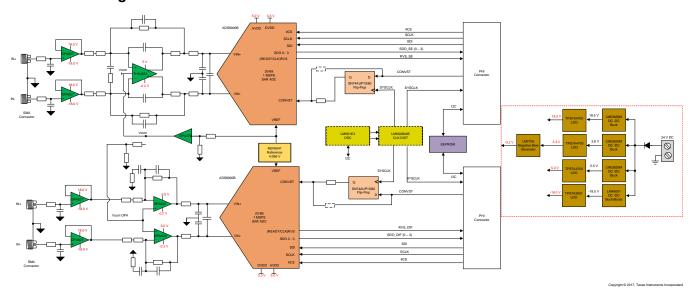

Figure 2. TIDA-01056 System Block Diagram

This reference design focuses on optimizing power supply efficiency while minimizing the effect of the EMI generated from the system buck converters powering the AFE and 20-bit, 1-MSPS successive approximation register (SAR) ADC. This design compares the efficiency of the LM53635 buck converter, which switches at 2.1 MHz and is used in this reference design, to the LMS3635 buck converter, which has a 400-kHz switching frequency. As both devices use the HotRod™ package and butterfly layout, designers can directly observe the effects of switching frequency on both EMI and efficiency.

# 2.2 Highlighted Products

# 2.2.1 LMS3635-Q1

The function of the LMS3635M in this design is to bring the 24-V input voltage down to 3.8 V, 5.5 V, and 18.5 V in a highly efficient manner. This part is selected based on its superior efficiency at light load, low switching frequency, excellent EMI performance, and compact printed-circuit board (PCB) layout. The automotive-qualified HotRod QFN package reduces parasitic inductance and resistance while increasing efficiency, minimizing switch node ringing, and dramatically lowering EMI. Seamless transition between pulse-width modulation (PWM) and pulse-frequency modulation (PFM) modes, along with a low quiescent current, ensures high efficiency and superior transient responses at all loads.

## 2.2.2 TPS7A47

The TPS7A47 is designed with bipolar technology primarily for high-accuracy, high-precision instrumentation applications where clean voltage rails are critical to maximize system performance. This feature makes the device ideal for powering operational amplifiers, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and other high-performance analog circuitry in critical applications such as medical, radio frequency (RF), and test-and-measurement.

System Overview www.ti.com

# 2.3 System Design Theory

High-performance DAQ systems require low-power consumption while minimizing EMI from switching regulators to prevent from impacting the performance of high-resolution ADCs. The following subsection describes optimizing the power supply stage using the LMS3635-Q1 and provides measurement results and a comparison of the efficiency, SNR, total harmonic distortion (THD), and SFDR.

#### 2.3.1 AFE and SAR ADC

This reference design consists of an AFE with two channels. Both channels are similar, with the exception of the ADC driver architecture. The first channel uses the THS4551, a fully differential amplifier specifically designed to be used with high-performance SAR ADCs. The second channel uses dual OPA625 amplifiers, which are wired to work as a fully differential amplifier. These amplifiers drive the ADS8900B SAR ADC, a 20-bit, high-precision, high-speed data converter. The AFE and SAR ADC are the key aspects of this design for working with DAQ systems; however, these devices are not the main focus of this design. To learn more about the design theory of the AFE and SAR ADC, see *ADC Driver Reference Design Improving Full-Scale THD Using Negative Supply*.

## 2.3.2 Power Structure

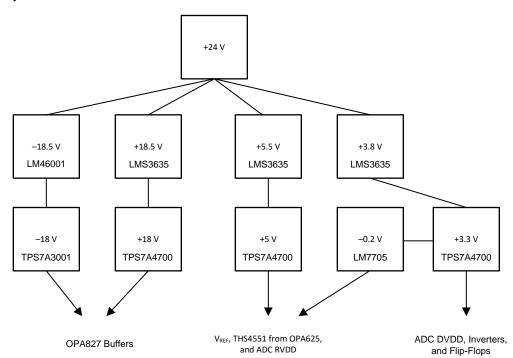

This system requires a wide variety of voltage rails to meet the specification of the reference design. The input voltage required for the system is 24-V DC. The power tree in Figure 3 highlights the distribution of the power into the different required rails. To create these rails, this design contains the LMS3635-Q1 high-efficiency buck converter. This solution is compared to the LM53635 to show the improvement in efficiency.

Figure 3. System Power Tree

www.ti.com System Overview

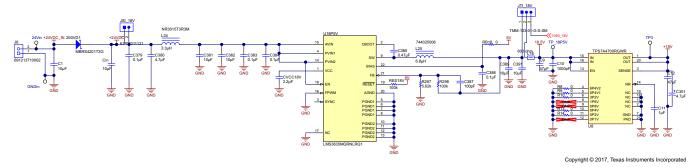

## 2.3.2.1 LMS3635-Q1 Circuitry

Figure 4 shows the 18-V rail circuitry with the LMS3635-Q1; each rail is structured the same way, with the only difference being the different passive component values. The input of the buck is connected to the 24-V supply by a two-pin header. This header allows the user to leave unused bucks powered off, which is critical to the testing performed on the reference design. The buck converter is followed by an LDO to remove the switching noise. The input of the LDO is connected to a three-pin header. The other two pins of this header are connected to the outputs of both buck converter options. This header is used in conjunction with the two-pin header to properly connect the buck, for which the intention is to use with the LDO. The three-pin header allows the use of only one LDO for each rail, which improves space efficiency and also helps with certain aspects of testing and debugging.

Figure 4. LMS3635-Q1 Schematic

## 2.3.3 LMS3635-Q1 Switching Noise

Buck converters produce output voltage ripple, which is also known as switching noise. Many different factors involving the switching regulator determine the amplitude of this ripple, which can be high enough to cause issues with devices powered by this buck converter. Because this reference design uses noise-sensitive devices such as the 20-bit ADC, a high-voltage ripple can have a detrimental effect on signal integrity. An LDO is placed at the output of the switching regulator to remove the switching noise and circumvent such an occurrence.

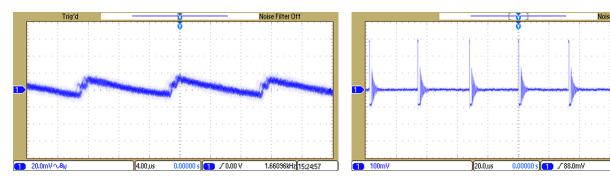

The following calculations and simulations show the importance of connecting the LDO to remove the switching frequency. The output voltage ripple and switching frequency ( $f_s$ ) for the buck in the 5-V rail (the rail powering the RVDD of the ADC,  $V_{REF}$ , OPA625, and THS4551) was measured to be approximately 30 mV and 30 kHz (see Figure 5 and Figure 6, respectively).

Figure 5. Output Ripple of LMS3635-Q1 (5-V Rail)

Figure 6. Switching Waveform of LMS3635-Q1 (5-V Rail)

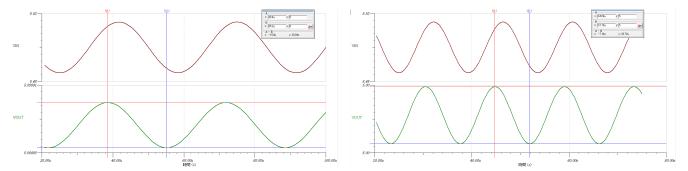

The buck is designed to output 5.5 V, which is just above the dropout of the LDO, to minimize the efficiency loss. A TINA-TI<sup>TM</sup> simulation model is created for the TPS7A4700 LDO with a 5.5-V DC level and a sine wave input of 30 mV<sub>pk-pk</sub>, 30 kHz (simulating the output of the LMS3635 device with ripple). A steady-state analysis provided the output of the LDO, which Figure 7 shows.

System Overview www.ti.com

As for the LM53635—because the output current of the 5.5-V rail is measured as 20 mA—its switching frequency must be around 70 kHz, as evidenced from the *Switching Frequency vs Load Current* graph in *LM53625/35-Q1*, 2.5-A or 3.5-A, 36-V Synchronous, 2.1-MHz, Step-Down DC-DC Converter. Figure 8 shows the LDO simulation result, which was obtained under the same DC level and amplitude as the LMS3635 device.

Figure 7. LDO Simulation V<sub>IN</sub> from LMS3635 for 5-V Rail

Figure 8. LDO Simulation V<sub>IN</sub> from LM53635 for 5-V Rail

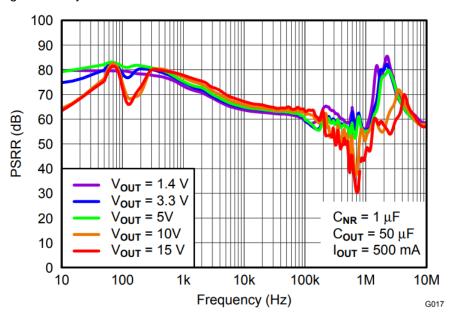

After the LDO, the peak-to-peak switching noise of the LMS3635-Q1 and LM53635 are 20.04  $\mu$ V and 33.72  $\mu$ V, respectively. Because the LDO has an improved power supply rejection ratio (PSRR) at lower frequencies (see Figure 9), the ripple rejection of the LMS3635-Q1 (30-kHz switching) is 41% superior to the LM53635 (70-kHz switching). Thus, from a ripple and EMI perspective, the LMS3635-Q1 is more suitable for high-accuracy DAQ.

Figure 9. PSRR of TPS7A47x

The LDO effectively reduces the switching ripple noise by a factor of 1497. Further calculations are made to observe the noise present at the ADC using the output voltage ripple of the LMS3635-Q1 device. Compare this result to the result of using the output voltage ripple of the TPS7A4700 in the same calculations. This ripple voltage without the LDO goes to both the OPA625 and THS4551 devices. The THS4551 has a PSRR of 110 dB at 30 kHz and a gain of 1. Equation 1 shows that the PSRR is equal to:

$$PSSR(dB) = -20 \log_{10} \left( \frac{\Delta V_{OS}}{\Delta V_{SUPPLY}} \right)$$

(1)

www.ti.com System Overview

Because this system has a gain of 1, the total noise gain on the non-inverting terminal is 1 + 1. This is a gain of 6 dB. The total PSRR for the THS4551 is approximately 104 dB for this system. This value is equal to 0.00000631 V/V. The amount of power supply noise coupled to the ADC data lines is calculated using Equation 2:

$$30 \text{ mV} \times 0.00000631 = 189.3 \text{ nV}$$

(2)

Compare this noise value to the least significant bit (LSB) value of the ADC to observe the effect it has on signal integrity. Calculate the value of 1 LSB for a 20-bit differential input ADC with 4.096 V as a reference voltage using Equation 3 and Equation 4:

$$\frac{2 \times 4.096}{2^{20}} = 7.812 \,\mu\text{V} \tag{3}$$

$$\frac{189.3 \,\text{nV}}{7.812 \,\mu\text{V}} \times 100 = 2.42\% \,\text{LSB} \tag{4}$$

Because the ADS8900B has a differential input, the full-scale input range (FSR) is twice the reference voltage. To determine the LSB of the differential input ADC, see the section regarding the *ADC Transfer Function* in *ADS890xB 20-Bit*, *High-Speed SAR ADCs With Integrated Reference Buffer, and Enhanced Performance Features*. The OPA625 has a power supply rejection ratio of 77 dB at 30 kHz. At a gain of 1, the PSRR is equal to 71 dB. This value is equivalent to 0.00028 V/V. Equation 5 and Equation 6 calculate the power supply noise present at the ADC driven by the OPA625 device:

$$30 \text{ mV} \times 0.00028 = 8.46 \,\mu\text{V}$$

(5)

$$\frac{8.46\,\mu\text{V}}{7.812\,\mu\text{V}} \times 100 = 108\% \,\text{LSB} \tag{6}$$

With a 2.42% LSB present at the ADC, the THS4551 signal chain is not greatly impacted by excluding the LDO. However, the OPA625 signal chain has more than 1 LSB of power supply noise present at the ADC without the LDO. This above 1 LSB noise value causes missing code and creates a huge negative impact on the output data of the ADC. Using the LDO output ripple of 20.04  $\mu$ V and the same equations, the amount of power supply noise coupled to the ADC data lines for the ADC driven by the THS4551 is:

$$20.04 \,\mu\text{V} \times 0.00000631 = 126.4 \,\text{pV}$$

(7)

$$\frac{126.4 \,\mathrm{pV}}{7.812 \,\mathrm{\mu V}} \times 100 = 0.0016\% \,\mathrm{LSB} \tag{8}$$

This highlights that the amount of noise on the 5-V rail is much less than 1% of the LSB value of the ADC. The amount of power supply noise present at the ADC of the OPA625 is:

$$20.04 \,\mu\text{V} \times 0.00028 = 5.65 \,\text{nV}$$

$$\frac{5.65 \,\text{nV}}{7.812 \,\mu\text{V}} \times 100 = 0.072\% \,\text{LSB} \tag{10}$$

When using the LDO, both the THS4551 and OPA625 signal chain ADCs have much less than 1% LSB of noise present at their power supply inputs. This specification ensures that there is no negative impact on signal integrity with the LDO present in the system. This test concludes that the LDO is necessary in the power rail circuits to generally remove any system performance degradation as a result of switching noise.

System Overview www.ti.com

## 2.3.4 LMS3635-Q1 EMI

One of the goals for this design is to eliminate any system performance degradation due to EMI for high-performance DAQ systems. Buck converters are the main source of unwanted spur production throughout the spectrum due to their harsh switching components. The LMS3635-Q1 is a great solution for this problem because many of its features focus on reducing EMI.

## 2.3.4.1 HotRod™ Packaging

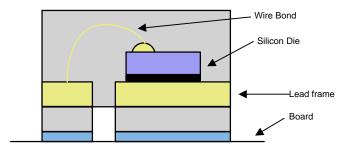

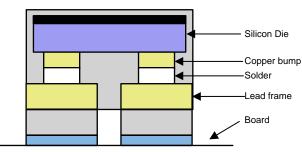

The biggest factor that helps the LMS3635-Q1 reduce EMI is the HotRod Flip-Chip-on-Leadframe (FCOL) packaging, which Figure 11 shows. This package style flips the die over and uses copper bumps to connect directly to the leads, thus eliminating the requirement for a wire bond (see Figure 10). Removing this wire bond reduces the parasitics, which dramatically lowers the switch node ringing. This ringing is a major source of EMI for buck converters using the standard wire-bond packaging.

Figure 10. Standard Wire-Bond QFN

Figure 11. HotRod™ FCOL QFN

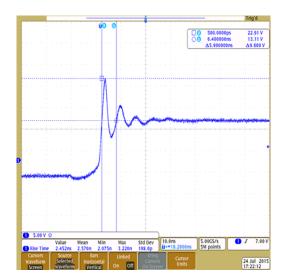

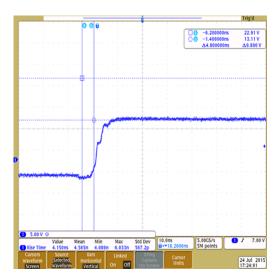

Figure 12 and Figure 13 show the difference between switch node ringing for a wire-bond package and a HotRod package. The ringing overshoot reduces from 9 V to 0 V, which lowers the overall EMI and noise. The HotRod packaging helps to reduce EMI and allows for a smaller size and reduced R<sub>DS\_ON</sub>, which improves the efficiency.

Figure 12. LM53603 TSSOP

Figure 13. LM53635-Q1 FCOL

# 3 Hardware, Software, Testing Requirements, and Test Results

# 3.1 Required Hardware

This section outlines the information for getting the board up and running quickly. To learn about the precision host interface (PHI) board or the onboard clocking and jitter cleaner, see *Optimized Analog Front-End DAQ System Reference Design for 18-Bit SAR Data Converters*. Take care when moving jumper pins to avoid possible damage to the components.

# 3.1.1 Jumper Configuration

This system has several configurable power options. These options are selectable through using two-pin and three-pin jumpers. Table 2 highlights the purpose of each jumper and assists in changing the configuration to fit the user requirements.

**Table 2. Jumper Configuration**

| JUMPER NAME                                    | SHORT PINS 1 AND 2                                | SHORT PINS 2 AND 3                              | DEFAULT CONFIGURATION |  |

|------------------------------------------------|---------------------------------------------------|-------------------------------------------------|-----------------------|--|

| JSI_18V                                        | 8V Power to LMS3635-Q1 18-V rail —                |                                                 | Short                 |  |

| JTI_18V                                        | Connects LMS3635-Q1 to TPS7A700 for 18-V rail     | Connects LMZ14201 to<br>TPS7A700 for 18-V rail  | Short pins 1 and 2    |  |

| JSI_5V                                         | Power to LMS3635-Q1 5-V rail                      | _                                               | Short                 |  |

| JTI_5V                                         | Connects LMS3635-Q1 to<br>TPS7A700 for 5-V rail   | Connects LMZ14203 to<br>TPS7A700 for 5-V rail   | Short pins 1 and 2    |  |

| JSI_3.3V                                       | Power to LMS3635-Q1 3.3-V rail —                  |                                                 | Short                 |  |

| JTI_3.3V                                       | Connects LMS3635-Q1 to<br>TPS7A700 for 3.3-V rail | Connects LMZ14202 to<br>TPS7A700 for 3.3-V rail | Short pins 1 and 2    |  |

| JPRI18V                                        | Power to LM46001 –18-V rail                       | _                                               | Short                 |  |

| JTI18V                                         | Connects LM46001 to TPS7A3001 for –18-V rail      | Connects LM5574 to<br>TPS7A3001 for –18-V rail  | Short pins 1 and 2    |  |

| JMTI18V                                        | Power to LM5574 –18-V rail                        | _                                               | Open                  |  |

| JZI_18V                                        | Power to LMZ14201 18-V rail                       | _                                               | Open                  |  |

| JZI_3.3V                                       | Power to LMZ14202 3.3-V rail                      | _                                               | Open                  |  |

| JZI_5V                                         | Power to LMZ14203 5-V rail                        | _                                               | Open                  |  |

| J39 Connects –0.2-V rail to OPA625 and THS4551 |                                                   | Shorts –0.2-V rail to ground Short pins 1 and 2 |                       |  |

# 3.2 Testing and Results

# 3.2.1 Efficiency

The efficiency of each buck converter (3.8 V, 5.5 V, and 18.5 V) was evaluated with those devices implemented on the system board. Because the LMS3635-Q1 is capable of superior light load mode, it has an overall better efficiency than the LM53635. Specifically, at a 15.7-mA output current (see Table 3), the efficiency improved by 7.2% (89/83-1).

| VOLTAGE<br>SOURCE | OUTPUT<br>VOLTAGE (V) | OUTPUT<br>CURRENT (mA) | INPUT<br>VOLTAGE (V) | INPUT<br>CURRENT (mA) | EFFICIENCY (%) |

|-------------------|-----------------------|------------------------|----------------------|-----------------------|----------------|

| LMS3635-Q1        | 3.804                 | 184                    | 24                   | 33                    | 88             |

|                   | 5.488                 | 20.1                   | 24                   | 5.26                  | 87             |

|                   | 19.077                | 15.7                   | 24                   | 14                    | 89             |

| LM53635-Q1        | 3.813                 | 184                    | 24                   | 34                    | 86             |

|                   | 5.492                 | 20.1                   | 24                   | 5.26                  | 87             |

|                   | 19.093                | 15.7                   | 24                   | 15                    | 83             |

**Table 3. Efficiency Evaluation Results**

### 3.2.2 EMI Matters

An Audio Precision 2700 series signal generator is used as the signal source to test the AFE and ADC performance. The noise and THD of the AP2700 have adequate performance and do not limit measurements or system performance. A generic DC power supply is used to generate the 24-V DC input voltage.

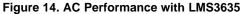

A PHI controller board is used to connect the TIDA-01056 board to the host PC, where the ADS8900B EVM GUI functions. This software allows the designer to measure SNR, THD, SFDR, signal-to-noise and distortion ratio (SINAD), and ENOB for the ADC by running a spectral analysis. The AP2700 is set to output a 2-kHz 8- $V_{pk-pk}$  sinusoid. A value of 2 kHz is chosen because it is the standard frequency when measuring noise and THD, and 8- $V_{pk-pk}$  grants full range on the THS4551 or OPA625 devices, thus granting a full range of 0 to the  $V_{REF}$  for the ADC.

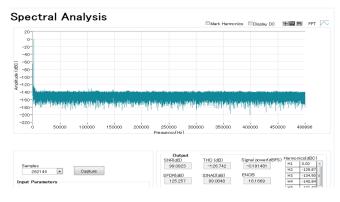

AC performance was measured for both the LMS3635-Q1 and LM53635-Q1 devices (see Figure 14 and Figure 15). The LMS3635 slightly outperformed the LM53635 by almost 1 dB in SFDR. According to *Multi-Rail Power Reference Design for Eliminating EMI Effects in High-Performance DAQ Systems*, the LMS3635 gives a comparable performance to the same system with external power supplies. Thus, the LMS3635 device can reduce power consumption and reduce voltage ripple while minimizing the effect of EMI from switching noise.

Figure 15. AC Performance with LM53635

www.ti.com Design Files

# 4 Design Files

### 4.1 Schematics

To download the schematics, see the design files at TIDA-01056.

### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01056.

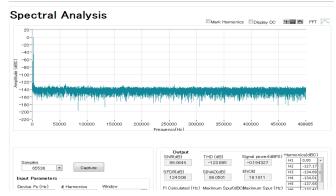

# 4.3 PCB Layout Recommendations

The LMS3635-Q1 has certain layout guidelines that help to reduce EMI. Figure 16 shows how the LMS3635-Q1 and its additional components must be placed in the layout.

Figure 16. LMS3635-Q1 Layout Guidelines

Putting the input and output capacitors in this configuration creates parallel capacitance loops, thus minimizing the inductance. This placement then reduces the switch node ringing and lowers the overall EMI emissions. TI also recommends leaving the ground plane unbroken under the device. This placement provides the shortest return path possible, minimizing EMI generated by the loop. For more layout recommendations regarding the AFE or SAR ADC, see *Optimized Analog Front-End DAQ System Reference Design for 18-Bit SAR Data Converters*.

# 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01056.

# 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01056.

## 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01056.

Design Files www.ti.com

# 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01056.

## 5 Software Files

To download the software files, see the design files at TIDA-01056.

### 6 Related Documentation

- 1. Texas Instruments, ADC Driver Reference Design Improving Full-Scale THD Using Negative Supply

- 2. Texas Instruments, ADS890xB 20-Bit, High-Speed SAR ADCs With Integrated Reference Buffer, and Enhanced Performance Features

- 3. Texas Instruments, Multi-Rail Power Reference Design for Eliminating EMI Effects in High-Performance DAQ Systems

- 4. Texas Instruments, Optimized Analog Front-End DAQ System Reference Design for 18-Bit SAR Data Converters

# 6.1 Trademarks

HotRod, TINA-TI are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

## 7 About the Authors

**SHOTA MAGO** is a field application engineer at Texas Instruments, where he is responsible for supporting Japanese industrial companies and proposing solutions for them. Shota obtained his bachelor's degree and master of electrical and electronic engineering from the University of Miyazaki in Japan.

**TARAS DUDAR** is a systems design engineer and architect at Texas Instruments, where he is responsible for developing reference design solutions for the test and measurement industry. Previously, Taras designed high-speed analog SOC integrated circuits for Gbps data communications. Taras earned his master of science in electrical engineering (MSEE) degree from the Oregon State University in Corvallis, OR.

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated