## User's Guide TPS62050 and TPS62052 Buck Converter Evaluation Module User's Guide

# TEXAS INSTRUMENTS

## **Table of Contents**

| 1 Introduction                                    | 2 |

|---------------------------------------------------|---|

| 2 Evalulation with the TPS6205xEVM                |   |

| 2.1 Enable (EN) Jumper                            |   |

| 2.2 Synchronization (SYNC) Jumper                 | 3 |

| 2.3 Power Good (PG)                               | 3 |

| 2.4 Low Battery Out (LBO)                         |   |

| 3 PCB Layout                                      |   |

| 3.1 SLVP234 EVM Schematic and Bill of Materials   | 4 |

| 3.2 PCB Layout of the TPS62050EVM and TPS62052EVM | 5 |

| 4 Revision History                                |   |

|                                                   |   |

#### Trademarks

All trademarks are the property of their respective owners.

## **1** Introduction

The Texas Instruments TPS62050 and TPS62052 evaluation modules (EVM) for low-power, high-efficiency, step-down converters help designers evaluate these devices. The EVMs make it possible to evaluate different modes of the devices as well as the device performance.

The TPS6205xEVM is available as the TPS62050 adjustable version set to 3.3 V and the TPS62052 1.5-V fixed version.

The TPS62050EVM can be easily set up to provide any output voltage between 0.7 V to 6 V (or Vin) by adjusting the external resistor divider. Refer to the data sheet (SLVS432) for various fixed voltage options available for the TPS6205x. The TPS6205x has an input voltage range between 2.7 V and 10 Vwith an output current up to 800 mA.

Any version of the TPS6205x can be evaluated by removing and replacing the IC on the EVM.

| EVM NUMBER DESCRIPTION |                                                |  |  |

|------------------------|------------------------------------------------|--|--|

| TPS62050EVM-234        | Adjustable output voltage version set to 3.3 V |  |  |

| TPS62052EVM-234        | 1.5-V fixed output voltage version             |  |  |

#### Table 1-1. EVM Ordering Information

## 2 Evalulation with the TPS6205xEVM

This section details the evaluation process and features of the EVM. For this purpose, a load is connected to the output pins Vout and GND, which allows the load current to be adjusted between 0 mA and 800 mA.

For accurate output voltage and input voltage measurements, it is important to measure the voltage on the input and output voltage terminals with avoltmeter connected directly to the input voltage or output voltage terminals. This eliminates any measurement errors related to voltage drops along the input and output terminal wires connected to the power supply or load.

#### 2.1 Enable (EN) Jumper

This jumper is used to enable the device. Connecting the EN pin to ON enables the part. Connecting the EN pin to OFF disables the device.

#### 2.2 Synchronization (SYNC) Jumper

This jumper is used to choose between PWM and PFM/PWM modes of operation. Setting the jumper across PWM forces the device into the low-noise fixed-frequency pulse width modulation (PWM) mode. Setting the jumper across PWM/PFM enables the power save mode where the device enters apulse frequency modulation mode (PFM) at light to medium load currents, which reduces quiescent current and switching frequency to a minimum to achieve highest efficiency over the entire load current range.

Additionally an external clock between 600 kHz and 1200 kHz can be applied to pin 2 of J2 (SYNC) in order to synchronize the converter to an external clock.

#### 2.3 Power Good (PG)

The PG pin is an open drain output capable of sinking typically 1 mA. A pullup resistor is required to use the PG. The pullup resistor should be placed between the Vout and PG. The PG pin becomes active high when the output voltage exceeds typically 98.5% of its nominal value. Leave the PG pin unconnected when not used.

#### 2.4 Low Battery Out (LBO)

The LBO pin is an open drain output which goes low when the voltage at the low battery input (LBI) falls below the trip point of 1.21 V. An external pullup resistor which is placed between LBO and Vout is required to use the LBO.

## 3 PCB Layout

As for all switch mode power supplies, the PCB layout is a very important step in the power supply design process. The following figures show the layout for the adjustable and fixed output voltage EVMs.

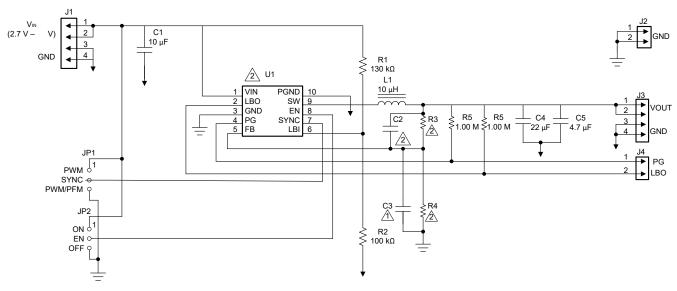

### 3.1 SLVP234 EVM Schematic and Bill of Materials

Figure 3-1 shows the SLVP234 EVM schematic diagram. The bill of materials for the TPS62050EVM and TPS62052EVM is shown in Table 3-1. More details about the design and component selection for the dc-dc converter can be found in the data sheet.

| COUNT    |          | REF DES | DESCRIPTION                                          | SIZE | MFR     | PART NUMBER           |

|----------|----------|---------|------------------------------------------------------|------|---------|-----------------------|

| TPS62050 | TPS62052 |         |                                                      |      |         |                       |

| 1        | 1        | C1      | Capacitor,Ceramic<br>, 10 mF,16 V, X5R,<br>10%       |      | Murata  | GRM32ER61C106<br>KC31 |

| 1        | open     | C2      | Capacitor,ceramic,<br>22 pF, 50 V, C0G,<br>5%        | 603  | Murata  | GRM1885C1H220<br>JZ01 |

| open     | open     | C3      | Capacitor,ceramic,<br>xx mF,xx mV                    | 603  |         |                       |

| 1        | 1        | C4      | Capacitor,<br>ceramic, 22 mF,<br>6.3–V, X5R,10%      | 1210 | Murata  | GRM32DR60J226<br>KA01 |

| 1        | 1        | C5      | Capacitor,ceramic,<br>4.7 mF,6.3 V,<br>X5R,10%       | 805  | Murata  | GRM219R60J475<br>KE11 |

| 2        | 2        | J1,J3   | Header,4 pin, 100<br>mil spacing, (36-<br>pin strip) | 0.12 | Sullins | PTC36SAAN             |

| 2        | 2        | J2,J4   | Header,2 pin, 100<br>mil spacing, (36-<br>pin strip) | 0.12 | Sullins | PTC36SAAN             |

| 2        | 2        | JP1,JP2 | Jumper,3 pin, 100<br>mil spacing, (36-<br>pin strip) | 0.12 | Sullins | PTC36SAAN             |

#### Table 3-1. TPS62050 and TPS62052 EVMs (SLVP234) Bill of Materials

| COUNT    |          | REF DES | DESCRIPTION                                              | SIZE    | MFR | PART NUMBER          |

|----------|----------|---------|----------------------------------------------------------|---------|-----|----------------------|

| TPS62050 | TPS62052 |         |                                                          |         |     |                      |

| 1        | 1        | L1      | Inductor,SMT, 10<br>mH,1.4 A, 63.6<br>mW                 | 0.276sq | TDK | SLF7032T-<br>100M1R4 |

| 1        | 1        | R1      | Resistor,chip, 130<br>kW,1/16 W, 1%                      | 603     | Std | Std                  |

| 1        | 1        | R2      | Resistor,chip, 100<br>kW,1/16 W, 1%                      | 603     | Std | Std                  |

| 1        |          | R3      | Resistor,chip, 562<br>kW,1/16 W, 1%                      | 603     | Std | Std                  |

|          | 1        |         | Resistor,chip, 0<br>W,1/16 W, 5%                         | 603     | Std | Std                  |

| 1        | open     | R4      | Resistor,chip, 100<br>kW,1/16 W, 1%                      | 603     | Std | Std                  |

| 1        | 1        | R5      | Resistor,chip, 1.00<br>MW,1/16 W, 1%                     | 603     | Std | Std                  |

| 1        | 1        | R6      | Resistor,chip, 1.00<br>MW,1/16 W, 1%                     | 603     | Std | Std                  |

| 1        |          | U1      | IC, high-<br>efficiencystep-<br>down converter,<br>Adj V | DGS10   | ТІ  | TPS62050DGS          |

|          | 1        |         | IC, high-<br>efficiencystep-<br>down converter,<br>1.5 V | DGS10   | ТІ  | TPS62052DGS          |

| 1        | 1        | -       | PCB,1.6 ln ´<br>1.255ln ´ 0.062ln                        |         | Any | SLVP234              |

| 2        | 2        | -       | Shunt,100 mil,<br>black                                  | 0.100   | 3M  | 929950-00            |

#### 24 TDS62050 and TDS62052 EVMs (SLVD234) Bill of Matorials (continued)

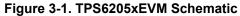

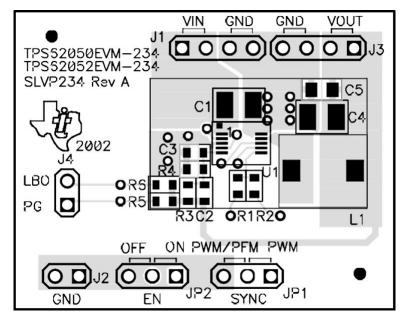

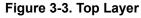

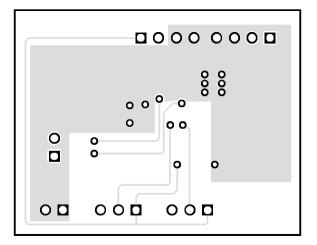

#### 3.2 PCB Layout of the TPS62050EVM and TPS62052EVM

The following figures show the layout for the adjustable and fixed output voltage EVMS.

Figure 3-2. Component Placement

Figure 3-4. Bottom Layer

#### **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision * (February 2003) to Revision A (July 2021)                               | Page |

|---|------------------------------------------------------------------------------------------------|------|

| • | Updated the numbering format for tables, figures, and cross-references throughout the document | 2    |

| • | Updated user's guide title                                                                     | 2    |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated