# TMS320C6000 DSP External Memory Interface (EMIF)

# Reference Guide

Literature Number: SPRU266E April 2008

# **Contents**

| Prefa | ce                                                                      | 11 |  |  |  |  |  |

|-------|-------------------------------------------------------------------------|----|--|--|--|--|--|

| 1     | Overview                                                                | 13 |  |  |  |  |  |

| 1.1   | Overview                                                                | 14 |  |  |  |  |  |

| 1.2   | Command-to-Command Turnaround Time                                      |    |  |  |  |  |  |

| 1.3   | SDRAM Interface                                                         | 15 |  |  |  |  |  |

|       | 1.3.1 SDRAM Initialization                                              | 19 |  |  |  |  |  |

|       | 1.3.2 Monitoring Page Boundaries                                        | 19 |  |  |  |  |  |

|       | 1.3.3 SDRAM Refresh Mode                                                | 20 |  |  |  |  |  |

|       | 1.3.4 SDRAM Deactivation (DCAB and DEAC)                                | 21 |  |  |  |  |  |

|       | 1.3.5 SDRAM Activation (ACTV)                                           | 23 |  |  |  |  |  |

| 1.4   | SBSRAM Interface                                                        | 24 |  |  |  |  |  |

| 1.5   | Asynchronous Interface                                                  | 26 |  |  |  |  |  |

|       | 1.5.1 Programmable ASRAM Parameters                                     | 28 |  |  |  |  |  |

|       | 1.5.2 Asynchronous Reads                                                | 28 |  |  |  |  |  |

|       | 1.5.3 Asynchronous Writes                                               | 30 |  |  |  |  |  |

|       | 1.5.4 Ready Input                                                       |    |  |  |  |  |  |

|       | 1.5.5 C620x/C670x DSP Illegal Access to Asynchronous Memory             |    |  |  |  |  |  |

| 1.6   | Resetting the EMIF                                                      |    |  |  |  |  |  |

|       | 1.6.1 Valid EMIF Clock During Reset                                     |    |  |  |  |  |  |

| 1.7   | Hold Interface                                                          |    |  |  |  |  |  |

|       | 1.7.1 TMS320C62x/C67x EMIF Reset Considerations With the Hold Interface |    |  |  |  |  |  |

|       | 1.7.2 TMS320C64x EMIF Reset Considerations With the Hold Interface      |    |  |  |  |  |  |

| 1.8   | Boundary Conditions When Accessing EMIF Registers                       |    |  |  |  |  |  |

| 1.9   | Clock Output Enabling                                                   |    |  |  |  |  |  |

| 1.10  | Emulation Halt Operation                                                |    |  |  |  |  |  |

| 1.11  | Power Down                                                              | 39 |  |  |  |  |  |

| 2     | TMS320C620x/C670x EMIF                                                  | 41 |  |  |  |  |  |

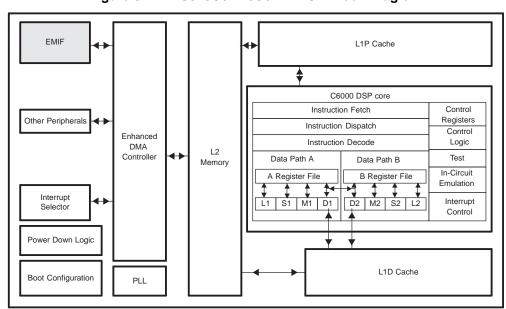

| 2.1   | Overview                                                                | 42 |  |  |  |  |  |

| 2.2   | EMIF Interface Signals                                                  | 43 |  |  |  |  |  |

|       | 2.2.1 C6201/C6701 EMIF                                                  |    |  |  |  |  |  |

|       | 2.2.2 C6202(B)/C6203(B)/C6204/C6205 EMIF                                |    |  |  |  |  |  |

| 2.3   | Memory Width and Byte Alignment                                         |    |  |  |  |  |  |

| 2.4   | SDRAM Interface                                                         | 46 |  |  |  |  |  |

|       | 2.4.1 C620x/C670x Bootmode                                              |    |  |  |  |  |  |

|       | 2.4.2 Monitoring Page Boundaries                                        |    |  |  |  |  |  |

|       | 2.4.3 Address Shift                                                     | 50 |  |  |  |  |  |

|       | 2.4.4 SDRAM Refresh Mode                                                |    |  |  |  |  |  |

|       | 2.4.5 Mode Register Set (MRS)                                           |    |  |  |  |  |  |

|       | 2.4.6 Timing Requirements                                               |    |  |  |  |  |  |

|       | 2.4.7 SDRAM Read                                                        |    |  |  |  |  |  |

|       | 2.4.8 SDRAM Write                                                       | 55 |  |  |  |  |  |

| 2.5 | SBSRAM Interface                                 | . 56 |

|-----|--------------------------------------------------|------|

|     | 2.5.1 SBSRAM Read                                | . 56 |

|     | 2.5.2 SBSRAM Write                               | . 57 |

| 2.6 | ROM Access Modes                                 | . 58 |

|     | 2.6.1 8-Bit ROM Mode                             | . 58 |

|     | 2.6.2 16-Bit ROM Mode                            | . 58 |

| 2.7 | Memory Request Priority                          | . 59 |

| 2.8 | EMIF Registers                                   | . 60 |

|     | 2.8.1 EMIF Global Control Register (GBLCTL)      | . 61 |

|     | 2.8.2 EMIF CE Space Control Registers (CECTL0-3) | . 63 |

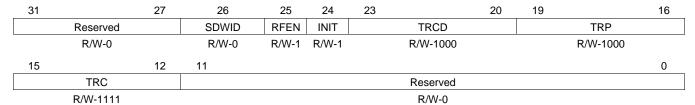

|     | 2.8.3 EMIF SDRAM Control Register (SDCTL)        | . 65 |

|     | 2.8.4 EMIF SDRAM Timing Register (SDTIM)         | . 66 |

| 3   | TMS320C621x/C671x EMIF                           | . 67 |

| 3.1 | Overview                                         | . 68 |

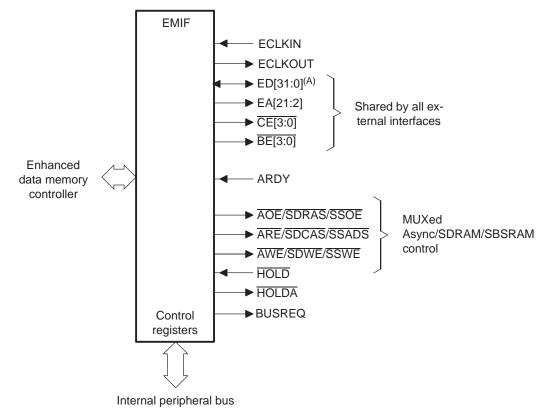

| 3.2 | EMIF Interface Signals                           | . 69 |

| 3.3 | Memory Width and Byte Alignment                  | . 71 |

| 3.4 | SDRAM Interface                                  | . 73 |

|     | 3.4.1 Monitoring Page Boundaries                 | . 75 |

|     | 3.4.2 Address Shift                              | . 77 |

|     | 3.4.3 SDRAM Refresh Mode                         | . 78 |

|     | 3.4.4 Mode Register Set (MRS)                    | . 78 |

|     | 3.4.5 Timing Requirements                        | . 80 |

|     | 3.4.6 SDRAM Read                                 |      |

|     | 3.4.7 SDRAM Write                                | . 82 |

| 3.5 | SBSRAM Interface                                 | . 83 |

|     | 3.5.1 SBSRAM Read                                | . 84 |

|     | 3.5.2 SBSRAM Write                               | . 85 |

| 3.6 | Memory Request Priority                          | . 86 |

| 3.7 | EMIF Registers                                   | . 86 |

|     | 3.7.1 EMIF Global Control Register (GBLCTL)      | . 87 |

|     | 3.7.2 EMIF CE Space Control Registers (CECTL0-3) | . 88 |

|     | 3.7.3 EMIF SDRAM Control Register (SDCTL)        |      |

|     | 3.7.4 EMIF SDRAM Timing Register (SDTIM)         | . 91 |

|     | 3.7.5 EMIF SDRAM Extension Register (SDEXT)      | . 91 |

| 4   | TMS320C64x EMIF                                  | 93   |

| 4.1 | Overview                                         |      |

| 4.2 | EMIF Interface Signals                           |      |

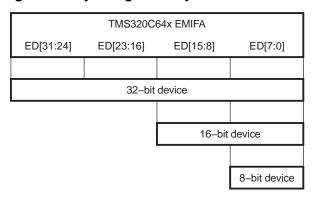

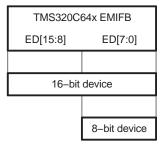

| 4.3 | Memory Width and Byte Alignment                  |      |

| 4.4 | SDRAM Interface                                  |      |

|     | 4.4.1 Monitoring Page Boundaries                 |      |

|     | 4.4.2 Address Shift                              |      |

|     | 4.4.3 SDRAM Refresh Mode                         |      |

|     | 4.4.4 SDRAM Self-Refresh Mode                    |      |

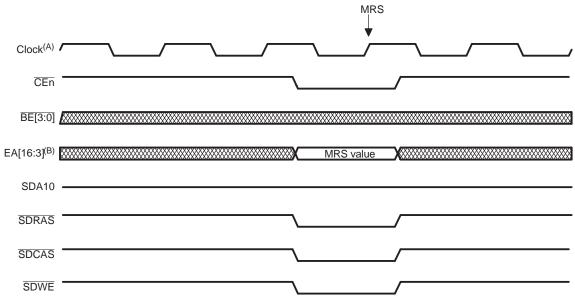

|     | 4.4.5 Mode Register Set (MRS)                    |      |

|     | 4.4.6 Timing Requirements                        |      |

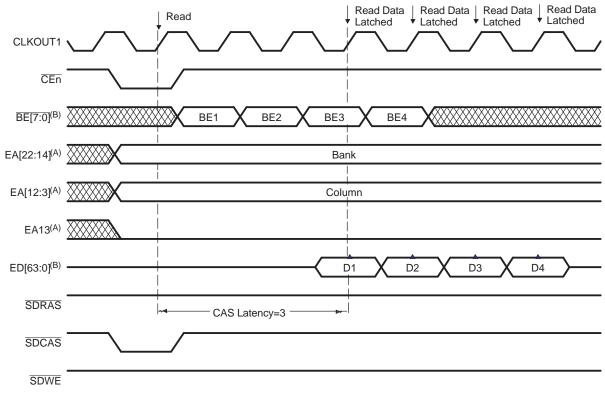

|     | 4.4.7 SDRAM Read                                 |      |

|     | 4.4.8 SDRAM Write                                |      |

| 4.5 | Programmable Synchronous Interface               |      |

| +.ט | 1 10grammable 3gricinonous intenace              | 100  |

### www.ti.com

| 4.8.7  | EMIF Peripheral Device Transfer Control Register (PDTCTL)                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0.0  | • , , ,                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

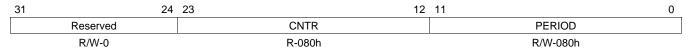

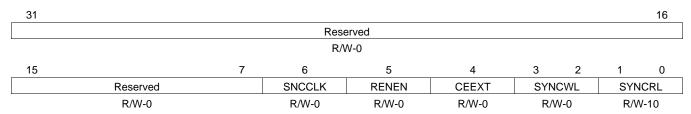

| 486    | EMIF SDRAM Extension Register (SDEXT)                                                                            | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.8.5  | EMIF SDRAM Timing Register (SDTIM)                                                                               | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.8.4  | EMIF SDRAM Control Register (SDCTL)                                                                              | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.8.3  | EMIF CE Space Secondary Control Registers (CESEC0-3)                                                             | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.8.2  | EMIF CE Space Control Registers (CECTL0-3)                                                                       | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.8.1  | EMIF Global Control Register (GBLCTL)                                                                            | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EMIF   | Registers                                                                                                        | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        |                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.6.3  | PDT Transfers with Multiple FIFOs on the Same Bus                                                                | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.6.2  | PDT Read                                                                                                         | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.6.1  | PDT Write                                                                                                        | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Periph | eral Device Transfer (PDT)                                                                                       | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.5.3  | Synchronous FIFO Interface                                                                                       | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.5.2  | Zero Bus Turnaround (ZBT) SRAM Interface                                                                         | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.5.1  | SBSRAM Interface                                                                                                 | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 4.5.2<br>4.5.3<br>Periph<br>4.6.1<br>4.6.2<br>4.6.3<br>4.6.4<br>Memo<br>EMIF<br>4.8.1<br>4.8.2<br>4.8.3<br>4.8.4 | 4.5.2 Zero Bus Turnaround (ZBT) SRAM Interface 4.5.3 Synchronous FIFO Interface Peripheral Device Transfer (PDT) 4.6.1 PDT Write 4.6.2 PDT Read. 4.6.3 PDT Transfers with Multiple FIFOs on the Same Bus 4.6.4 PDT Transfers: Bus Width and DMA Considerations.  Memory Request Priority  EMIF Registers. 4.8.1 EMIF Global Control Register (GBLCTL) 4.8.2 EMIF CE Space Control Registers (CECTL0-3) 4.8.3 EMIF CE Space Secondary Control Registers (CESEC0-3) 4.8.4 EMIF SDRAM Control Register (SDCTL) 4.8.5 EMIF SDRAM Timing Register (SDCTIM) |

# **List of Figures**

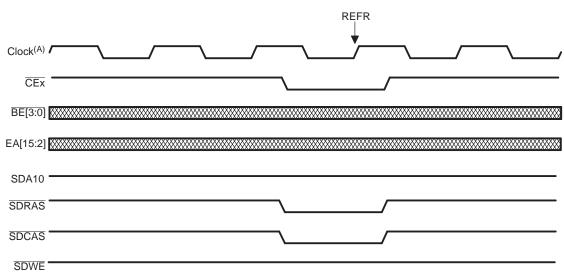

| 1-1  | SDRAM Refresh Timing Diagram                                                        | 20 |

|------|-------------------------------------------------------------------------------------|----|

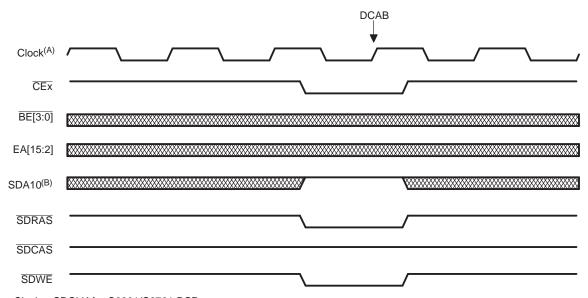

| 1-2  | TMS320C6000 SDRAM Deactivate All Banks (DCAB) Command Timing Diagram                | 21 |

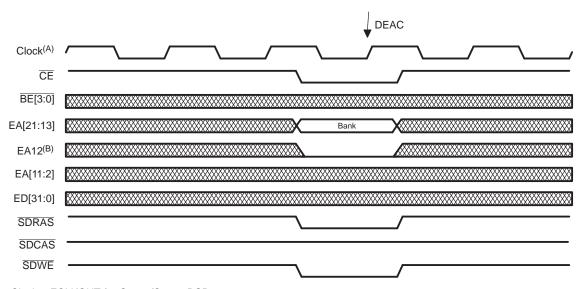

| 1-3  | TMS320C621x/C671x and TMS320C64x SDRAM Deactivate Single Bank (DEAC) Command Timing |    |

|      | Diagram                                                                             |    |

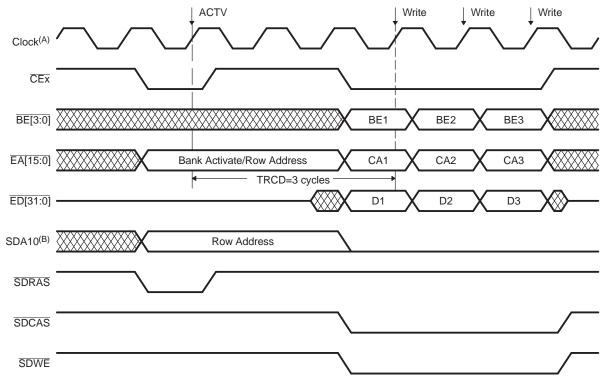

| 1-4  | TMS320C6000 SDRAM Activate (ACTV) Command Before an SDRAM Write Timing Diagram      |    |

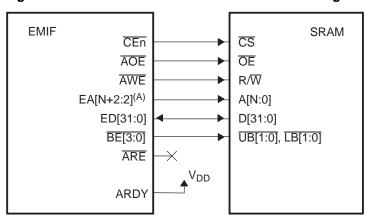

| 1-5  | EMIF to 32-bit SRAM Interface Block Diagram                                         |    |

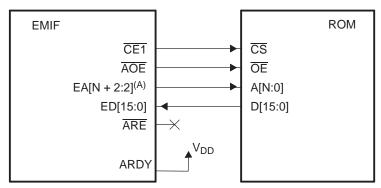

| 1-6  | EMIF to 8-Bit ROM Interface Block Diagram                                           |    |

| 1-7  | EMIF to 16-Bit ROM Interface Block Diagram                                          |    |

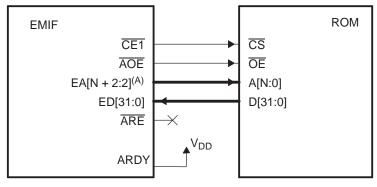

| 1-8  | EMIF to 32-Bit ROM Interface Block Diagram                                          | 27 |

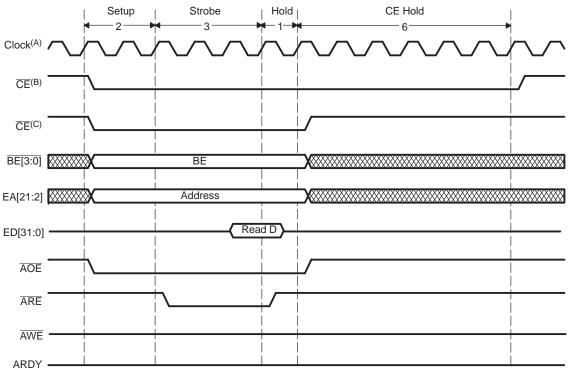

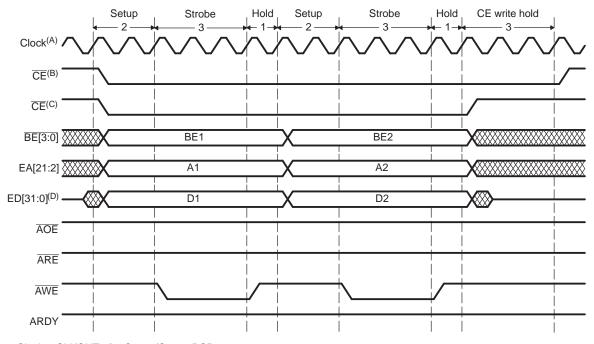

| 1-9  | Asynchronous Read Timing Diagram                                                    | 29 |

| 1-10 | Asynchronous Write Timing Diagram                                                   | 30 |

| 1-11 | TMS320C620x/C670x EMIF Ready Operation Timing Diagram                               | 32 |

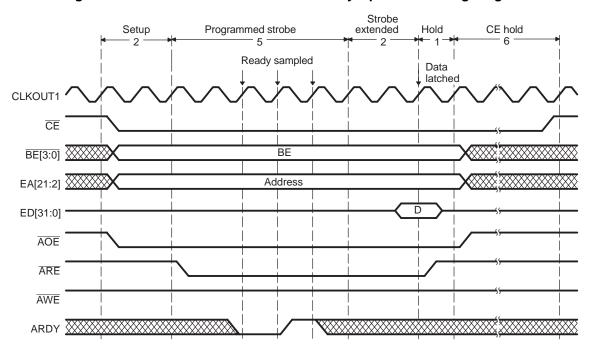

| 1-12 | TMS320C621x/C671x EMIF Ready Operation Timing Diagram                               | 33 |

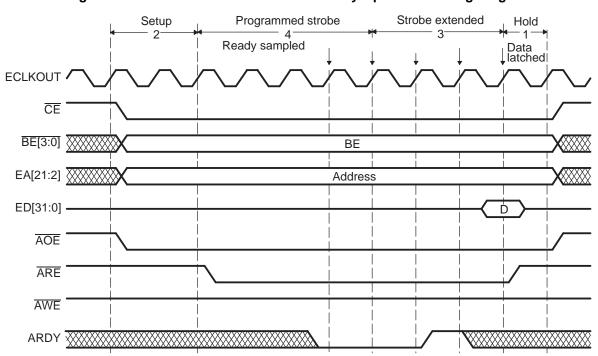

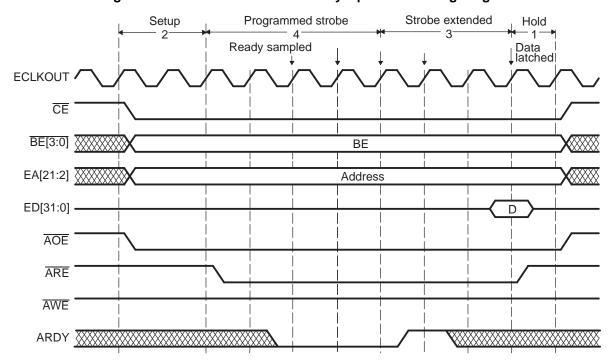

| 1-13 | TMS320C64x EMIF Ready Operation Timing Diagram                                      | 34 |

| 1-14 | TMS320C64x EMIF Clock Block Diagram                                                 | 38 |

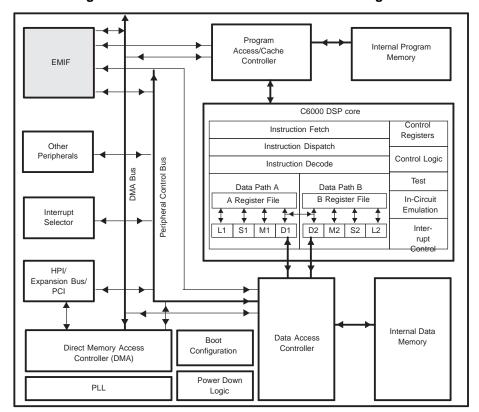

| 2-1  | TMS320C620x/C670x DSP Block Diagram                                                 | 42 |

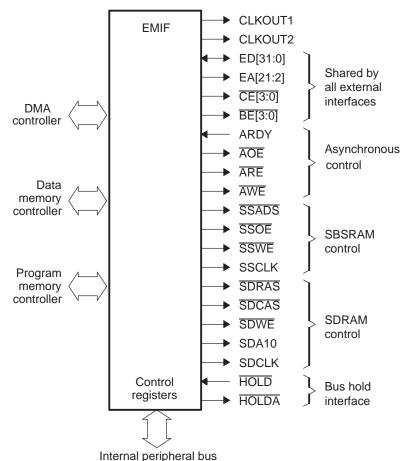

| 2-2  | TMS320C6201/C6701 EMIF Interface Signals                                            | 43 |

| 2-3  | TMS320C6202/C6203/C6204/C6205 EMIF Interface Signals                                | 44 |

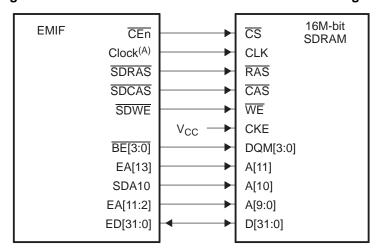

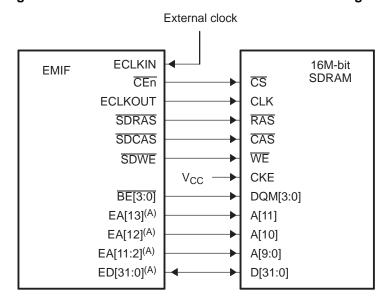

| 2-4  | EMIF to 16M-Bit SDRAM Interface Block Diagram                                       | 46 |

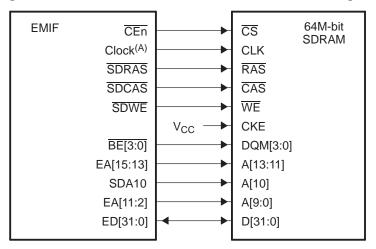

| 2-5  | EMIF to 64M-Bit SDRAM Interface Block Diagram                                       | 47 |

| 2-6  | Logical Address-to-Page Register Mapping                                            | 49 |

| 2-7  | Mode Register Value                                                                 | 52 |

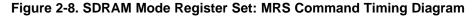

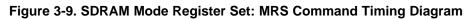

| 2-8  | SDRAM Mode Register Set: MRS Command Timing Diagram                                 | 53 |

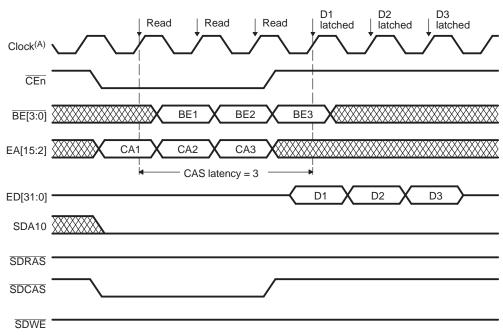

| 2-9  | SDRAM Read Timing Diagram                                                           | 54 |

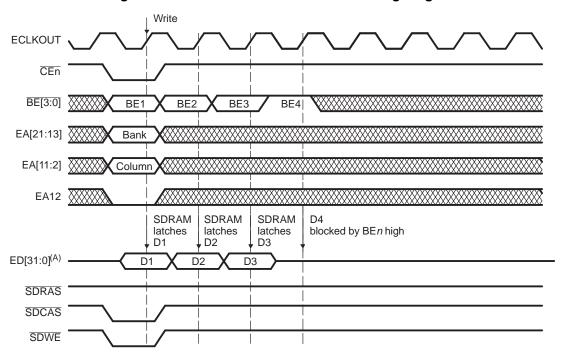

| 2-10 | SDRAM Three-Word Write Timing Diagram                                               | 55 |

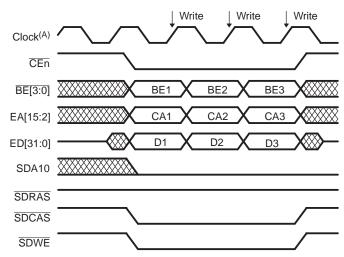

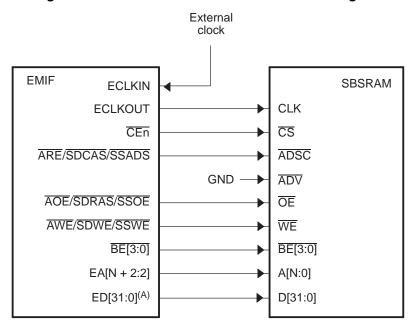

| 2-11 | EMIF to SBSRAM Interface Block Diagram                                              | 56 |

| 2-12 | SBSRAM Four-Word Read Timing Diagram                                                | 56 |

| 2-13 | SBSRAM Four-Word Write Timing Diagram                                               | 57 |

| 2-14 | EMIF Global Control Register (GBLCTL) (C6201/C6701 DSP)                             | 61 |

| 2-15 | EMIF Global Control Register (GBLCTL) (C6202/C6203/C6204/C6205 DSP)                 |    |

| 2-16 | EMIF CE Space Control Register (CECTL)                                              |    |

| 2-17 | EMIF SDRAM Control Register (SDCTL)                                                 | 65 |

| 2-18 | EMIF SDRAM Timing Register (SDTIM)                                                  |    |

| 3-1  | TMS320C621x/C671x DSP Block Diagram                                                 | 68 |

| 3-2  | TMS320C621x/C671x EMIF Interface Signals                                            | 69 |

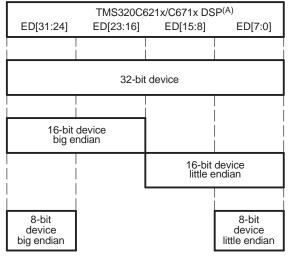

| 3-3  | Byte Alignment by Endianess - 32-Bit                                                | 71 |

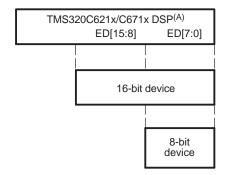

| 3-4  | Byte Alignment by Endianess - 16-bit                                                | 72 |

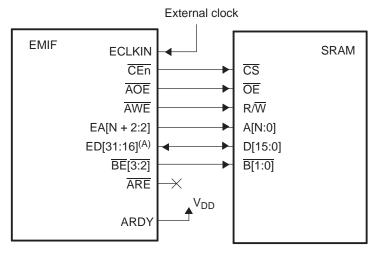

| 3-5  | TMS320C621x/C671x EMIF to 16-bit SRAM (Big Endian) Block Diagram                    | 72 |

| 3-6  | EMIF to 16M-Bit SDRAM Interface Block Diagram                                       |    |

| 3-7  | Logical Address-to-Page Register Mapping for 32-Bit Logical Address                 | 76 |

| 3-8  | Mode Register Value                                                                 |    |

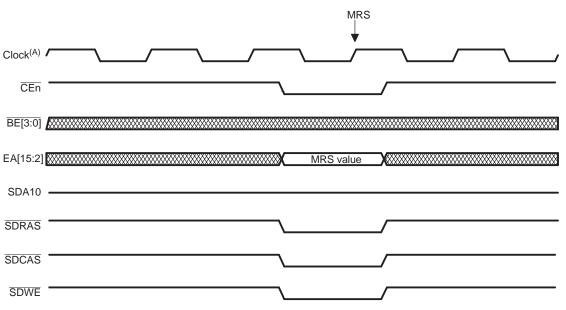

| 3-9  | SDRAM Mode Register Set: MRS Command Timing Diagram                                 | 79 |

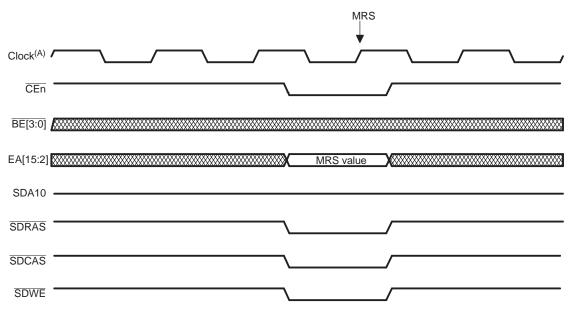

| 3-10 | SDRAM Three-Word Read Timing Diagram                                                | 81 |

| 3-11 | SDRAM Three-Word Write Timing Diagram                                               |    |

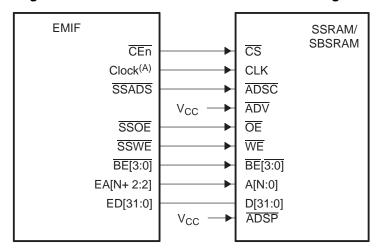

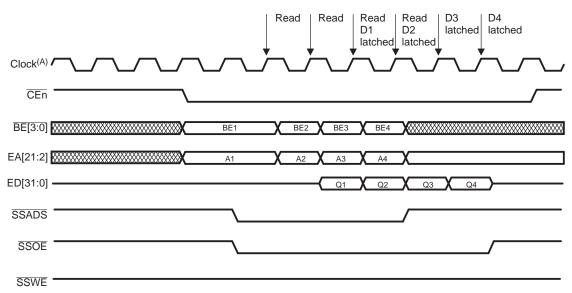

| 3-12 | EMIF to SBSRAM Interface Block Diagram                                              |    |

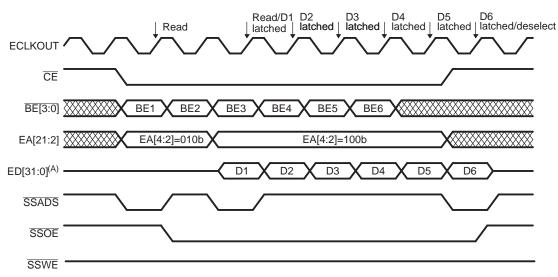

| 3-13 | SBSRAM Six-Word Read Timing Diagram                                                 |    |

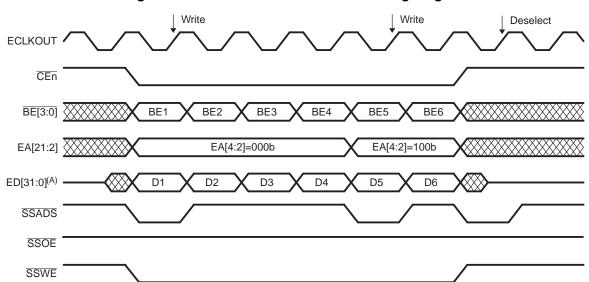

| 3-14 | SBSRAM Six-Word Write Timing Diagram                                                |    |

| 3-15 | EMIF Global Control Register (GBLCTL)                                               |    |

| 3-16 | EMIF CE Space Control Register (CECTL)                                              |    |

| 3-17 | EMIF SDRAM Control Register (SDCTL)                                                 |    |

| 3-18 | EMIF SDRAM Timing Register (SDTIM)                                                  |    |

| 3-19 | EMIF SDRAM Extension Register (SDEXT)                                               | 92 |

## www.ti.com

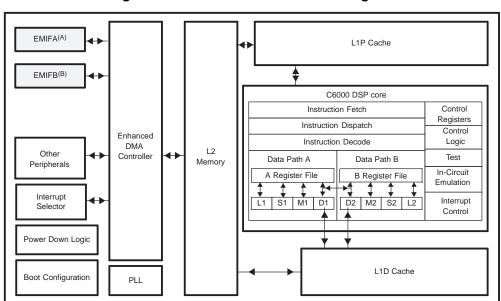

| 4-1  | TMS320C64x DSP Block Diagram                                                                  | . 94 |

|------|-----------------------------------------------------------------------------------------------|------|

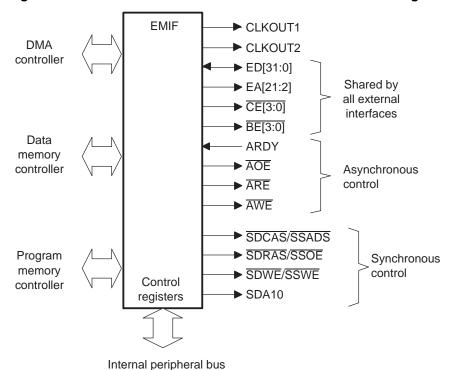

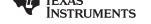

| 4-2  | TMS320C64x EMIFA and EMIFB Interface Signals                                                  | . 95 |

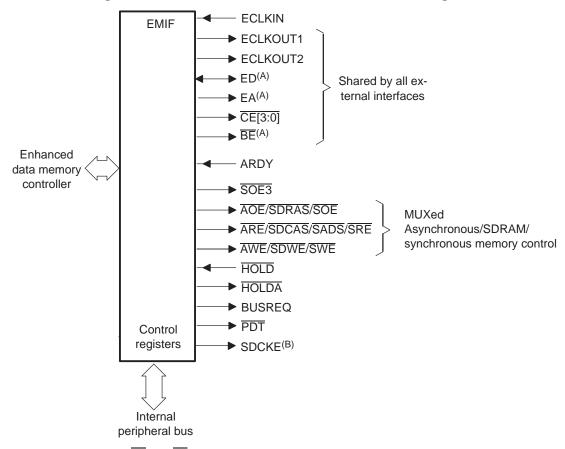

| 4-3  | Byte Alignment by Endianness - 64-bit                                                         | . 98 |

| 4-4  | Byte Alignment by Endianess - 32-bit                                                          | . 98 |

| 4-5  | Byte Alignment by Endianess - 16-bit                                                          | . 98 |

| 4-6  | EMIFA to 64M-Bit SDRAM Interface Block Diagram                                                | . 99 |

| 4-7  | Logical Address-to-Page Register Mapping for EMIFA                                            | 101  |

| 4-8  | Logical Address-to-Page Register Mapping for EMIFB                                            | 102  |

| 4-9  | Mode Register Value <sup>(A)</sup>                                                            | 105  |

| 4-10 | SDRAM Mode Register Set: MRS Command Timing Diagram                                           | 105  |

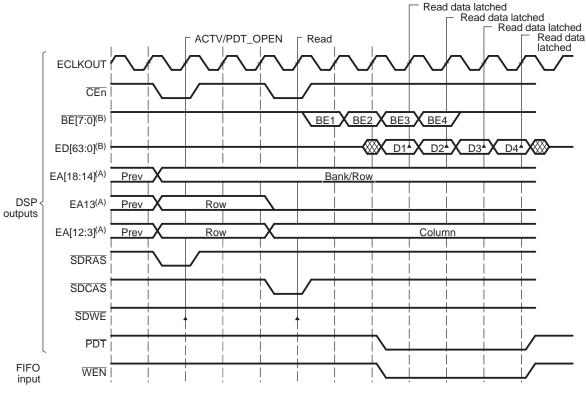

| 4-11 | SDRAM Read Timing Diagram                                                                     | 107  |

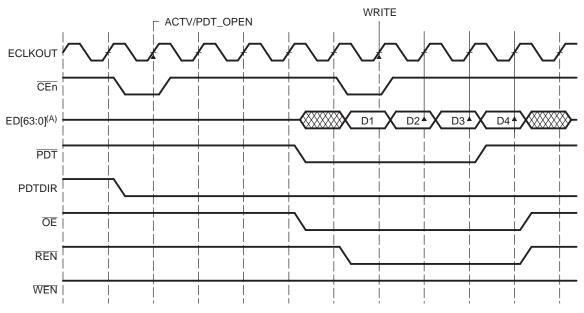

| 4-12 | SDRAM Write Timing Diagram                                                                    | 108  |

| 4-13 | EMIF to SBSRAM Interface Block Diagram                                                        | 110  |

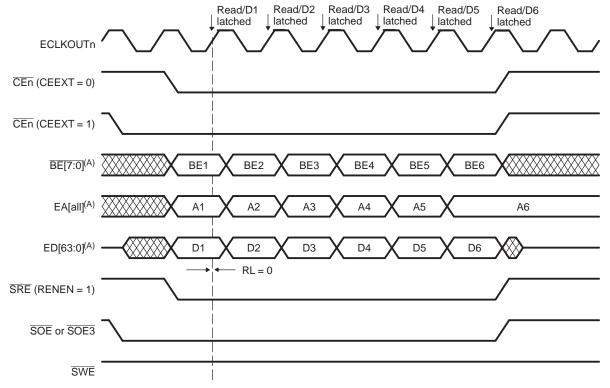

| 4-14 | SBSRAM Six-Element Read Timing Diagram                                                        | 111  |

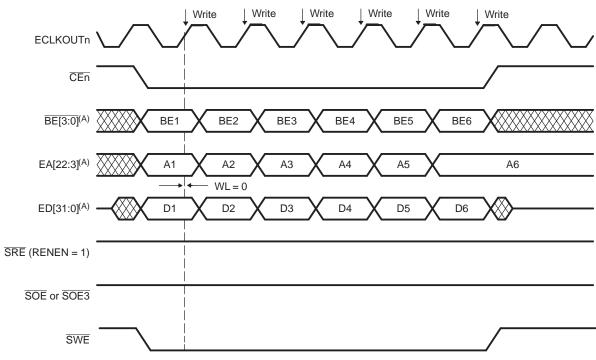

| 4-15 | SBSRAM Six-Element Write Timing Diagram                                                       | 112  |

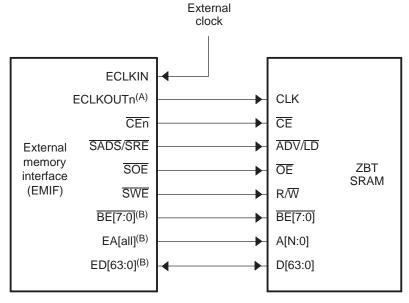

| 4-16 | EMIF to Zero Bus Turnaround (ZBT) SRAM Interface Block Diagram                                | 113  |

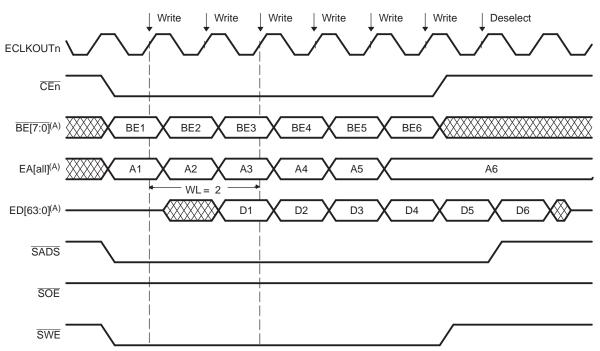

| 4-17 | Zero Bus Turnaround (ZBT) SRAM Six-Element Write Timing Diagram                               | 114  |

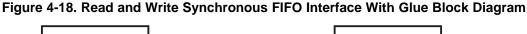

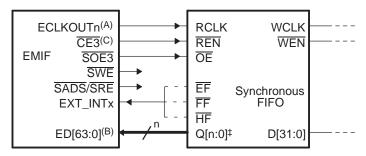

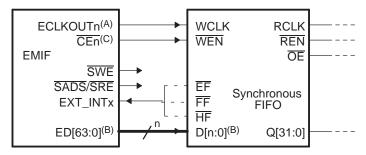

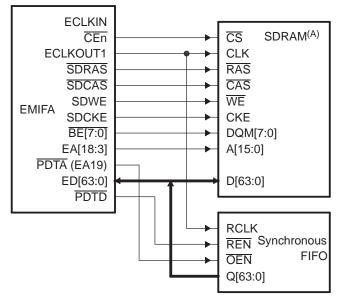

| 4-18 | Read and Write Synchronous FIFO Interface With Glue Block Diagram                             | 115  |

| 4-19 | Glueless Synchronous FIFO Read Interface in CE3 Space Block Diagram                           | 116  |

| 4-20 | Glueless Synchronous FIFO Write Interface Block Diagram                                       | 116  |

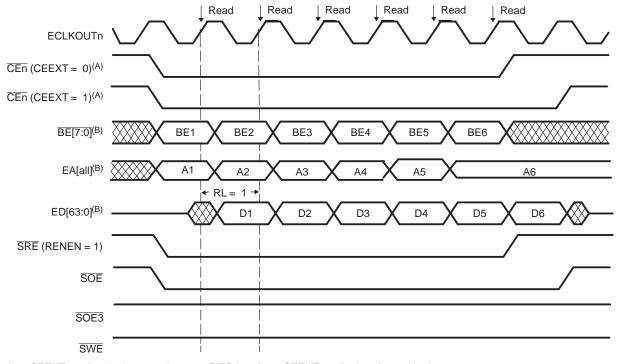

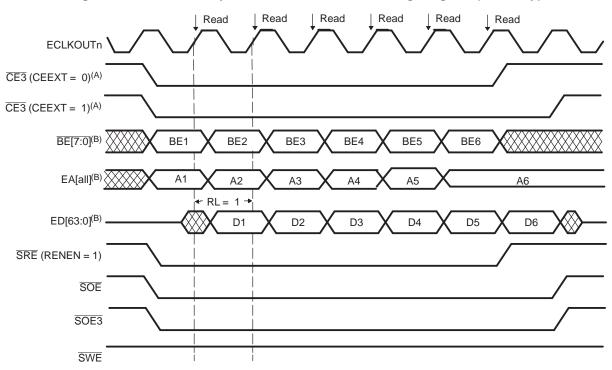

| 4-21 | Standard Synchronous FIFO Read Timing Diagram (CE0, CE1, or CE2)                              | 117  |

| 4-22 | Standard Synchronous FIFO Read Timing Diagram (CE3 only)                                      | 118  |

| 4-23 | Standard Synchronous FIFO Write Timing Diagram                                                | 119  |

| 4-24 | First Word Fall Through (FWFT) Synchronous FIFO Read Timing Diagram                           | 120  |

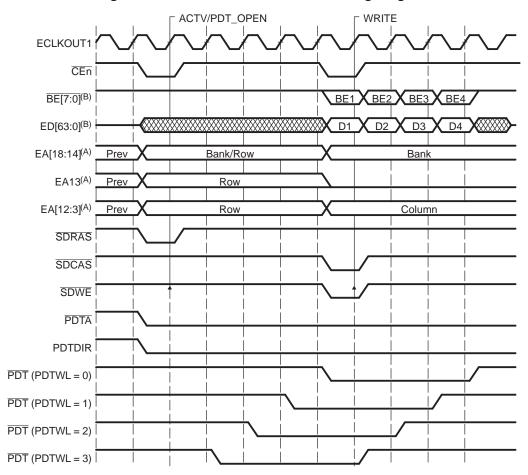

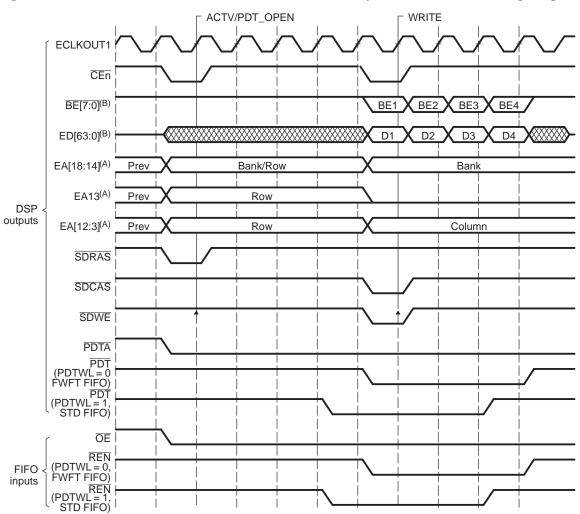

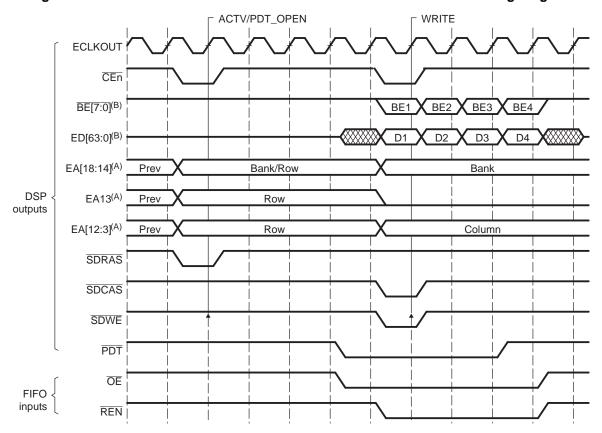

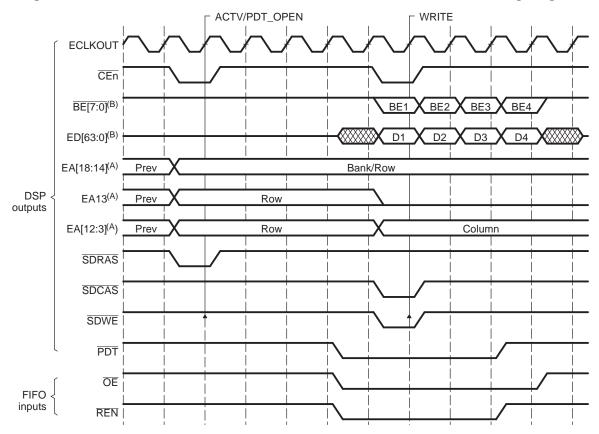

| 4-25 | PDT Write Transaction Timing Diagram                                                          | 123  |

| 4-26 | Case A: Glueless PDT Write Interface From Synchronous FIFO Block Diagram                      | 124  |

| 4-27 | Case A: Glueless PDT Write Transfer From Synchronous FIFO Timing Diagram                      | 125  |

| 4-28 | Case B: PDT Write Interface From FWFT FIFO With Glue Block Diagram                            | 126  |

| 4-29 | Case B: PDT Write Transfer From FWFT FIFO With Glue Timing Diagram                            | 126  |

| 4-30 | Case C: PDT Write Interface From Standard FIFO With Glue Block Diagram                        | 127  |

| 4-31 | Case C: PDT Write Transfer From Standard FIFO With Glue Timing Diagram                        | 127  |

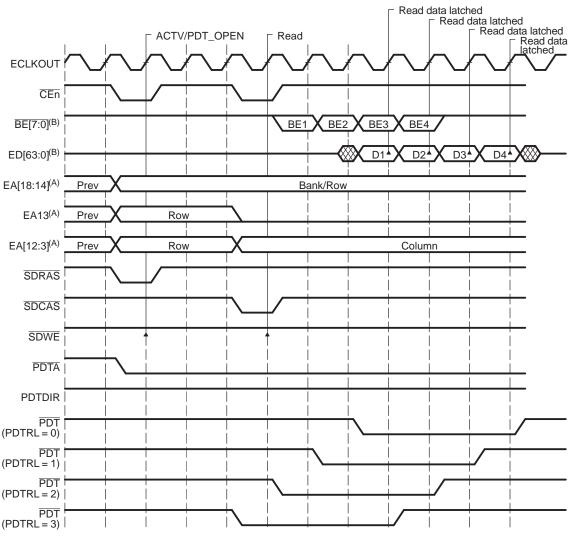

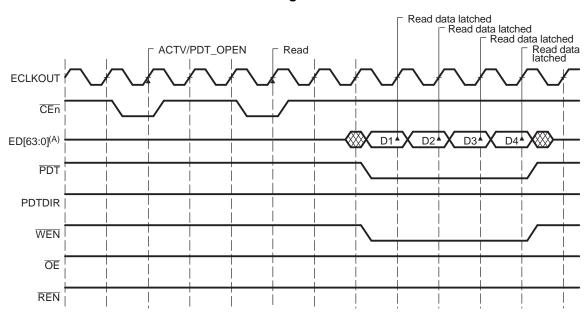

| 4-32 | PDT Read Transaction (CAS Latency is 3) Timing Diagram                                        |      |

| 4-33 | Case D: Glueless PDT Read Interface to Synchronous FIFO Block Diagram                         | 130  |

| 4-34 | Case D: Glueless PDT Read Transfer to Synchronous FIFO Timing Diagram                         | 130  |

| 4-35 | Case E: PDT Read and Write Interface With Multiple FIFOs Block Diagram                        | 131  |

| 4-36 | Case E: PDT Write Transfer with Read and Write FIFOs in the System (FWFT FIFO) Timing Diagram | 132  |

| 4-37 | Case E: PDT Read Transfer with Read and Write FIFOs in the System (FWFT FIFO) Timing Diagram  | 132  |

| 4-38 | EMIF Global Control Register (GBLCTL)                                                         | 135  |

| 4-39 | EMIF CE Space Control Register (CECTL)                                                        | 137  |

| 4-40 | EMIF CE Space Secondary Control Register (CESEC)                                              |      |

| 4-41 | EMIF SDRAM Control Register (SDCTL)                                                           | 140  |

| 4-42 | EMIF SDRAM Timing Register (SDTIM)                                                            | 142  |

| 4-43 | EMIF SDRAM Extension Register (SDEXT)                                                         | 143  |

| 4-44 | EMIF Peripheral Device Transfer Control Register (PDTCTL)                                     | 144  |

# **List of Tables**

| 1-1  | Differences Between the C62x/C67x and C64x EMIF                    | . 14 |

|------|--------------------------------------------------------------------|------|

| 1-2  | TMS320C6000 EMIF SDRAM Commands                                    | . 15 |

| 1-3  | Truth Table for SDRAM Commands                                     | . 16 |

| 1-4  | TMS320C6000 SDRAM Signal Descriptions                              | . 17 |

| 1-5  | TMS320C6000 SDRAM Interface Summary                                | . 18 |

| 1-6  | TMS320C6000 SBSRAM Operating Speeds                                | . 24 |

| 1-7  | TMS320C6000 SBSRAM Signal Descriptions                             | . 25 |

| 1-8  | TMS320C6000 SBSRAM Interface Summary                               | . 25 |

| 1-9  | Asynchronous Interface Signal Descriptions                         | . 26 |

| 1-10 | TMS320C6000 ASRAM Interface Summary                                | . 28 |

| 1-11 | EMIF Output Clock (ECLKOUTn) Operation                             | . 38 |

| 2-1  | TMS320C620x/C670x EMIF Interface Signal Descriptions               | . 45 |

| 2-2  | Addressable Memory Ranges                                          |      |

| 2-3  | TMS320C620x/C670x DSP Compatible SDRAM                             |      |

| 2-4  | Example C620x/C670x SDRAM Interface with Unused SDRAM Address Pins | . 48 |

| 2-5  | Byte Address-to-EA Mapping for SDRAM RAS and CAS                   |      |

| 2-6  | Implied SDRAM Configuration by MRS Command                         | . 52 |

| 2-7  | SDRAM Timing Parameters                                            |      |

| 2-8  | Byte Address to EA Mapping for Asynchronous Memory Widths          | . 58 |

| 2-9  | EMIF Prioritization of Memory Requests                             | . 59 |

| 2-10 | EMIF Registers for C620x/C670x DSP                                 |      |

| 2-11 | EMIF Global Control Register (GBLCTL) Field Descriptions           |      |

| 2-12 | EMIF CE Space Control Register (CECTL) Field Descriptions          |      |

| 2-13 | EMIF SDRAM Control Register (SDCTL) Field Descriptions             |      |

| 2-14 | EMIF SDRAM Timing Register (SDTIM) Field Descriptions              |      |

| 3-1  | TMS320C621x/C671x EMIF Interface Signal Descriptions               |      |

| 3-2  | Addressable Memory Ranges                                          |      |

| 3-3  | TMS320C621x/C671x DSP Compatible SDRAM                             |      |

| 3-4  | Byte Address-to-EA Mapping for 8-, 16-, and 32-Bit Interface       |      |

| 3-5  | Implied SDRAM Configuration by MRS Command                         |      |

| 3-6  | SDRAM Timing Parameters                                            |      |

| 3-7  | Recommended Values for Command-to-Command Parameters               |      |

| 3-8  | SBSRAM in Linear Burst Mode                                        |      |

| 3-9  | EMIF Prioritization of Memory Requests                             |      |

| 3-10 | EMIF Registers for C621x/C671x DSP                                 |      |

| 3-11 | EMIF Global Control Register (GBLCTL) Field Descriptions           |      |

| 3-12 | EMIF CE Space Control Register (CECTL) Field Descriptions          |      |

| 3-13 | EMIF SDRAM Control Register (SDCTL) Field Descriptions             |      |

| 3-14 | EMIF SDRAM Timing Register (SDTIM) Field Descriptions              |      |

| 3-15 | EMIF SDRAM Extension Register (SDEXT) Field Descriptions           |      |

| 4-1  | TMS320C64x EMIFA Bus Widths                                        |      |

| 4-2  | TMS320C64x EMIF Interface Signal Descriptions                      |      |

| 4-3  | Addressable Memory Ranges                                          |      |

| 4-4  | TMS320C64x DSP Compatible SDRAM                                    |      |

| 4-5  | Byte Address-to-EA Mapping for 8-, 16-, 32-, 64-Bit Interface      |      |

| 4-6  | Implied SDRAM Configuration by MRS Command                         |      |

| 4-7  | SDRAM Timing Parameters                                            |      |

| 4-8  | Recommended Values for Command-to-Command Parameters               |      |

| 4-9  | Programmable Synchronous Pins                                      | 109  |

### www.ti.com

| 4-10 | Peripheral Device Transfer (PDT) Signal Description                          | 121 |

|------|------------------------------------------------------------------------------|-----|

| 4-11 | Supported Set Ups for PDT Write Transfers                                    | 124 |

| 4-12 | Limitations on the Number of Additional Peripherals for a PDT Transfer       | 133 |

| 4-13 | DMA Configuration for a PDT Transfer                                         | 133 |

| 4-14 | EMIF Prioritization of Memory Requests                                       | 134 |

| 4-15 | EMIF Registers for C64x DSP                                                  | 134 |

| 4-16 | EMIF Global Control Register (GBLCTL) Field Descriptions                     | 135 |

| 4-17 | EMIF CE Space Control Register (CECTL) Field Descriptions                    | 137 |

| 4-18 | EMIF CE Space Secondary Control Register (CESEC) Field Descriptions          | 139 |

| 4-19 | EMIF SDRAM Control Register (SDCTL) Field Descriptions                       | 140 |

| 4-20 | EMIF SDRAM Timing Register (SDTIM) Field Descriptions                        | 142 |

| 4-21 | EMIF SDRAM Extension Register (SDEXT) Field Descriptions                     | 143 |

| 4-22 | EMIF Peripheral Device Transfer Control Register (PDTCTL) Field Descriptions | 144 |

| Δ-1  | Document Revision History                                                    | 145 |

# Read This First

### **About This Manual**

This document describes the operation of the external memory interface (EMIF) in the digital signal processors (DSPs) of the TMS320C6000™ DSP family. For operation and registers unique in the TMS320C620x/C670x EMIF, see Chapter 2. For operation and registers unique in the TMS320C621x/C671x EMIF, see Chapter 3. For operation and registers unique in the TMS320C64x™ EMIF, see Chapter 4.

### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

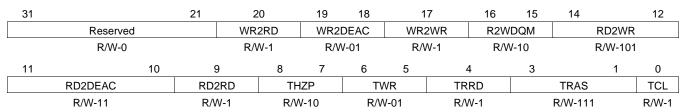

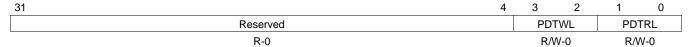

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

### **Related Documentation From Texas Instruments**

The following documents describe the C6000<sup>™</sup> devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

The current documentation that describes the C6000 devices, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: www.ti.com/c6000.

- SPRU189 TMS320C6000 DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C6000 digital signal processors (DSPs).

- SPRU190 TMS320C6000 DSP Peripherals Overview Reference Guide. Provides an overview and briefly describes the peripherals available on the TMS320C6000 family of digital signal processors (DSPs).

- SPRU197 TMS320C6000 Technical Brief. Provides an introduction to the TMS320C62x and TMS320C67x digital signal processors (DSPs) of the TMS320C6000 DSP family. Describes the CPU architecture, peripherals, development tools and third-party support for the C62x and C67x DSPs.

- <u>SPRU395</u> *TMS320C64x Technical Overview.* Provides an introduction to the TMS320C64x digital signal processors (DSPs) of the TMS320C6000 DSP family.

## **Trademarks**

TMS320C6000, TMS320C64x, C6000, TMS320C620x/C670x, TMS320C621x/C671x, C64x are trademarks of Texas Instruments.

# **Overview**

This chapter provides an overview and describes the common operation of the external memory interface (EMIF) in the digital signal processors (DSPs) of the TMS320C6000<sup>TM</sup> DSP family. For operation and registers unique in the TMS320C620x/C670x<sup>TM</sup> EMIF, see Chapter 2. For operation and registers unique in the TMS320C621x/C671x<sup>TM</sup> EMIF, see Chapter 3. For operation and registers unique in the TMS320C64x<sup>TM</sup> EMIF, see Chapter 4.

| Topic |                                                   | Page      |

|-------|---------------------------------------------------|-----------|

| 1.1   | Overview                                          | 14        |

| 1.2   | Command-to-Command Turnaround Time                | 15        |

| 1.3   | SDRAM Interface                                   | 15        |

| 1.4   | SBSRAM Interface                                  | 24        |

| 1.5   | Asynchronous Interface                            | 26        |

| 1.6   | Resetting the EMIF                                | <b>35</b> |

| 1.7   | Hold Interface                                    | <b>36</b> |

| 1.8   | Boundary Conditions When Accessing EMIF Registers | <b>37</b> |

| 1.9   | Clock Output Enabling                             | 38        |

| 1.10  | Emulation Halt Operation                          | <b>39</b> |

| 1.11  | Power Down                                        | 39        |

Overview www.ti.com

### 1.1 Overview

The external memory interfaces (EMIFs) of all C6000 devices support a glueless interface to a variety of external devices, including:

- Pipelined synchronous-burst SRAM (SBSRAM)

- Synchronous DRAM (SDRAM)

- Asynchronous devices, including SRAM, ROM, and FIFOs

- An external shared-memory device

Table 1-1 summarizes the differences between the C6000 EMIFs.

Table 1-1. Differences Between the C62x/C67x and C64x EMIF

|                                                |                          | C62x/C67x EMIF                               |                                  |                                                                | C64x EMIF <sup>(1)</sup>  |                           |  |  |

|------------------------------------------------|--------------------------|----------------------------------------------|----------------------------------|----------------------------------------------------------------|---------------------------|---------------------------|--|--|

|                                                |                          | Other C620x/C670x C621x/C671x <sup>(2)</sup> |                                  | EM                                                             | EMIFB<br>C6416/15/14      |                           |  |  |

| Feature                                        | C6201/C6701              |                                              |                                  | C6416/15/14/12, C6411,<br>DM642/643 DM640/641                  |                           |                           |  |  |

| Bus width                                      | 32-bit                   | 32-bit                                       | 32-bit <sup>(2)</sup>            | 64-bit                                                         | 32-bit                    | 16-bit                    |  |  |

| Number of memory spaces                        | 4                        | 4                                            | 4                                | 4                                                              | 4                         | 4                         |  |  |

| Addressable space (Mbytes)                     | 52                       | 52                                           | 512 <sup>(2)</sup>               | 1024                                                           | 512                       | 256                       |  |  |

| cĺocking and/or 1/2ıCPU ECLKIN ECLKIN, ECLKIN, |                          |                                              | 1/41CPU clock<br>or 1/61CPU      | Independent<br>ECLKIN,<br>1/41CPU clock<br>or 1/61CPU<br>clock |                           |                           |  |  |

| Width support                                  | 32 bit;<br>8-/16-bit ROM | 32 bit;<br>8-/16-bit ROM                     | 8-/16-bit, 32-bit <sup>(2)</sup> | 8-, 16-, 32-, or<br>64-bit                                     | 8-, 16-, or 32-bit        | 8-bit or 16-bit           |  |  |

| Supported<br>memory type<br>at CE1             | Asynchronous memory      | Asynchronous memory                          | All types                        | All types                                                      | All types                 | All types                 |  |  |

| Control signals                                | Separate                 | Muxed<br>synchronous<br>signals              | Muxed all control signals        | Muxed all control signals                                      | Muxed all control signals | Muxed all control signals |  |  |

| Synchronous<br>memory in<br>system             | Both SDRAM and<br>SBSRAM | Either SDRAM or<br>SBSRAM                    | Both SDRAM and<br>SBSRAM         | All synchronous                                                | All synchronous           | All synchronous           |  |  |

| Additional registers                           | _                        | _                                            | SDEXT                            | SDEXT<br>CESEC                                                 | SDEXT<br>CESEC            | SDEXT<br>CESEC            |  |  |

| PDT support                                    | No                       | No                                           | No                               | Yes                                                            | Yes                       | Yes                       |  |  |

| ROM/Flash                                      | $\sqrt{}$                | $\sqrt{}$                                    | $\sqrt{}$                        | $\checkmark$                                                   | $\sqrt{}$                 | $\sqrt{}$                 |  |  |

| Asynchronous<br>memory I/O                     | $\sqrt{}$                | $\sqrt{}$                                    | $\sqrt{}$                        | $\sqrt{}$                                                      | $\sqrt{}$                 | $\sqrt{}$                 |  |  |

| Pipeline<br>SBSRAM                             | $\sqrt{}$                | $\sqrt{}$                                    | $\sqrt{}$                        | $\sqrt{}$                                                      | $\sqrt{}$                 | $\checkmark$              |  |  |

| Flow thru<br>SBSRAM                            |                          |                                              |                                  | $\sqrt{}$                                                      | $\sqrt{}$                 | $\sqrt{}$                 |  |  |

| ZBT SRAM                                       |                          |                                              |                                  | $\checkmark$                                                   | $\checkmark$              | √                         |  |  |

| Standard<br>Synchronous<br>FIFO                |                          |                                              |                                  | $\sqrt{}$                                                      | $\sqrt{}$                 | √                         |  |  |

| FWFT FIFO                                      |                          |                                              |                                  | $\sqrt{}$                                                      | $\sqrt{}$                 | $\checkmark$              |  |  |

<sup>(1)</sup> On the C64x DSP, the EMIFA bus width is device specific, either 64-bit or 32-bit wide. EMIFB has a 16-bit bus width.

On the C6712/C6712C DSP, the EMIF is only 16-bits wide. Addressable space is 256M bytes. It supports memory widths of 8 bits and 16 bits.

## 1.2 Command-to-Command Turnaround Time

The C6000 EMIF has a one cycle command-to-command turnaround time. At least 1 data dead cycle is always included between commands so that read data and write data are never driven in the same cycle.

#### 1.3 SDRAM Interface

The C6000 EMIF supports the SDRAM commands shown in Table 1-2. Table 1-3 shows the signal truth table for the SDRAM commands. The 16-bit EMIF, 32-bit EMIF, and 64-bit EMIF table entries refer to the total bus width of the EMIF and not the size of the transfer. Table 1-4 summarizes the pin connection and related signals specific to SDRAM operation. Table 1-5 summarizes the similarities and differences on the C6000 SDRAM interface.

Table 1-2. TMS320C6000 EMIF SDRAM Commands

| Command     | Function                                                          |

|-------------|-------------------------------------------------------------------|

| ACTV        | Activates the selected bank and selects the row                   |

| DCAB        | Deactivates (also known as PRECHARGE) all banks                   |

| DEAC(1)     | Deactivates a single bank                                         |

| MRS         | Mode register set, configures SDRAM mode register                 |

| READ        | Inputs the starting column address and begins the read operation  |

| REFR        | Autorefresh cycle with internal address                           |

| SLFREFR (2) | Self-refresh mode                                                 |

| WRT         | Inputs the starting column address and begins the write operation |

<sup>(1)</sup> TMS320C621x/C671x/C64x DSP only.

<sup>(2)</sup> TMS320C64x DSP only.

SDRAM Interface www.ti.com

|                                |                      | Ta | able 1-3. T | ruth Tabl | e for SDF | RAM Comma                           | nds             |                     |                         |

|--------------------------------|----------------------|----|-------------|-----------|-----------|-------------------------------------|-----------------|---------------------|-------------------------|

| SDRAM:                         | CKE                  | CS | RAS         | CAS       | W         | A[19:16]                            | A[15:11]        | A10                 | A[9:0]                  |

| 16-bit<br>EMIF: <sup>(1)</sup> | SDCKE                | CE | SDRAS       | SDCAS     | SDWE      | EA[20:17] <sup>(2)</sup>            | EA[16:12]       | EA11                | EA[10:1]                |

| 32-bit<br>EMIF: <sup>(1)</sup> | SDCKE <sup>(3)</sup> | CE | SDRAS       | SDCAS     | SDWE      | EA[21:18] <sup>(4)</sup>            | EA[17:13]       | EA12 <sup>(5)</sup> | EA[11:2] <sup>(6)</sup> |

| 64-bit<br>EMIF: <sup>(1)</sup> | SDCKE                | CE | SDRAS       | SDCAS     | SDWE      | EA[22:19] <sup>(2)</sup>            | EA[18:14]       | EA13                | EA[12:3] <sup>(7)</sup> |

| ACTV                           | Н                    | L  | L           | Н         | Н         | 0001b<br>or<br>0000b <sup>(4)</sup> | Bank/Row        | Row                 | Row                     |

| READ                           | Н                    | L  | Н           | L         | Н         | X                                   | Bank/<br>Column | L                   | Column                  |

| WRT                            | Н                    | L  | Н           | L         | L         | X                                   | Bank/<br>Column | L                   | Column                  |

| MRS                            | Н                    | L  | L           | L         | L         | L                                   | L/Mode          | Mode                | Mode                    |

| DCAB                           | Н                    | L  | L           | Н         | L         | Х                                   | Χ               | Н                   | Χ                       |

| DEAC                           | Н                    | L  | L           | Н         | L         | Х                                   | Bank/X          | L                   | Χ                       |

| REFR                           | Н                    | L  | L           | L         | Н         | X                                   | Χ               | Х                   | Χ                       |

| SLFREFR                        | L                    | L  | L           | L         | Н         | X                                   | X               | Χ                   | X                       |

<sup>(1) 16-</sup>bit EMIF includes C64x EMIFB; 32-bit EMIF includes all C62x/C67x EMIF, both 32-bit and 16-bit interfaces; 64-bit EMIF includes C64x EMIFA, both 64-bit and 32-bit interfaces.

<sup>(2)</sup> For C64x DSP, upper address bits are used during ACTV to indicate non-PDT (0001b) vs. PDT (0000b) access. During all other accesses, address bits indicated with X hold previous value.

<sup>(3)</sup> SDCKE does not exist on C62x/C67x DSP.

<sup>(4)</sup> For C62x/C67x DSP, upper address bits are reserved for future use. Undefined.

<sup>(5)</sup> SDA10 is used on C620x/C670x DSP. EA12 is used on C621x/C671x DSP.

<sup>(6)</sup> EMIF address numbering for the C6712/C6712C 16-bit EMIF begins with EA2 to maintain signal name compatibility with the C62x/C67x 32-bit EMIF.

<sup>(7)</sup> EMIF address numbering for the C64x 32-bit EMIFA begins with EA3 to maintain signal name compatibility with the C64x 64-bit EMIFA.

SDRAM Interface www.ti.com

# Table 1-4. TMS320C6000 SDRAM Signal Descriptions

| EMIF Signal                              | SDRAM<br>Signal | SDRAM Function                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BEx                                      | DQMx            | Data/output mask. DQM is an input/output buffer control signal. When high, it disables writes and places outputs in the high impedance state during reads. DQM has a 2-CLK-cycle latency on reads and a 0-CLK-cycle latency on writes. DQM pins serve as byte strobes and are connected to BE outputs.                                                                                                     |

| CE3, CE2,<br>CE1 <sup>(1)</sup> , or CE0 | <del>CS</del>   | Chip select and command enable. $\overline{\text{CS}}$ must be active (low) for a command to be clocked into the SDRAM. $\overline{\text{CE1}}$ does not support SDRAM on C620x/C670x DSP.                                                                                                                                                                                                                 |

| CLKOUT2                                  | CLK             | SDRAM clock input. Runs at 1/2 the CPU clock rate. Used for synchronous memory interface on the C6202(B)/C6203(B)/C6204/C6205 DSP.                                                                                                                                                                                                                                                                         |

| ECLKOUT                                  | CLK             | SDRAM clock input. Used for synchronous memory interface on the C621x/C671x/C64x DSP. For C6713 DSP, runs at either ECLKIN or SYSCLK3 (programmable divide-down clock with PLL output as reference clock), configurable using EKSRC bit in DEVCFG. For C621x/C671x DSP, runs at ECLKIN rate. For C64x DSP, ECLKOUT1 is used. ECLKOUT1 runs at EMIF input clock rate (ECLKIN, CPU/4 clock, or CPU/6 clock). |

| SDA10 <sup>(2)</sup>                     | A10             | Address line A10/autoprecharge disable. Serves as a row address bit during ACTV commands and also disables the autoprecharging function of SDRAM. (C620x/C670x DSP only)                                                                                                                                                                                                                                   |

| SDCAS                                    | CAS             | Column address strobe and command Input. Latched by the rising edge of CLK to determine current operation. Valid only if $\overline{\text{CS}}$ is active (low) during that clock edge.                                                                                                                                                                                                                    |

| SDCKE <sup>(3)</sup>                     | CKE             | CKE clock enable. For C64x DSP, SDCKE is connected to CKE to minimize SDRAM power consumption when self-refresh mode is enabled. For C62x/C67x SDRAM interface, CKE is tied high (on the SDRAM device) since the Self Refresh command is not supported.                                                                                                                                                    |

| SDCLK                                    | CLK             | SDRAM clock input. Runs at 1/2 the CPU clock rate. Used for SDRAM interface on C6201/C6701 DSP.                                                                                                                                                                                                                                                                                                            |

| SDRAS                                    | RAS             | Row address strobe and command input. Latched by the rising edge of CLK to determine current operation. Valid only if $\overline{\text{CS}}$ is active (low) during that clock edge.                                                                                                                                                                                                                       |

| SDWE                                     | WE              | Write strobe and command input. Latched by the rising edge of CLK to determine current operation. Valid only if $\overline{\text{CS}}$ is active (low) during that clock edge.                                                                                                                                                                                                                             |

For C620x/C670x DSP, CE1 does not support SDRAM.

SDA10 is used on C620x/C670x DSP. EA12 is used on C621x/C671x DSP. EA13 is used on C64x EMIFA; EA11 is used on C64x EMIFA. (2)

<sup>(3)</sup> SDCKE exists on C64x DSP only.

SDRAM Interface www.ti.com

Table 1-5. TMS320C6000 SDRAM Interface Summary

| C62x/C67x EMIF                              |                                                                             |                                                                             |                                                      | C64x EMIF                                                          |                                                                    |                                                                    |  |

|---------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--|

|                                             |                                                                             |                                                                             |                                                      | EMIFA                                                              |                                                                    | EMIFB                                                              |  |

| Feature                                     | C6201/C6701                                                                 | Other<br>C620x/C670x <sup>(1)</sup>                                         | C621x/C671x <sup>(2)</sup>                           | C6416/15/14/12,<br>DM642                                           | C6411,<br>DM640/641                                                | C6416/15/14                                                        |  |

| Interface width                             | 32-bit                                                                      | 32-bit                                                                      | 32-, 16-, 8-bit                                      | 64-, 32-, 16-,<br>8-bit                                            | 32-, 16-, 8-bit                                                    | 16-, 8-bit                                                         |  |

| SDRAM clock                                 | SDCLK                                                                       | CLKOUT2                                                                     | ECLKOUT                                              | ECLKOUT1                                                           | ECLKOUT1                                                           | ECLKOUT1                                                           |  |

| Registers for<br>SDRAM timing<br>parameters | SDCTL,<br>SDTIM                                                             | SDCTL,<br>SDTIM                                                             | SDCTL,<br>SDTIM,<br>SDEXT                            | SDCTL,<br>SDTIM,<br>SDEXT                                          | SDCTL,<br>SDTIM,<br>SDEXT                                          | SDCTL,<br>SDTIM,<br>SDEXT                                          |  |

| SDRAM control signals                       | Dedicated<br>SDRAM<br>control signals                                       | MUXed with<br>SBSRAM<br>control signals                                     | MUXed with<br>SBSRAM and<br>Async control<br>signals | MUXed with<br>Async and<br>Programmable<br>Sync control<br>signals | MUXed with<br>Async and<br>Programmable<br>Sync control<br>signals | MUXed with<br>Async and<br>Programmable<br>Sync control<br>signals |  |

| Number of open pages                        | Single open page per CE space                                               | Single open page per CE space                                               | 4 open pages in any CE space                         | 4 open pages in any CE space                                       | 4 open pages in any CE space                                       | 4 open pages in any CE space                                       |  |

| Programmable<br>SDRAM<br>configuration      | 8- or 9-column address bits                                                 | 8- or 9-column address bits                                                 | column, row, and bank size                           | column, row, and<br>bank size                                      | column, row,<br>and bank size                                      | column, row, and bank size                                         |  |

| Burst mode                                  | Not supported.<br>Performs bursts<br>by issuing<br>back-to-back<br>commands | Not supported.<br>Performs bursts<br>by issuing<br>back-to-back<br>commands | Supports SDRAM<br>burst mode with a<br>4-word burst  | Supports SDRAM<br>burst mode with a<br>4-word burst                | Supports<br>SDRAM burst<br>mode with a<br>4-word burst             | Supports<br>SDRAM burst<br>mode with a<br>4-word burst             |  |

| Background refresh                          | Yes                                                                         | Yes                                                                         | No                                                   | No                                                                 | No                                                                 | No                                                                 |  |

| Precharge pin                               | SDA10                                                                       | SDA10                                                                       | EA12                                                 | EA13                                                               | EA13                                                               | EA11                                                               |  |

| SDRAM<br>self-refresh<br>mode               | No                                                                          | No                                                                          | No                                                   | Yes                                                                | Yes                                                                | No                                                                 |  |

| Page replacement                            | Fixed                                                                       | Fixed                                                                       | Random                                               | LRU                                                                | LRU                                                                | LRU                                                                |  |

This column applies to all C620x/C670x devices, except C6201/C6701 DSP. C6712/C6712C DSP interfaces to 8-bit and 16-bit SDRAM only.

www.ti.com SDRAM Interface

### 1.3.1 SDRAM Initialization

After reset, none of the CE spaces are configured as SDRAM. The CPU should initialize all of the CE space control registers and the SDRAM extension register before performing SDRAM initialization by setting the INIT bit to 1. If SDRAM does not exist in the system, you should not write a 1 to the INIT bit.

The EMIF performs the following steps when INIT is set to 1:

- 1. Sends a DCAB command to all CE spaces configured as SDRAM.

- 2. Sends eight refresh commands.

- 3. Sends an MRS command to all CE spaces configured as SDRAM.

For the duration of SDRAM initialization, the  $\overline{\text{BE}}$  signals are inactive high. The SDRAM initialization is noninterruptible by other EMIF accesses.

SDRAM initialization status may be monitored using the INIT bit. The INIT bit returns to 0 automatically when initialization is complete.

# 1.3.2 Monitoring Page Boundaries

SDRAM is a paged memory type, thus the EMIF SDRAM controller monitors the active row of SDRAM so that row boundaries are not crossed during the course of an access. To accomplish this priority, the EMIF stores the address of the open row in internal page register(s), then performs compares against that address for subsequent accesses to any SDRAM CE space.

For all C6000 devices, ending the current access is not a condition that forces the active SDRAM row to be closed. The EMIF leaves the active row open until it becomes necessary to close it. This decreases the deactivate-reactivate overhead and allows the interface to capitalize fully on the address locality of memory accesses.

SDRAM Interface www.ti.com

### 1.3.3 SDRAM Refresh Mode

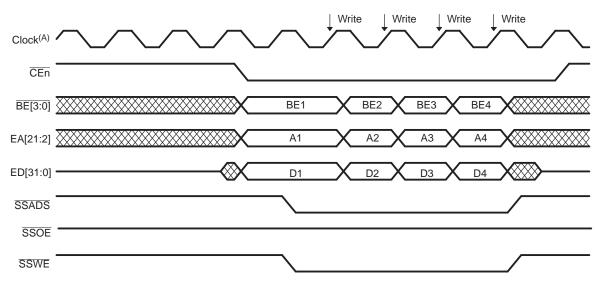

The RFEN bit in the SDRAM control register (SDCTL) selects the SDRAM refresh mode of the EMIF. When RFEN = 0, all EMIF refreshes are disabled, and you must ensure that refreshes are implemented in an external device. When RFEN = 1, the EMIF performs refreshes of SDRAM.

Refresh commands (REFR) enable all  $\overline{\text{CE}}$  signals for all CE spaces selected to use SDRAM (with the MTYPE field of the CE space control register). REFR is automatically preceded by a DCAB command, ensuring the deactivation of all CE spaces selected with SDRAM. Following the DCAB command, the EMIF begins performing trickle refreshes at a rate defined by the PERIOD value in SDTIM, provided no other SDRAM access is pending.

For all C6000 devices, the EMIF SDRAM interface performs CAS-before-RAS refresh cycles for SDRAM. Some SDRAM manufacturers call this autorefresh. Prior to an REFR command, a DCAB command is performed to all CE spaces specifying SDRAM to ensure the closure of all active banks. Page information is always invalid before and after a REFR command; thus, a refresh cycle always forces a page miss. A deactivate cycle is required prior to the refresh command. Figure 1-1 shows the timing diagram for an SDRAM refresh.

Figure 1-1. SDRAM Refresh Timing Diagram

- A Clock = SDCLK for C6201/C6701 DSP.

- = CLKOUT2 for all C620x/C670x DSP, except C6201/C6701 DSP.

- = ECLKOUT for C621x/C671x DSP.

- = ECLKOUT1 for C64x DSP.

www.ti.com SDRAM Interface

# 1.3.4 SDRAM Deactivation (DCAB and DEAC)

The SDRAM deactivation (DCAB) is performed after a hardware reset or when INIT = 1 in the SDRAM control register (SDCTL). The SDRAMs also require this cycle prior to a refresh (REFR) and mode set register (MRS) command. On the C6000 EMIF, a DCAB is issued when a page boundary is crossed. During the DCAB command, SDA10 is driven high to ensure the deactivation of all SDRAM banks. Figure 1-2 shows the timing diagram for SDRAM deactivation.

The C621x/C671x EMIF and C64x<sup>™</sup> EMIF also support the DEAC command, which closes a single page of SDRAM specified by the bank select signals. When a page boundary is crossed, the DEAC command is used to close the open page. The C621x/C671x EMIF and C64x EMIF still support the DCAB command to close all pages prior to REFR and MRS commands. Figure 1-3 shows the timing diagram for SDRAM deactivation.

Figure 1-2. TMS320C6000 SDRAM Deactivate All Banks (DCAB) Command Timing Diagram

- A Clock = SDCLK for C6201/C6701 DSP.

- = CLKOUT2 for all C620x/C670x DSP, except C6201/C6701 DSP.

- = ECLKOUT for C621x/C671x DSP.

- = ECLKOUT1 for C64x DSP.

- B SDA10 applies to C620x/C670x DSP only. On C621x/C671x DSP, EA12 is used. On C64x EMIFA, EA13 is used; on EMIFB, EA11 is used.

SDRAM Interface www.ti.com

Figure 1-3. TMS320C621x/C671x and TMS320C64x SDRAM Deactivate Single Bank (DEAC) Command Timing Diagram

A Clock = ECLKOUT for C621x/C671x DSP. = ECLKOUT1 for C64x DSP.

B For C64x EMIFA, EA13 is used; for EMIFB, EA11 is used.

www.ti.com SDRAM Interface

# 1.3.5 SDRAM Activation (ACTV)

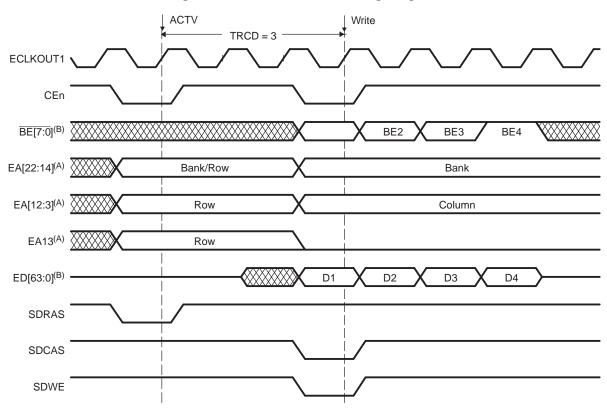

The C6000 EMIF automatically issues the activate (ACTV) command before a read or write to a new row of SDRAM. The ACTV command opens up a page of memory, allowing future accesses (reads or writes) with minimum latency. When the EMIF issues an ACTV command, a delay of  $t_{RCD}$  is incurred before a read or write command is issued. Figure 1-4 shows an example of an ACTV command before an SDRAM write. In this example,  $t_{RCD} = 3$  EMIF clock cycles. The ACTV command for SDRAM reads are identical. Reads or writes to the currently active row and bank of SDRAM can achieve much higher throughput than reads or writes to random areas, because every time a new page is accessed, the ACTV command must be issued.

Figure 1-4. TMS320C6000 SDRAM Activate (ACTV) Command Before an SDRAM Write Timing Diagram

- A Clock = SDCLK for C6201/C6701 DSP.

- = CLKOUT2 for all C620x/C670x DSP, except C6201/C6701 DSP.

- = ECLKOUT for C621x/C671x DSP.

- = ECLKOUT1 for C64x DSP.

- B SDA10 applies to C620x/C670x DSP only. On C621x/C671x DSP, EA12 is used. On C64x EMIFA, EA13 is used; on EMIFB, EA11 is used.

SBSRAM Interface www.ti.com

# 1.4 SBSRAM Interface

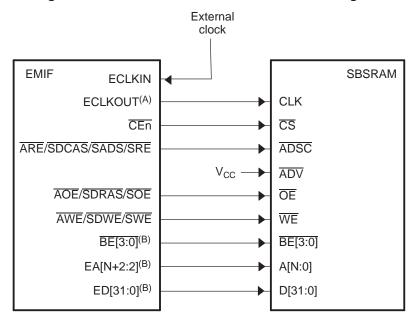

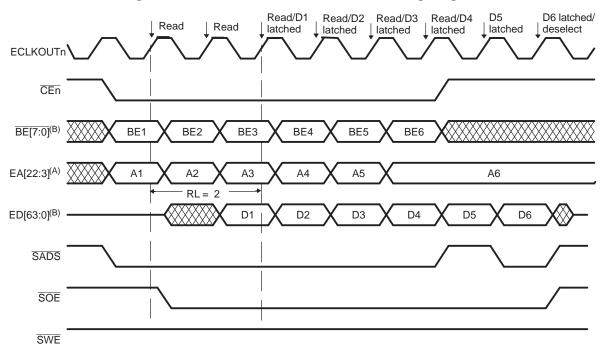

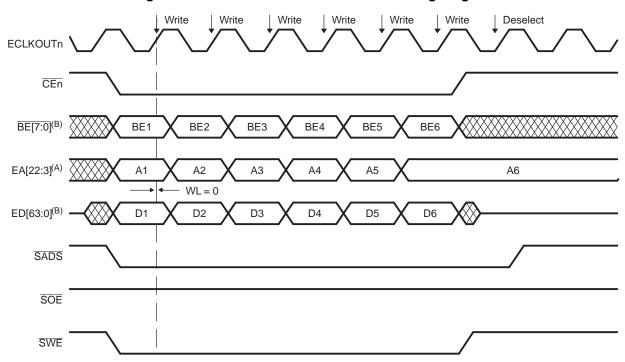

The C6000 EMIF interfaces directly to industry-standard synchronous burst SRAMs (SBSRAMs). This memory interface allows a high-speed memory interface without some of the limitations of SDRAM. Most notably, since SBSRAMs are SRAM devices, random accesses in the same direction can occur in a single cycle. Besides supporting the SBSRAM interface, the programmable synchronous interface on the C64x DSP supports additional synchronous device interfaces. See section Section 4.5 for details on the C64x DSP interface with the other synchronous devices. This section discusses the SBSRAM interface on all the C6000 devices.

SBSRAMs are latent by their architecture, since read data follows address and control information by two cycles. Consequently, the EMIF inserts cycles between read and write commands to ensure that no conflict exists on the ED[31:0] bus. The EMIF keeps this turnaround penalty to a minimum.

For the C6000 EMIF, the SBSRAM interface can run at either the CPU clock speed or at 1/2 of this rate, see Table 1-6. The selection is made based on the setting of the SSCRT bit in the EMIF global control register (GBLCTL).

Table 1-6. TMS320C6000 SBSRAM Operating Speeds

| Device         | Operates at                |

|----------------|----------------------------|

| C6201 DSP only | CPU clock or 1/2 CPU clock |

| C620x DSP      | 1/2 CPU clock              |

| C6701 DSP only | CPU clock or 1/2 CPU clock |

| C670x DSP      | 1/2 CPU clock              |

| C621x DSP      | ECLKOUT                    |

| C671x DSP      | ECLKOUT                    |

| C64x DSP       | ECLKOUT1 or ECLKOUT2       |

www.ti.com SBSRAM Interface

The four SBSRAM control pins are latched by the SBSRAM on the rising EMIF clock edge to determine the current operation. Table 1-7 lists these pins. These signals are valid only if the chip select line for the SBSRAM is low.

Table 1-8 provides an overview of similarities and differences on the C6000 SBSRAM interface.

Table 1-7. TMS320C6000 SBSRAM Signal Descriptions

| EMIF Signal <sup>(1)</sup> | SBSRAM Signal | SBSRAM Function |

|----------------------------|---------------|-----------------|

| SSADS                      | ADSC          | Address strobe  |

| SSOE                       | ŌĒ            | Output enable   |

| SSWE                       | WE            | Write enable    |

| SSCLK/CLKOUT2/ECLKOUT(2)   | CLK           | SBSRAM clock    |

<sup>(1)</sup> For C64x DSP, SBSRAM control signals are renamed as SADS/SRE, SOE, and SWE, respectively.

# Table 1-8. TMS320C6000 SBSRAM Interface Summary

|                        | C62x/C67x EMIF                                                                 |                                                                             |                                                      | C64x EMIF                                                                                                  |                                                                                                            |                                                                                                            |  |

|------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

|                        |                                                                                | 6201/C6701 Other C620x/C670x <sup>(1)</sup>                                 | C621x/C671x <sup>(2)</sup>                           | EMIFA                                                                                                      |                                                                                                            | EMIFB                                                                                                      |  |

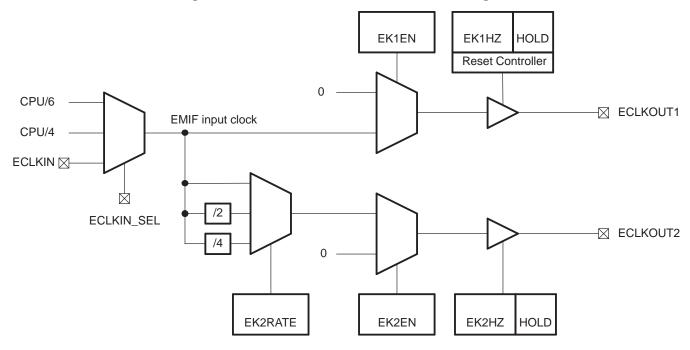

| Feature                | C6201/C6701                                                                    |                                                                             |                                                      | C6416/15/14/12,<br>DM642/643                                                                               | C6411, DM640/641                                                                                           | C6416/15/14                                                                                                |  |