SPRU652G November 2002 Revised February 2005

Copyright © 2005, Texas Instruments Incorporated

### **REVISION HISTORY**

This revision history highlights the technical changes made to SPRU652E to generate SPRU652F. It also highlights the technical changes made to SPRU652F to generate SPRU652G; these changes are marked by "**[Revision G]**" in the Revision History table below.

Scope: Added Advisory CPU\_118 and updated Section 1.1, etc. Added Advisory CPU\_119 [Revision G]

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                                                                            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6              | Table 1, Quick Reference Table:         –       added CPU_118, CPU May Halt After Returning From an Interrupt Service Routine When Operating in Emulation (Debug) Mode |

| 10             | Updated Section 1.1, Device and Development-Support Tool Nomenclature                                                                                                  |

| 47             | CPU_116, Interrupted Nesting of Loops May Stop CPU Execution:<br>– Details section: corrected hierarchy of bulleted list                                               |

| 50             | Added CPU_118, CPU May Halt After Returning From an Interrupt Service Routine When Operating in Emulation (Debug) Mode                                                 |

| 51             | Added CPU_119, Due to Improper Update of the DBSTAT Register, the Debugger May Halt at Code Locations Where No Breakpoints are Set <b>[Revision G]</b>                 |

### Contents

| 1 | Intro | duction       |                                                                                                                               | . 5  |

|---|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------|------|

|   | 1.1   | Device and    | Development-Support Tool Nomenclature                                                                                         | 10   |

| 2 | Impo  | ortant Notice | s About CPU Advisories                                                                                                        | . 11 |

|   | -     |               | ilicon Advisory Information                                                                                                   |      |

|   | 2.2   | Useful Infor  | mation Regarding Assembler Diagnostic Messages                                                                                | . 11 |

|   |       | 2.2.1 ERR     | OR Diagnostics                                                                                                                | . 11 |

|   |       | 2.2.2 WAR     | RNING Diagnostics                                                                                                             | . 11 |

|   |       | 2.2.3 REM     | IARK Diagnostics                                                                                                              | . 11 |

| 3 | C552  | x CPU Knowr   | n Design Advisories to Functional Specifications                                                                              | . 13 |

|   |       | CPU_72        | C54CM Bit Update and *CDP With T0 Index is not Pipeline-Protected                                                             |      |

|   |       | CPU_73        | Certain Instructions not Pipeline-Protected From Resets                                                                       |      |

|   |       | CPU_76        | DELAY Smem Does not Work With Circular Addressing                                                                             |      |

|   |       | CPU_79        | IDLE Cannot Copy the Content of ICR to ISTR                                                                                   | 15   |

|   |       | CPU_80        | Nested Local Repeat Corrupted After C54CM Bit Reset                                                                           | 16   |

|   |       | CPU_81        | WHILE Instruction in Slot #2 is not Protected                                                                                 | 16   |

|   |       | CPU_82        | 'if (cond true) goto' at the End of Local Repeat Fails                                                                        | 17   |

|   |       | CPU_83        | BRAF Updated Incorrectly in Certain Cases of Conditional Execution                                                            | 17   |

|   |       | CPU_84        | SP/SSP Access Followed by a Conditional Execute is not Protected Against Interrupts                                           | 18   |

|   |       | CPU_85        | Local Repeat With C54CM = 1 may be Corrupted on its Last Iteration                                                            | 19   |

|   |       | CPU_86        | Corruption of CSR or BCRx Register Read When Executed in Parallel With Write                                                  | 19   |

|   |       | CPU_87        | Context Restore Just Before Return Instruction Sometimes Fails                                                                | 20   |

|   |       | CPU_88        | Incorrect Context Store of BRAF During Interrupt Servicing                                                                    | 21   |

|   |       | CPU_89        | Internal Overflow not Detected When Using the Left Shift Command                                                              | 22   |

|   |       | CPU_90        | CPU Bypass Can Cause Corruption of a Read Following a Write                                                                   | 23   |

|   |       | CPU_91        | C16, XF, and HM Bits not Reinitialized by Software Reset                                                                      | 24   |

|   |       | CPU_92        | Consecutive C-Bus Accesses may not Work                                                                                       | 24   |

|   |       | CPU_93        | Interrupted Conditional Execution After Memory Write may Execute Unconditionally in the D Unit                                | 26   |

|   |       | CPU_94        | Interrupted Conditional Execution After Long Memory-Mapped Register Write is Executed Unconditionally in the D Unit / AD Unit | . 27 |

|   |       | CPU_95        | BRCx Decrement may not Work When gotoP24 is put at End of Blockrepeat<br>With C54CM = 0                                       | . 29 |

|   |       | CPU_96        | gotoP24 Within Blockrepeat Exits the Loop                                                                                     | 30   |

|   |       | CPU_97        | RETA = Lmem    Lmem = RETA may not Work                                                                                       | 31   |

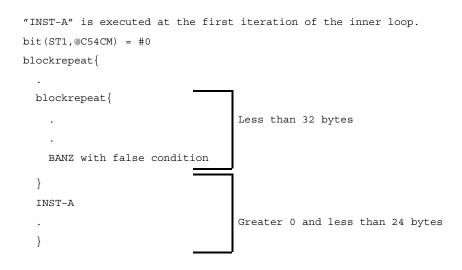

|   |       | CPU_98        | BANZ at the End of Inner Loop in Native Mode may Corrupt Program Flow                                                         | 32   |

|   |       | CPU_99        | Return_int (Under a Fast Return Configuration) may Cause Improper Operation of                                                |      |

|   |       |               | Single Repeats and Conditional Executions                                                                                     |      |

|   |       | CPU_100       | Interrupted Single Repeat is not Resumed After RETI                                                                           | 34   |

| CPU_102         | Page Register Update and CPU Bypass Corrupts Following Memory Read                                                     | 35 |

|-----------------|------------------------------------------------------------------------------------------------------------------------|----|

| CPU_103         | C54x Instruction, FRET[D] is not Protected Against Prior C54CM Bit Update                                              | 37 |

| CPU_104         | Blockrepeat Corrupted if Preceded by Localrepeat With C54CM = 1 and BRC0 = 0                                           | 37 |

| CPU_106         | Move (Shift and Store) Instructions Incompatible With C54x When<br>C54CM Bit = 1 and SST Bit = 1                       | 38 |

| CPU_107         | Conditional Call With False Condition Corrupts RETA                                                                    | 40 |

| CPU_108         | Long (32-Bit) Read From MMR Gets Corrupted                                                                             | 41 |

| CPU_109         | Bus Error Issued on Byte Access to I/O Space With Address Range 0x0 to 0x5f                                            | 42 |

| CPU_110         | Relative Branch in ISR Corrupts Program Flow When Localrepeat With C54CM = 1 is Interrupted                            | 43 |

| CPU_111         | C54CM Bit Modification Followed by a mar Instruction Not Pipeline-Protected                                            | 44 |

| CPU_112         | Data Page Register and Stack Pointer Update Not Pipeline-Protected Against Data Move Instructions                      | 45 |

| CPU_114         | ST2 Update and Dual-Memory Access With Circular Qualifier Not Pipeline-Protected                                       | 46 |

| CPU_116         | Interrupted Nesting of Loops May Stop CPU Execution                                                                    | 47 |

| CPU_117         | Updating BRC Prior to a Loop That Contains Only Single Repeats Incorrectly Decrements the RPTC                         | 48 |

| CPU_118         | CPU May Halt After Returning From an Interrupt Service Routine When<br>Operating in Emulation (Debug) Mode             | 50 |

| CPU_119         | Due to Improper Update of the DBSTAT Register, the Debugger May Halt at<br>Code Locations Where No Breakpoints are Set | 51 |

| Documentation S | Support                                                                                                                | 53 |

4

•

#### 1 Introduction

This document describes functional exceptions to the CPU behavior described in the *TMS320C55x DSP CPU Reference Guide* (literature number SPRU371). Non-CPU issues are described in the device-specific silicon errata. [For advisories on the OMAP5910 dual-core processor, see the *OMAP5910 Dual-Core Processor Silicon Errata* (literature number SPRZ016).] See Section 4 for a listing of related documentation.

A quick reference table (Table 1) is included so that advisory descriptions may be quickly located from the short description of each advisory. The advisory number in the first column of the table is referenced in the title of each advisory description that follows in Section 3. The columns on the right of the table indicate whether the advisory is present on the indicated silicon revision. The CPU advisories can be grouped into three primary categories:

- Parallel Execution Issues

These issues are related to specific combinations of instructions executed in parallel. In

most cases, these issues can be avoided by not executing the instructions in parallel.

- Pipeline-protection Issues These issues are cases where the pipeline is not properly automatically protected for specific instruction sequences. In most cases, these problems can be corrected by rearranging the instruction sequences, or by adding NOP instructions.

- Other Issues These are the issues that do not fall into one of the above two categories.

The legend following indicates which symbols are used for each case.

| II    | The advisory is present on this silicon revision and is related to parallel instruction execution.  |

|-------|-----------------------------------------------------------------------------------------------------|

| Р     | The advisory is present on this silicon revision and is related to pipeline protection.             |

| Х     | The advisory is present on this silicon revision and not related to either of the above categories. |

| fixed | The advisory <b>is not</b> present on this silicon revision.                                        |

| N/A   | The advisory <b>is not</b> applicable to this device.                                               |

| Advisory | Device:                                                                                   | 5501     | 5502     | 5503     | 5507     | 5509A    | 5510      | OMAP5910 | OMAP5912 |

|----------|-------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|-----------|----------|----------|

| Number   | Silicon Revision:                                                                         | All revs | 2.1 / 2.2 | All revs | All revs |

| CPU_72   | C54CM Bit Update and *CDP<br>With T0 Index is not<br>Pipeline-Protected                   | N/A      | N/A      | N/A      | N/A      | N/A      | Ρ         | N/A      | N/A      |

| CPU_73   | Certain Instructions not<br>Pipeline-Protected From<br>Resets                             | N/A      | N/A      | N/A      | N/A      | N/A      | Ρ         | Р        | Р        |

| CPU_76   | DELAY Smem Does not Work<br>With Circular Addressing                                      | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | Х        | Х        |

| CPU_79   | IDLE Cannot Copy the<br>Content of ICR to ISTR                                            | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | N/A      | N/A      |

| CPU_80   | Nested Local Repeat<br>Corrupted After C54CM Bit<br>Reset                                 | N/A      | N/A      | N/A      | N/A      | N/A      | Р         | N/A      | N/A      |

| CPU_81   | WHILE Instruction in Slot #2<br>is not Protected                                          | N/A      | N/A      | N/A      | N/A      | N/A      | Ρ         | N/A      | N/A      |

| CPU_82   | ʻif(cond true) goto' at the End<br>of Local Repeat Fails                                  | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | Х        | Х        |

| CPU_83   | BRAF Updated Incorrectly in<br>Certain Cases of Conditional<br>Execution                  | N/A      | N/A      | N/A      | N/A      | N/A      | х         | Х        | Х        |

| CPU_84   | SP/SSP Access Followed by<br>a Conditional Execute is not<br>Protected Against Interrupts | N/A      | N/A      | N/A      | N/A      | N/A      | Ρ         | Р        | Р        |

| CPU_85   | Local Repeat With<br>C54CM = 1 may be Corrupted<br>on its Last Iteration                  | N/A      | N/A      | N/A      | N/A      | N/A      | х         | х        | Х        |

| CPU_86   | Corruption of CSR or BCRx<br>Register Read When<br>Executed in Parallel With<br>Write     | N/A      | N/A      | N/A      | N/A      | N/A      | II        | ll       | Ι        |

| CPU_87   | Context Restore Just Before<br>Return Instruction Sometimes<br>Fails                      | N/A      | N/A      | N/A      | N/A      | N/A      | Ρ         | Р        | Р        |

| CPU_88   | Incorrect Context Store of<br>BRAF During Interrupt<br>Servicing                          | N/A      | N/A      | N/A      | N/A      | N/A      | II        | II       | II       |

| CPU_89   | Internal Overflow not<br>Detected When Using the Left                                     | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | Х        | Х        |

#### Table 1. Quick Reference Table

Shift Command

| Advisory | Device:                                                                                                                                      | 5501     | 5502     | 5503     | 5507     | 5509A    | 5510      | OMAP5910 | OMAP5912 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|-----------|----------|----------|

| Number   | Silicon Revision:                                                                                                                            | All revs | 2.1 / 2.2 | All revs | All revs |

| CPU_90   | CPU Bypass Can Cause<br>Corruption of a Read<br>Following a Write                                                                            | N/A      | N/A      | N/A      | N/A      | N/A      | fixed     | fixed    | fixed    |

| CPU_91   | C16, XF, and HM Bits not<br>Reinitialized by Software<br>Reset                                                                               | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | Х        | х        |

| CPU_92   | Consecutive C-Bus Accesses<br>may not Work                                                                                                   | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | N/A      | N/A      |

| CPU_93   | Interrupted Conditional<br>Execution After Memory Write<br>may Execute Unconditionally<br>in the D Unit                                      | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | N/A      | N/A      |

| CPU_94   | Interrupted Conditional<br>Execution After Long<br>Memory-Mapped Register<br>Write is Executed<br>Unconditionally in the D Unit /<br>AD Unit | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | x        | х        |

| CPU_95   | BRCx Decrement may not<br>Work When gotoP24 is put at<br>End of Blockrepeat With<br>C54CM = 0                                                | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | Х        | Х        |

| CPU_96   | gotoP24 Within Blockrepeat<br>Exits the Loop                                                                                                 | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | Х        | Х        |

| CPU_97   | RETA = Lmem    Lmem =<br>RETA may not Work                                                                                                   | N/A      | N/A      | N/A      | N/A      | N/A      | II        | I        | ll       |

| CPU_98   | BANZ at the End of Inner<br>Loop in Native Mode may<br>Corrupt Program Flow                                                                  | N/A      | N/A      | N/A      | N/A      | N/A      | х         | Х        | х        |

| CPU_99   | Return_int (Under a Fast<br>Return Configuration) may<br>Cause Improper Operation of<br>Single Repeats and<br>Conditional Executions         | N/A      | N/A      | N/A      | N/A      | N/A      | Х         | ×        | Х        |

| CPU_100  | Interrupted Single Repeat is<br>not Resumed After RETI                                                                                       | N/A      | N/A      | N/A      | N/A      | N/A      | х         | Х        | Х        |

| CPU_102  | Page Register Update and<br>CPU Bypass Corrupts<br>Following Memory Read                                                                     | N/A      | N/A      | N/A      | N/A      | N/A      | х         | Х        | х        |

| CPU_103  | C54x Instruction, FRET[D] is<br>not Protected Against Prior<br>C54CM Bit Update                                                              | х        | Х        | Х        | х        | Х        | II        | N/A      | N/A      |

### Table 1. Quick Reference Table (Continued)

| Advisory | Device:                                                                                                    | 5501     | 5502     | 5503     | 5507     | 5509A    | 5510      | OMAP5910 | OMAP5912 |

|----------|------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|-----------|----------|----------|

| Number   | Silicon Revision:                                                                                          | All revs | 2.1 / 2.2 | All revs | All revs |

| CPU_104  | Blockrepeat Corrupted if<br>Preceded by Localrepeat With<br>C54CM = 1 and BRC0 = 0                         | Х        | Х        | Х        | Х        | Х        | Х         | Х        | Х        |

| CPU_106  | Move (Shift and Store)<br>Instructions Incompatible With<br>C54x When C54CM Bit = 1<br>and SST Bit = 1     | Х        | Х        | Х        | Х        | Х        | Х         | Х        | Х        |

| CPU_107  | Conditional Call With False<br>Condition Corrupts RETA                                                     | Х        | х        | х        | х        | х        | х         | Х        | Х        |

| CPU_108  | Long (32-Bit) Read From<br>MMR Gets Corrupted                                                              | х        | х        | х        | х        | х        | х         | Х        | Х        |

| CPU_109  | Bus Error Issued on Byte<br>Access to I/O Space With<br>Address Range 0x0 to 0x5f                          | Х        | Х        | Х        | Х        | Х        | Х         | х        | Х        |

| CPU_110  | Relative Branch in ISR<br>Corrupts Program Flow When<br>Localrepeat With C54CM = 1<br>is Interrupted       | Х        | Х        | Х        | Х        | Х        | Х         | Х        | Х        |

| CPU_111  | C54CM Bit Modification<br>Followed by a mar Instruction<br>Not Pipeline-Protected                          | Ρ        | Ρ        | Ρ        | Ρ        | Ρ        | Ρ         | Р        | Р        |

| CPU_112  | Data Page Register and Stack<br>Pointer Update Not<br>Pipeline-Protected Against<br>Data Move Instructions | Ρ        | Ρ        | Ρ        | Ρ        | Ρ        | Ρ         | Ρ        | Ρ        |

| CPU_114  | ST2 Update and<br>Dual-Memory Access With<br>Circular Qualifier Not<br>Pipeline-Protected                  | Ρ        | Ρ        | Ρ        | Ρ        | Ρ        | Ρ         | Ρ        | Ρ        |

| CPU_116  | Interrupted Nesting of Loops<br>May Stop CPU Execution                                                     | Р        | Ρ        | Р        | Р        | Ρ        | Р         | Р        | Р        |

| CPU_117  | Updating BRC Prior to a Loop<br>That Contains Only Single<br>Repeats Incorrectly<br>Decrements the RPTC    | Х        | Х        | Х        | Х        | Х        | Х         | х        | Х        |

Table 1. Quick Reference Table (Continued)

| Advisory | Device:                                                                                                                         | 5501     | 5502     | 5503     | 5507     | 5509A    | 5510      | OMAP5910 | OMAP5912 |

|----------|---------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|-----------|----------|----------|

| Number   | Silicon Revision:                                                                                                               | All revs | 2.1 / 2.2 | All revs | All revs |

| CPU_118  | CPU May Halt After Returning<br>From an Interrupt Service<br>Routine When Operating in<br>Emulation (Debug) Mode                | Х        | Х        | Х        | Х        | Х        | Х         | Х        | Х        |

| CPU_119  | Due to Improper Update of<br>the DBSTAT Register, the<br>Debugger May Halt at<br>Code Locations Where No<br>Breakpoints are Set | Х        | х        | х        | х        | х        | х         | Х        | х        |

Table 1. Quick Reference Table (Continued)

#### 1.1 Device and Development-Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all DSP devices and support tools. Each DSP commercial family member has one of three prefixes: TMX, TMP, or TMS (e.g., **TMS**320VC5502GZZ). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully qualified production devices/tools (TMS/TMDS).

Device development evolutionary flow:

- TMX Experimental device that is not necessarily representative of the final device's electrical specifications

- **TMP** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

- **TMS** Fully qualified production device

Support tool development evolutionary flow:

- **TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing.

- TMDS Fully qualified development-support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

TMS devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

### 2 Important Notices About CPU Advisories

#### 2.1 Prototype Silicon Advisory Information

The list of advisories included in this document may include all prototype versions of a device. As prototype silicon revisions become obsolete, they will be removed from this document. Please consult your local sales representative if you need information concerning previous silicon revisions not listed in this document.

#### 2.2 Useful Information Regarding Assembler Diagnostic Messages

The TMS320C55x Assembler will generate three types of diagnostic messages when it detects a potential or probable Silicon Exception.

#### 2.2.1 ERROR Diagnostics

The assembler generates ERROR diagnostics in cases where it can fully determine that the code will cause a silicon exception to occur on hardware.

#### 2.2.2 WARNING Diagnostics

The assembler generates WARNING diagnostics in cases where it can fully determine that the code will cause a silicon exception to occur on hardware, but which, under certain circumstances, may not be an issue for the user.

#### 2.2.3 REMARK Diagnostics

The assembler generates REMARK diagnostics in conditions where it can fully determine that the code may cause a silicon exception to occur on hardware, but the exception itself also depends on non-visible trigger conditions that the assembler has no knowledge of, such as whether interrupts are enabled.

Since the assembler cannot determine the state of these trigger conditions, it cannot know that the exception will affect this code. Therefore, it generates a REMARK to instruct the user to examine the code and evaluate whether this is a potential silicon exception situation. (Please see the following sections for how to suppress remarks in situations where you have determined that the other trigger conditions do not exist.)

#### Intended Treatment of REMARK Diagnostics

The intent of generating REMARK diagnostics is to inform the user that the code could potentially cause a silicon exception and that it should be reviewed by the user side by side with the trigger conditions and a determination be made whether the code is a potential silicon exception situation.

If the code is determined to be a potential silicon exception situation, users should modify their code to prevent that exception from occurring.

If users determine that their code will not cause a silicon exception based on the trigger conditions, then the REMARK that the assembler generates can be suppressed. There are two methods of doing so; please see the "Suppressing REMARK Diagnostics" section.

#### Suppressing REMARK Diagnostics

Once the user determines that a silicon exception REMARK diagnostic is not appropriate for the code as written, the REMARK diagnostic can be suppressed in one of the following ways.

#### **REMARK Directives:**

The .noremark/.remark directives can be used to suppress the generation of a REMARK diagnostic for particular regions of code. The .noremark directive turns off the generation of a particular REMARK diagnostic. The .remark directive re-enables the generation of a particular REMARK diagnostic.

A '.noremark ##' (where ## is the remark id) directive is placed at the beginning of the region, and a '.remark ##' directive is placed at the end of the region.

**NOTE:** The .noremark/.remark directive combination should always be placed around the entire region of code that participates in the potential silicon exception. Otherwise, spurious diagnostics may still be generated.

Additionally, the user has the option of disabling a silicon exception diagnostic for the entire file by placing just the .noremark directive at the top of the assembly file. However, this may be dangerous if, during inevitable code maintenance, the code is modified by someone not familiar with all the exception conditions. Please take great care when using the directives in this manner.

#### **REMARK Command-Line Options:**

The compiler shell (cl55) supports a command line option to suppress a particular REMARK diagnostic. The shell option –ar# (where # is the assembler's silicon exception id as described above) will suppress the named REMARK for the entire scope of all assembly files compiled with that command. Using the option –ar without a number will suppress all REMARK diagnostics.

Again, this may be dangerous if, during inevitable code maintenance, the code is modified by someone not familiar with all the silicon exception conditions. Please take great care when using the command-line REMARK options. Using the .noremark/.remark directives covering the shortest possible range of source lines is much safer.

#### **PENDING Assembler Notification Status:**

In the advisory descriptions, an assembler notification status marked "Pending" indicates the current version of the code generation tools do not yet detect the condition. As versions of the tools are released, known issues are included.

### 3 C55x CPU Known Design Advisories to Functional Specifications

| Advisory CPU_72         | C54CM Bit Update and *CDP With T0 Index is not Pipeline-Protected                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Details:                | When the C54CM bit in status register 1 (ST1_55) is set to 1, the T0 index for single/dual/coefficient memory accesses should be replaced with AR0 for 54x compatibility. Therefore, if a C54CM bit update is followed by an instruction utilizing the Data Address Generator and T0 index, a stall should be generated to postpone the Data Address Generator until the C54CM bit update is complete. In the following cases, the stall is not created and the incorrect index is used (AR0/T0): |  |  |  |  |  |  |  |

|                         | Case 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                         | C54CM bit update by bit instruction<br>0–4 cycles<br>B-bus access with 'coef(*CDP+T0)' using address modifier: *ABS16(#k) or *(#k).                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                         | Case 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                         | C54CM bit update by MMR write<br>0–5 cycles<br>B-bus access with 'coef(*CDP+T0)' using address modifier: *ABS16(#k) or *(#k).                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                         | Algebraic example         bit(ST1,#5) = #1       ; set C54CM (=1)         AC0 = *(#60h)*coef(*(CDP+T0))       ; T0 incorrectly used as index                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                         | Mnemonic exampleBSET #5, ST1_55; set C54CM (=1)MOV (#60h)*coef(*(CDP+T0)), AC0; T0 incorrectly used as index; 0xaaaa                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Assembler Notification: | Assembler (versions 2.00 and later) will generate a REMARK when this condition is found.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Workaround(s):          | <ol> <li>In the case where the C54CM bit is updated by a bit instruction, maintain at least 5 cycles<br/>(useful code or NOPs) between the C54CM bit update and the Data Address Generator<br/>instruction.</li> </ol>                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                         | <ol> <li>In the case where the C54CM bit is updated by a MMR write of ST1_55, maintain at least<br/>6 cycles (useful code or NOPs) between the C54CM bit update and the Data Address<br/>Generator instruction.</li> </ol>                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Advisory CPU_73         | Certain Instructions not Pipeline-Protected From Resets                                                                                                                                                                            |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                                                        |

| Details:                | In the following cases, instructions may not execute properly due to insufficient pipeline protection from reset conditions:                                                                                                       |

|                         | Case 1                                                                                                                                                                                                                             |

|                         | The following instruction(s) is not executed properly when closely preceded by a hardware or<br>software reset:<br>DP = #K16 ;OR<br>Data Address Generator operation affected by any status bit ;OR<br>if (cond) execute (AD Unit) |

|                         | These instructions (which depend on ST0_55, ST1_55 and ST2_55) will not execute correctly if they are located in the first four instructions following the reset (including the delay slot in the reset vector).                   |

|                         | Case 2                                                                                                                                                                                                                             |

|                         | IFR0/1 or ST1 MMR read instructions may return invalid read data when followed by a software reset.                                                                                                                                |

|                         | Case 3                                                                                                                                                                                                                             |

|                         | The BRAF bit is not cleared correctly by a software reset which follows the bit (ST1, #BRAF) = #1 instruction.                                                                                                                     |

| Assembler Notification: | None                                                                                                                                                                                                                               |

| Workaround:             | Use the appropriate workaround, based on the Case.                                                                                                                                                                                 |

|                         | Case 1                                                                                                                                                                                                                             |

|                         | Do not put the following instruction(s) in the delay slot (last four bytes after the interrupt vector). Also do not use the following instruction(s) as the first, second, or third instructions at beginning of program space:    |

|                         | DP = #K16 ;OR<br>DAGEN-operation affected by any status bit ;OR<br>if (cond) execute (AD Unit)                                                                                                                                     |

|                         | Case 2                                                                                                                                                                                                                             |

|                         | Ensure at least 3 cycles between IFR0/1 or ST1 MMR read and a software reset.                                                                                                                                                      |

|                         | Case 3                                                                                                                                                                                                                             |

|                         | Ensure at least 5 cycles between bit(ST1, #BRAF) = #1 and a software reset                                                                                                                                                         |

| Advisory CPU_76         | DELAY Smem Does not Work With Circular Addressing                                                                                                                                                                                                                                                        |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                                                                                                                              |

| Details:                | When using circular addressing mode with the 'DELAY Smem' instruction in the following case:                                                                                                                                                                                                             |

|                         | smem = (end address of a circular buffer)                                                                                                                                                                                                                                                                |

|                         | the incorrect destination address is used for the delay instruction. The destination address used is (end of circular buffer)+1, which is outside of the circular buffer. The correct functionality would be for the destination address to wrap around to the beginning address of the circular buffer. |

| Assembler Notification: | Assembler (version 2.3 and later) will detect the use of delay (Smem) and generate a REMARK.                                                                                                                                                                                                             |

| Workaround:             | Do not use circular addressing mode with the 'DELAY' instruction.                                                                                                                                                                                                                                        |

| Advisory CPU_79         | IDLE Cannot Copy the Content of ICR to ISTR                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Details:                | When an IDLE instruction is decoded, the content of the Idle Configuration Register (ICR) is supposed to be copied to the Idle Status Register (ISTR) when the instruction preceding the IDLE completes its write phase. However, during the following sequence, the ICR to ISTR copy does not happen: |  |  |  |  |  |  |

|                         | 1. IDLE is decoded.                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                         | <ol> <li>A wakeup interrupt condition (NMI or any maskable interrupt which is enabled in the<br/>IER0/IER1 registers) is captured or is currently pending.</li> </ol>                                                                                                                                  |  |  |  |  |  |  |

|                         | 3. The ICR to ISTR would normally happen here, but does not occur.                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Assembler Notification: | None                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Workaround:             | Make sure all interrupts are masked (disabled) via the IER0/IER1 registers before IDLE instruction is decoded. This workaround does not work for the NMI interrupt.                                                                                                                                    |  |  |  |  |  |  |

| Advisory CPU_80         | Nested Local Repeat Corrupted After C54CM Bit Reset                                                                                                                                            |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                    |

| Details:                | When the following conditions occur:                                                                                                                                                           |

|                         | • A local repeat follows another local repeat (nested local repeats).                                                                                                                          |

|                         | • The first local repeat is stalled in the address phase due to a C54CM bit update from 1 to 0,                                                                                                |

|                         | The CPU jumps to the wrong instruction address when leaving the outer repeat loop.                                                                                                             |

|                         | <pre>Algebraic example bit (ST1, #5) = #0 nop nop ; insert additional NOP here to implement workaround localrepeat {</pre>                                                                     |

| Assembler Notification: | loop<br>Assembler (version 2.30 and greater) will generate a WARNING when these conditions occur.                                                                                              |

| Workaround(s):          | <ol> <li>In the case of a C54CM bit update by a bit instruction to register ST1. Ensure that the<br/>C54CM bit update occurs a least four (4) cycles before the first local repeat.</li> </ol> |

|                         | 2. In the case of a C54CM bit update by an MMR instruction. Ensure that the C54CM bit                                                                                                          |

| Advisory CPU_81         | WHILE Instruction in Slot #2 is not Protected                                                                                                                                                                                                                                                                                      |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                                                                                                                                                        |

| Details:                | When WHILE instruction is located as second slot and single repeated instruction follows after one null slot that is caused by any pipeline discontinuity, the WHILE instruction is not pipeline protected. If the single repeat instruction follows WHILE instruction immediately or there are more than one null slot, it works. |

| Assembler Notification: | Assembler (version 1.83 and greater) will generate an ERROR when a WHILE operation is found in the second position of a parallel pair.                                                                                                                                                                                             |

| Workaround:             | Do not use the WHILE instruction in the second slot of a parallel instruction pair.                                                                                                                                                                                                                                                |

update occurs a least five (5) cycles before the first local repeat.

| Advisory CPU_82         | <i>'if (cond true) goto' at the End of Local Repeat Fails</i>                                                                                                                                                                                                                                           |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                                                                                                                             |

| Details:                | Within any local repeat block if a conditional branch instruction is placed at the second to last position, and the branch target is at the last position of the loop, the program flow is corrupted. This is the case regardless of whether the local repeat is the outer loop or a nested inner loop. |

|                         | Algebraic example                                                                                                                                                                                                                                                                                       |

|                         | localrepeat{                                                                                                                                                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                                                         |

|                         | ·                                                                                                                                                                                                                                                                                                       |

|                         | if (cond true) goto TARGET                                                                                                                                                                                                                                                                              |

|                         | TARGET                                                                                                                                                                                                                                                                                                  |

|                         | nop                                                                                                                                                                                                                                                                                                     |

|                         | }                                                                                                                                                                                                                                                                                                       |

|                         |                                                                                                                                                                                                                                                                                                         |

| Assembler Notification: | None                                                                                                                                                                                                                                                                                                    |

| Workaround:             | Do not use this instruction sequence.                                                                                                                                                                                                                                                                   |

| Advisory CPU_83         | BRAF Updated Incorrectly in Certain Cases of Conditional Execution                                                                                                                                                                                |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                                                                       |

| Details:                | When C54CM=1 and one of the following cases occurs, the BRAF bit is modified regardless of the condition.                                                                                                                                         |

|                         | <ul> <li>if(cond=false)Execute(D_unit)    bit(ST1, @BRAF) = #0/1</li> </ul>                                                                                                                                                                       |

|                         | <ul> <li>while(cond=false &amp;&amp; (RPTC &lt; k8)) bit(ST1, @BRAF) = #0/1</li> </ul>                                                                                                                                                            |

| Assembler Notification: | Assembler (version 2.3 and greater) will attempt to detect the cases above and generate a WARNING.                                                                                                                                                |

| Workaround(s):          | <ol> <li>Use the AD-unit instead of the D-unit in the conditional execution instruction<br/>OR<br/>Do not use parallelism (use conditional execute of next instruction as opposed to<br/>conditional execute of parallel instruction).</li> </ol> |

|                         | 2. Do not use a bit instruction that modifies BRAF within the WHILE instruction                                                                                                                                                                   |

| Advisory CPU_84         | SP/SSP Access Followed by a Conditional Execute is not Protected Against Interrupts                                                                                                                                                                                                                         |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                                                                                                                                 |

| Details:                | Any of the following instructions are not protected against interrupts when followed by a AD-unit conditional execute instruction for which the condition is false. (This exception only applies to conditional execution of the next instruction and not a conditional execute of a parallel instruction): |

|                         | MMR-read access to SP/SSP                                                                                                                                                                                                                                                                                   |

|                         | • dst = XSP/XSSP                                                                                                                                                                                                                                                                                            |

|                         | • dbl(Lmem) = XSP/XSSP                                                                                                                                                                                                                                                                                      |

|                         | <ul> <li>push_both(XSP/XSSP)</li> </ul>                                                                                                                                                                                                                                                                     |

|                         | • XSP/XSSP = pop()                                                                                                                                                                                                                                                                                          |

|                         | MMR-write access to SP/SSP                                                                                                                                                                                                                                                                                  |

|                         | Algebraic example<br>{<br>nop<br>SP = SP - #1<br>if (TC1) execute (AD_Unit) ;where TC1=0, condition is false.<br><interrupt occurs=""><br/>AR6 -= #1<br/></interrupt>                                                                                                                                       |

| Assembler Notification: | Assembler (version 2.3 and greater) will attempt to identify a code sequence that may cause the exception, and will generate a REMARK.                                                                                                                                                                      |

| Workaround(s):          | <ol> <li>When SP/SSP is read in the read phase, insert two (2) NOPs between the SP/SSP<br/>instruction and the conditional execute instruction.</li> </ol>                                                                                                                                                  |

|                         | 2. When SP/SSP is read or written in the execute phase, insert three (3) NOPs between the SP/SSP instruction and the conditional execute instruction.                                                                                                                                                       |

|                         | <ol> <li>When SP/SSP is written in the write phase, insert four (4) NOPs between the SP/SSP<br/>instruction and the conditional execute instruction.</li> </ol>                                                                                                                                             |

| Advisory CPU_85         | Local Repeat With C54CM = 1 may be Corrupted on its Last Iteration                                                                                                                         |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                |

| Details:                | Under the following conditions during a local repeat loop:                                                                                                                                 |

|                         | • C54CM = 1                                                                                                                                                                                |

|                         | • The program fetch is occurring to restart the last iteration of the local repeat loop                                                                                                    |

|                         | The program fetch is stalled                                                                                                                                                               |

|                         | The local repeat may be overwritten even though the last iteration has not been completed.                                                                                                 |

| Assembler Notification: | Assembler (version 2.3 and greater) will generate a WARNING when a .C54CM_ON directive is seen and a local repeat is encountered.                                                          |

| Workaround:             | Do not use local repeat loops with $C54CM = 1$ .                                                                                                                                           |

|                         |                                                                                                                                                                                            |

| Advisory CPU_86         | Corruption of CSR or BCRx Register Read When Executed in Parallel With Write                                                                                                               |

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                |

| Details:                | Under the following conditions:                                                                                                                                                            |

|                         | • CSR, BRC0, or BRC1 register is read in the EXE phase in parallel with a write to the same register                                                                                       |

|                         | The instruction is stalled due to a previous write access                                                                                                                                  |

|                         | The register read may be corrupted, returning the new value from the register write instruction.<br>The possible parallel instruction pairs which may cause this condition are as follows: |

|                         | Smem= CSR  CSR = TAx;Smem should be updated by old register value, butSmem= CSR  CSR = Smem;updated to TAx value instead                                                                   |

|                         | Smem=BRC0 $\parallel$ BRC0 = TAxSmem=BRC0 $\parallel$ BRC0 = SmemTAx=BRC0 $\parallel$ BRC0 = TAxTAx=BRC0 $\parallel$ BRC0 = Smem                                                           |

|                         | Smem=BRC1 $\parallel$ BRC1 = TAxSmem=BRC1 $\parallel$ BRC1 = SmemTAx=BRC1 $\parallel$ BRC1 = TAxTAx=BRC1 $\parallel$ BRC1 = Smem                                                           |

| Assembler Notification: | Assembler (version 2.3 and greater) will detect the above parallel pairs and generate a WARNING.                                                                                           |

| Workaround:             | Do not execute these instructions in parallel.                                                                                                                                             |

| Advisory CPU_87         | Context Restore Just Before Return Instruction Sometimes Fails                                                                                                                                                                                                     |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                                                                                        |

| Details:                | A context restore just before the return instruction sometimes fails. There are two cases in which this condition may occur:                                                                                                                                       |

|                         | <i>Case 1:</i> When the C54CM bit in ST1_55 is updated via MMR write just before the return instruction, a failure may occur. In the following sequence:                                                                                                           |

|                         | *(ST1_55) = < <i>value&gt;</i><br>return                                                                                                                                                                                                                           |

|                         | the new value of the C54CM bit is not used by the return instruction. This may eventually lead to a BRAF recovery error. When C54CM=1, BRAF is not recovered by return. When C54CM=0, BRAF is recovered.                                                           |

|                         | This failure occurs under the following conditions:                                                                                                                                                                                                                |

|                         | <ul> <li>C54CM bit is modified by ST1_55 context restore, AND</li> </ul>                                                                                                                                                                                           |

|                         | • the return condition is either 'return' with slow-return configuration, OR, 'if() return' with fast or slow return configuration.                                                                                                                                |

|                         | Case 2: Altering the BRAF bit just before 'return_int' instruction. In the following sequence:                                                                                                                                                                     |

|                         | C54CM = #1                                                                                                                                                                                                                                                         |

|                         | <br>any BRAF update<br>return_int                                                                                                                                                                                                                                  |

|                         | In the fast-return configuration, BRAF is recovered immediately after return_int is decoded (along with return address). Due to lack of pipeline protection, the BRAF contents recovered by 'return_int' is overwritten by the instruction preceding 'return_int'. |

|                         | This failure occurs under the following conditions:                                                                                                                                                                                                                |

|                         | • C54CM = 1, AND                                                                                                                                                                                                                                                   |

|                         | • the return condition is either 'return' with fast-return configuration.                                                                                                                                                                                          |

| Assembler Notification: | Assembler (version 2.3 and greater) will generate a REMARK when it detects the above instruction sequences.                                                                                                                                                        |

| Workaround:             | Use one of the following workarounds.                                                                                                                                                                                                                              |

|                         | Case 1: Insert at least one NOP between the MMR access and the return instruction.                                                                                                                                                                                 |

|                         | <i>Case 2:</i> Do not recover the BRAF context with an instruction that accesses BRAF. Instead, let the return instruction recover the BRAF content.                                                                                                               |

| Advisory CPU_88         | Incorrect Context Store of BRAF During Interrupt Servicing                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                                                                                                                                                                                                                                                                                                                                                                                                               |

| Revision(s) Affected:   | See Table 1                                                                                                                                                                                                                                                                                                                                                                                                   |