## TMS320C6000 DSP Power-Down Logic and Modes Reference Guide

Literature Number: SPRU728C March 2005

## Preface

## **Read This First**

#### About This Manual

This document describes the power-down logic and modes used by the digital signal processors (DSPs) of the TMS320C6000<sup>™</sup> DSP family.

#### Notational Conventions

This document uses the following conventions.

□ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

#### **Related Documentation From Texas Instruments**

The following documents describe the C6000<sup>TM</sup> devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

- **TMS320C6000 CPU and Instruction Set Reference Guide** (literature number SPRU189) describes the TMS320C6000<sup>™</sup> CPU architecture, instruction set, pipeline, and interrupts for these digital signal processors.

- **TMS320C6000 DSP Peripherals Overview Reference Guide** (literature number SPRU190) describes the peripherals available on the TMS320C6000<sup>™</sup> DSPs.

- **TMS320C6000 Technical Brief** (literature number SPRU197) gives an introduction to the TMS320C62x<sup>™</sup> and TMS320C67x<sup>™</sup> DSPs, development tools, and third-party support.

- **TMS320C64x Technical Overview** (SPRU395) gives an introduction to the TMS320C64x<sup>™</sup> DSP and discusses the application areas that are enhanced by the TMS320C64x VelociTI<sup>™</sup>.

- **TMS320C6000 Programmer's Guide** (literature number SPRU198) describes ways to optimize C and assembly code for the TMS320C6000<sup>™</sup> DSPs and includes application program examples.

- **TMS320C6000 Code Composer Studio Tutorial** (literature number SPRU301) introduces the Code Composer Studio<sup>™</sup> integrated development environment and software tools.

- Code Composer Studio Application Programming Interface Reference Guide (literature number SPRU321) describes the Code Composer Studio<sup>™</sup> application programming interface (API), which allows you to program custom plug-ins for Code Composer.

- **TMS320C6x Peripheral Support Library Programmer's Reference** (literature number SPRU273) describes the contents of the TMS320C6000<sup>™</sup> peripheral support library of functions and macros. It lists functions and macros both by header file and alphabetically, provides a complete description of each, and gives code examples to show how they are used.

- **TMS320C6000** Chip Support Library API Reference Guide (literature number SPRU401) describes a set of application programming interfaces (APIs) used to configure and control the on-chip peripherals.

### Trademarks

Code Composer Studio, C6000, C62x, C64x, C67x, TMS320C6000, TMS320C62x, TMS320C64x, TMS320C67x, and VelociTI are trademarks of Texas Instruments.

## Contents

| 1   | Overview                                                   | . 7 |

|-----|------------------------------------------------------------|-----|

| 2   | Power-Down Mode Descriptions                               | . 9 |

| 3   | Triggering, Wake-Up, and Effects                           | 11  |

| 4   | Peripheral Power-Down Mode for TMS320C6202(B)/C6203(B) DSP | 13  |

| Rev | vision History                                             | 17  |

# Figures

| 1 | Power-Down Logic                                              | . 9 |

|---|---------------------------------------------------------------|-----|

| 2 | Control Status Register (CSR)                                 | 11  |

| 3 | PWRD Field of CSR                                             | 11  |

| 4 | Power-Down Control Register (PDCTL) for C6202(B)/C6203(B) DSP | 13  |

## **Tables**

| 1 | Differences in C6000 DSP Power-Down Modes              | . 8 |

|---|--------------------------------------------------------|-----|

| 2 | Power-Down Modes                                       | 10  |

| 3 | Power-Down Mode and Wake-Up Selection                  | 11  |

| 4 | Power-Down Control Register (PDCTL) Address            | 13  |

| 5 | Power-Down Control Register (PDCTL) Field Descriptions | 14  |

| 6 | Document Revision History                              | 17  |

This document describes the power-down logic and modes used by the digital signal processors (DSPs) of the TMS320C6000<sup>™</sup> DSP family.

### 1 Overview

Most of the operating power of CMOS logic is dissipated during circuit switching from one logic state to another. By preventing some or all of the device logic from switching, the power-down modes are used to achieve significant power savings without losing any data or operation context. The three power-down modes, PD1, PD2, and PD3, available on the C6000<sup>™</sup> DSP perform this function. In addition to PD1, PD2, and PD3, the C6202(B)/C6203(B) DSP also has a peripheral power-down mode, as discussed in section 4. Table 1 summarizes the differences between the power-down modes in the C6000 devices.

| Device                | PD pin on<br>device | Power-down control<br>register (PDCTL) | PWRD field in control status register (CSR) |

|-----------------------|---------------------|----------------------------------------|---------------------------------------------|

| C6201                 | Yes                 | No                                     | Yes                                         |

| C6202/C6202(B)        | Yes                 | Yes                                    | Yes                                         |

| C6203(B)              | Yes                 | Yes                                    | Yes                                         |

| C6204                 | Yes                 | No                                     | Yes                                         |

| C6205                 | Yes                 | No                                     | Yes                                         |

| C6211/C6211(B)        | No                  | No                                     | Yes                                         |

| C6410                 | No                  | No                                     | Yes                                         |

| C6411                 | No                  | No                                     | Yes                                         |

| C6412                 | No                  | No                                     | Yes                                         |

| C6413                 | No                  | No                                     | Yes                                         |

| C6414                 | No                  | No                                     | Yes                                         |

| C6415                 | No                  | No                                     | Yes                                         |

| C6416                 | No                  | No                                     | Yes                                         |

| C6418                 | No                  | No                                     | Yes                                         |

| DM640                 | No                  | No                                     | Yes                                         |

| DM641                 | No                  | No                                     | Yes                                         |

| DM642                 | No                  | No                                     | Yes                                         |

| DM643                 | No                  | No                                     | Yes                                         |

| C6701                 | Yes                 | No                                     | Yes                                         |

| C6711/6711(B)/6711(C) | No                  | No                                     | Yes                                         |

| C6712/6712(C)         | No                  | No                                     | Yes                                         |

| C6713                 | No                  | No                                     | Yes                                         |

## Table 1. Differences in C6000 DSP Power-Down Modes

Power-Down Logic and Modes

8

## 2 Power-Down Mode Descriptions

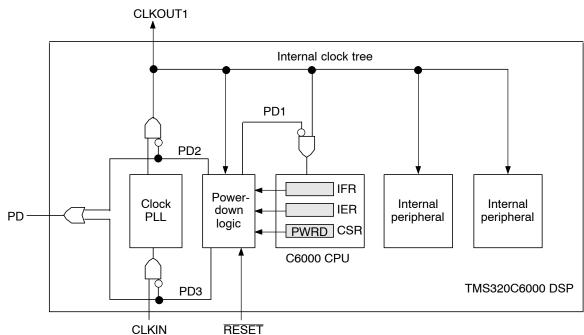

Figure 1 shows the power-down logic on a C6000 device. Power-down mode PD1 blocks the internal clock inputs at the boundary of the CPU, preventing most of its logic from switching. PD1 effectively shuts down the CPU. During PD1, DMA/EDMA transactions can proceed between peripherals and internal memory.

Additional power savings are accomplished in power-down mode PD2. During PD2, the entire on-chip clock structure (including multiple buffers) is halted at the output of the PLL (see Figure 1). Power-down mode PD3 is like PD2 but also disconnects the external clock source (CLKIN) from reaching the PLL. Wake-up from PD3 takes longer than wake-up from PD2 because the PLL needs to be re-locked, just as it does following power-up.

On the C620x/C670x DSP, both the PD2 and PD3 signals also assert the PD pin for external recognition of these two power-down modes. Although the C621x/C671x/C64x DSP has power-down modes identical to the other devices, there is no PD pin driven externally. In addition to power-down modes described in this document, the IDLE instruction provides lower CPU power consumption by executing continuous NOPs. The IDLE instruction terminates only upon servicing an interrupt. PD2 and PD3 modes are only aborted by device reset. Table 2 summarizes all the power-down modes.

Figure 1. Power-Down Logic

SPRU728C

| Power-down<br>mode | Trigger action                                      | Wake-up method                                         | Effect on device operation                                                                                                                                                                                                                                                                                                              |

|--------------------|-----------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD1                | Write 001001b or<br>010001b to bits<br>15–10 of CSR | Internal interrupt,<br>external interrupt,<br>or Reset | CPU halted (except for the interrupt logic)                                                                                                                                                                                                                                                                                             |

| PD2                | Write 011010b to<br>bits 15–10 of CSR               | Reset only                                             | Output clock from PLL is halted, stopping the internal clock structure from switching and resulting in the entire device being halted. Signal terminal PD is driven high. All register and internal RAM contents are preserved. All functional I/O "freeze" in the last state when the PLL clock is turned off. <sup>†</sup>            |

| PD3                | Write 11100b to<br>bits 15–10 of CSR                | Reset only                                             | Input clock to PLL stops generating clocks.<br>Signal terminal PD is driven high. All register<br>and internal RAM contents are preserved. All<br>functional I/O "freeze" in the last state when<br>the PLL clock is turned off. Following reset,<br>the PLL needs time to re-lock, just as it does<br>following power-up. <sup>†</sup> |

Table 2. Power-Down Modes

<sup>†</sup> When entering PD2 and PD3, all functional I/O remains in the previous state. However, for peripherals that are asynchronous in nature (HPI) or peripherals with an external clock source (McBSP, XBUS, timers, C621x/C671x/C64x EMIF, UTOPIA, PCI), output signals may transition in response to stimulus on the inputs. Peripheral operation is not assured under these conditions.

## 3 Triggering, Wake-Up, and Effects

The power-down modes and their wake-up methods are programmed by the PWRD field (bits 15–10) of the control status register (CSR) in the C6000 CPU, shown in Figure 2. The PWRD field of the CSR is shown in Figure 3 and described in Table 3. When writing to CSR, all bits of the PWRD field should be configured at the same time. A logic 0 should be used when writing to the reserved bit (bit 15) of the PWRD field. The CSR is discussed in detail in the *TMS320C6000 CPU and Instruction Set Reference Guide* (SPRU189).

### Figure 2. Control Status Register (CSR)

| 31 |        |    |     | 24 | 23 |     |   |             |   |      | 16  |

|----|--------|----|-----|----|----|-----|---|-------------|---|------|-----|

|    | CPU ID |    |     |    |    |     |   | Revision ID |   |      |     |

|    |        |    |     |    |    |     |   |             |   |      |     |

|    |        |    |     |    |    |     |   |             |   |      |     |

| 15 |        | 10 | 9   | 8  | 7  |     | 5 | 4           | 2 | 1    | 0   |

|    | PWRD   |    | SAT | EN |    | PCC |   | DCC         |   | PGIE | GIE |

#### Figure 3. PWRD Field of CSR

| 15       | 14                                      | 13                        | 12    | 11    | 10    |

|----------|-----------------------------------------|---------------------------|-------|-------|-------|

| Reserved | Enabled or nonenabled interrupt<br>wake | Enabled interrupt<br>wake | PD3   | PD2   | PD1   |

| R/W-0    | R/W-0                                   | R/W-0                     | R/W-0 | R/W-0 | R/W-0 |

**Legend:** R/W = Read/Write; -n = value after reset

Note: Refer to the TMS320C6000 CPU and Instruction Set Reference Guide (SPRU189) for other bit fields in CSR.

#### Table 3. Power-Down Mode and Wake-Up Selection

| PRWD field | Power-down mode | Wake-up method                              |

|------------|-----------------|---------------------------------------------|

| 00 0000    | No power-down   | —                                           |

| 00 1001    | PD1             | Wake by an enabled interrupt.               |

| 01 0001    | PD1             | Wake by an enabled or nonenabled interrupt. |

| 01 1010    | PD2             | Wake by a device reset.                     |

| 01 1100    | PD3             | Wake by a device reset.                     |

| other      | Reserved        | _                                           |

11

Power-down mode PD1 takes effect 8 to 9 clock cycles after the instruction that caused the power down (by setting the PWRD bits in CSR). Use the following code segment to enter power down:

|           | B NextInst<br>NOP                  | ;branch does not effect program flow, but<br>; hides the move to the CSR in the delay<br>; slots     |

|-----------|------------------------------------|------------------------------------------------------------------------------------------------------|

|           | MVC Breg, CSR<br>NOP<br>NOP<br>NOP | ;power-down mode is set by this instruction                                                          |

| NextInst: | NOP<br>NOP5<br>INSTR2              | ;CPU notifies power-down logic to initiate<br>; power down<br>;normal program execution resumed here |

The wake-up from PD1 is triggered by either an enabled interrupt or any interrupt (enabled or not enabled). The first case is selected by writing a logic 1 to bit 13 of CSR, and the second case is selected by writing a logic 1 to bit 14 of CSR. If PD1 mode is terminated by a nonenabled interrupt, the program execution returns to the instruction following the NOP 5. Wake-up by an enabled interrupt executes the corresponding interrupt service fetch packet (ISFP) first, prior to returning to the instruction following the NOP 5. The GIE bit in CSR and the NMIE bit in the interrupt enable register (IER) must also be set in order for the ISFP to execute; otherwise, execution returns to the previous point, rather than servicing the interrupt.

## 4 Peripheral Power-Down Mode for TMS320C6202(B)/C6203(B) DSP

In addition to the power-down modes common to all C6000 devices, the C6202(B)/C6203(B) DSP has the ability to turn off clocks to individual peripherals on the device using the peripheral power-down control register (PDCTL). This feature allows you to selectively turn off peripherals that are not being used for a specific application and save in power consumption for unused peripherals.

This method can have significant savings in power consumption. In a device that is as highly integrated as the C6000 DSP, a significant amount of power is consumed in a reset or no activity state just due to the internal clock distribution. By selectively turning off unused portions of the device, the effects can be minimized.

Table 4 shows the PDCTL address location. Figure 4 shows the PDCTL and Table 5 describes the fields.

You must be careful to not disable a portion of the device that is being used, since the peripheral becomes nonoperational once disabled. A clock-off mode can be entered and exited depending on the needs of the application. For example, if an application does not need the serial ports, the ports can be disabled and then reenabled when needed. While a peripheral is in power-down mode, no writes to the peripheral's registers will occur; and reads from the peripheral will produce invalid data.

### Table 4. Power-Down Control Register (PDCTL) Address

| Byte Address | Abbreviation | Description                            |

|--------------|--------------|----------------------------------------|

| 019C 0200h   | PDCTL        | Peripheral power-down control register |

## Figure 4. Power-Down Control Register (PDCTL) for C6202(B)/C6203(B) DSP

| 31 | 1        |   |          |        |        |       |       |

|----|----------|---|----------|--------|--------|-------|-------|

|    |          |   | Reserved |        |        |       |       |

|    |          |   | R-0      |        |        |       |       |

| 15 |          | 5 | 4        | 3      | 2      | 1     | 0     |

|    | Reserved |   | MCBSP2   | MCBSP1 | MCBSP0 | EMIF  | DMA   |

|    | R-0      |   | R/W-0    | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

**Legend:** R = Read only; R/W = Read/Write; -n = value after reset

SPRU728C

Power-Down Logic and Modes

13

| Bit  | field†   | symval†   | Value | Description                                                                                           |

|------|----------|-----------|-------|-------------------------------------------------------------------------------------------------------|

| 31–5 | Reserved | _         | 0     | Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. |

| 4    | MCBSP2   | OF(value) |       | Internal McBSP2 clock enable bit.                                                                     |

|      |          | DEFAULT   | 0     | Internal McBSP2 clock is enabled.                                                                     |

|      |          | CLKON     |       |                                                                                                       |

|      |          | CLKOFF    | 1     | Internal McBSP2 clock is disabled. McBSP2 is not functional.                                          |

| 3    | MCBSP1   | OF(value) |       | Internal McBSP1 clock enable bit.                                                                     |

|      |          | DEFAULT   | 0     | Internal McBSP1 clock is enabled.                                                                     |

|      |          | CLKON     |       |                                                                                                       |

|      |          | CLKOFF    | 1     | Internal McBSP1 clock is disabled. McBSP1 is not functional.                                          |

| 2    | MCBSP0   | OF(value) |       | Internal McBSP0 clock enable bit.                                                                     |

|      |          | DEFAULT   | 0     | Internal McBSP0 clock is enabled.                                                                     |

|      |          | CLKON     |       |                                                                                                       |

|      |          | CLKOFF    | 1     | Internal McBSP0 clock is disabled. McBSP1 is not functional.                                          |

| 1    | EMIF     | OF(value) |       | Internal EMIF clock enable bit.                                                                       |

|      |          | DEFAULT   | 0     | Internal EMIF clock is enabled.                                                                       |

|      |          | CLKON     |       |                                                                                                       |

|      |          | CLKOFF    | 1     | Internal EMIF clock is disabled. EMIF is not functional.                                              |

| 0    | DMA      | OF(value) |       | Internal DMA clock enable bit.                                                                        |

|      |          | DEFAULT   | 0     | Internal DMA clock is enabled.                                                                        |

|      |          | CLKON     |       |                                                                                                       |

|      |          | CLKOFF    | 1     | Internal DMA clock is disabled. DMA is not functional.                                                |

Table 5. Power-Down Control Register (PDCTL) Field Descriptions

<sup>†</sup> For CSL implementation, use the notation PWR\_PDCTL\_field\_symval

When reenabling any of the PDCTL bits, the CPU should wait at least 5 additional clock cycles before attempting to access that peripheral. This delay can be accomplished with a NOP 5 instruction after any write to PDCTL, as shown in Example 1.

Example 1. Assemble Code for Initializing Peripheral Power-Down Control Register

| MVK  | 0x019C0200, | Dest_Ptr_Reg  |

|------|-------------|---------------|

| MVKH | 0x019C0200, | Dest_Ptr_Reg  |

| STW  | SrcReg,     | *Dest_Ptr_Reg |

| NOP  | 5           |               |

This page is intentionally left blank.

# **Revision History**

Table 6 lists the changes made since the previous version of this document.

Table 6. Document Revision History

| Page | Additions/Modifications/Deletions |  |  |  |

|------|-----------------------------------|--|--|--|

| 8    | Updated Table 1 to include DM643. |  |  |  |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated