# TMS320C64x+ DSP Cache

# **User's Guide**

Literature Number: SPRU862B February 2009

# **Contents**

| Prefa | ICE                                                            | . 7 |

|-------|----------------------------------------------------------------|-----|

| 1     | Introduction                                                   | . 9 |

| 1.1   | Purpose of This User's Guide                                   | 10  |

| 1.2   | Chip Support Library (CSL)                                     | 10  |

| 1.3   | Cache Terms and Definitions                                    | 10  |

| 1.4   | Cache Differences Between C64x and C64x+ DSP                   | 14  |

| 1.5   | Why Use Cache                                                  | 15  |

| 1.6   | Principle of Locality                                          | 16  |

| 1.7   | Cache Memory Architecture Overview                             | 17  |

| 1.8   | Cache Basics                                                   | 18  |

|       | 1.8.1 Direct-Mapped Caches                                     | 18  |

|       | 1.8.2 Types of Cache Misses                                    | 20  |

|       | 1.8.3 Set-Associative Caches                                   |     |

|       | 1.8.4 Level 2 (L2) Cache                                       | 22  |

|       | 1.8.5 Cacheability of External Memory Addresses                | 23  |

| 2     | Using Cache                                                    | 25  |

| 2.1   | Configuring L1 Caches                                          | 26  |

| 2.2   | Configuring L2 Cache                                           | 26  |

| 2.3   | Cacheability                                                   | 26  |

| 2.4   | Coherence                                                      | 28  |

|       | 2.4.1 Snoop Coherence Protocol                                 | 29  |

|       | 2.4.2 Cache Coherence Protocol for DMA Accesses to L2 SRAM     | 30  |

|       | 2.4.3 Usage Guidelines for L2 Cache Coherence Operations       | 36  |

|       | 2.4.4 Usage Guidelines for L1 Cache Coherence Operations       | 38  |

| 2.5   | On-Chip Debug Support                                          | 39  |

| 2.6   | Self-Modifying Code and L1P Coherence                          | 39  |

| 2.7   | Changing Cache Configuration During Run-Time                   | 39  |

|       | 2.7.1 Disabling External Memory Caching                        | 40  |

|       | 2.7.2 Changing Cache Sizes During Run-Time                     | 40  |

| 3     | Optimizing for Cache Performance                               | 45  |

| 3.1   | Differences Between C64x+ and C64x DSP                         | 46  |

| 3.2   | Cache Performance Characteristics                              | 46  |

|       | 3.2.1 Stall Conditions                                         | 46  |

|       | 3.2.2 C64x+ Pipelining of L1D Read Misses                      | 50  |

|       | 3.2.3 Optimization Techniques Overview                         | 52  |

| 3.3   | Application-Level Optimizations                                | 53  |

|       | 3.3.1 Streaming to External Memory or L1/L2 SRAM               | 53  |

|       | 3.3.2 Using L1 SRAM                                            | 53  |

|       | 3.3.3 Signal Processing versus General-Purpose Processing Code | 54  |

| 3.4   | Procedural-Level Optimizations                                 | 54  |

| С   | Revision History                                                             | <b>79</b> |

|-----|------------------------------------------------------------------------------|-----------|

| B.1 | Eliminating False Addresses                                                  | 78        |

| В   | C64x+ DSP Cache Coherence                                                    |           |

| Α   | Cache Differences Between C64x+ DSP and C64x DSP                             | <b>71</b> |

| 3.5 | On-Chip Debug Support                                                        | 70        |

|     | 3.4.7 Avoiding Write Buffer Related Stalls                                   | 66        |

|     | 3.4.6 Avoiding Capacity Misses                                               | 64        |

|     | 3.4.5 Avoiding L1D Thrashing                                                 | 62        |

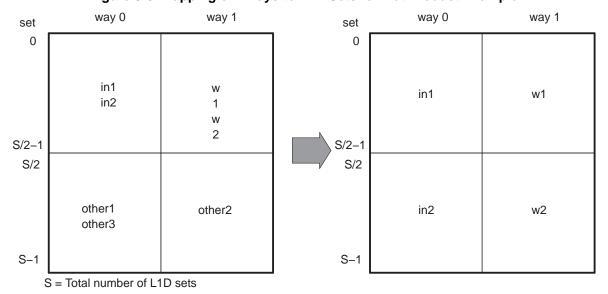

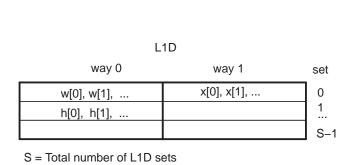

|     | 3.4.4 Avoiding L1D Conflict Misses                                           | 60        |

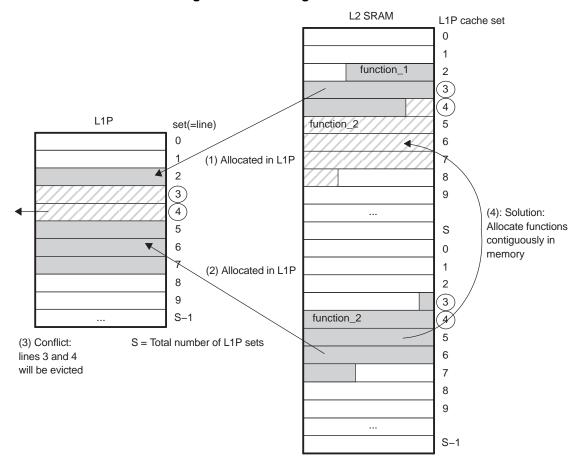

|     | 3.4.3 Avoiding L1P Conflict Misses                                           | 56        |

|     | 3.4.2 Processing Chains                                                      | 55        |

|     | 3.4.1 Reduce Memory Bandwidth Requirements by Choosing Appropriate Data Type | 55        |

# List of Figures

| 1-1 | Flat Versus Hierarchical Memory Architecture                       | 15 |

|-----|--------------------------------------------------------------------|----|

| 1-2 | Access Pattern of a 6-Tap FIR Filter                               | 16 |

| 1-3 | C64x+ Cache Memory Architecture                                    | 17 |

| 1-4 | C64x+ L1P Cache Architecture (16K Bytes)                           | 19 |

| 1-5 | Memory Address from Cache Controller (For 16K Byte Cache Size)     | 19 |

| 1-6 | C64x+ L1D Cache Architecture (16K Bytes)                           | 21 |

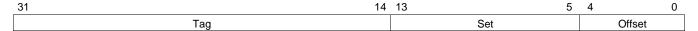

| 2-1 | C64x+ L2 Memory Configurations                                     | 27 |

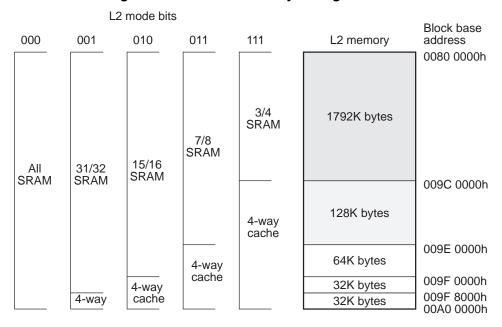

| 2-2 | Cache Coherence Problem                                            | 28 |

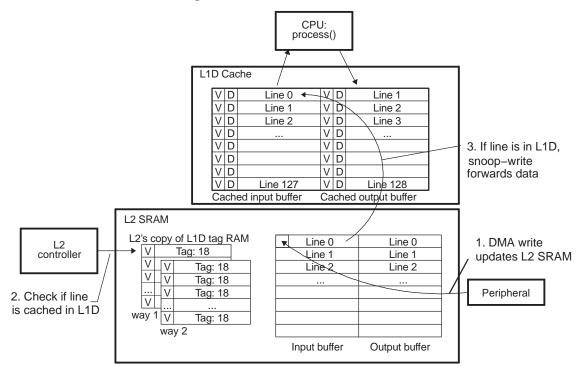

| 2-3 | DMA Write to L2 SRAM                                               | 30 |

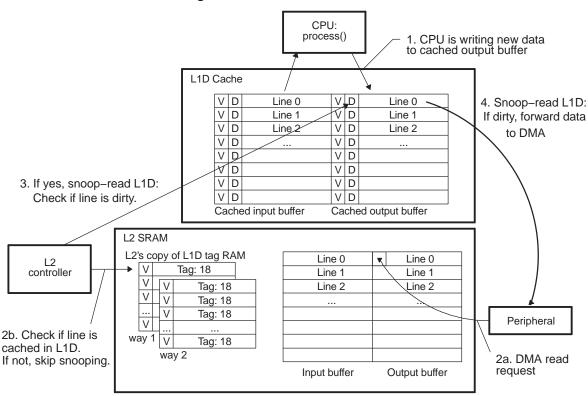

| 2-4 | DMA Read of L2 SRAM                                                | 31 |

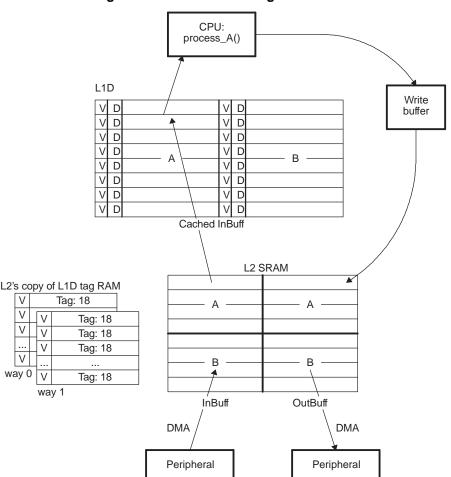

| 2-5 | Double Buffering in L2 SRAM                                        | 32 |

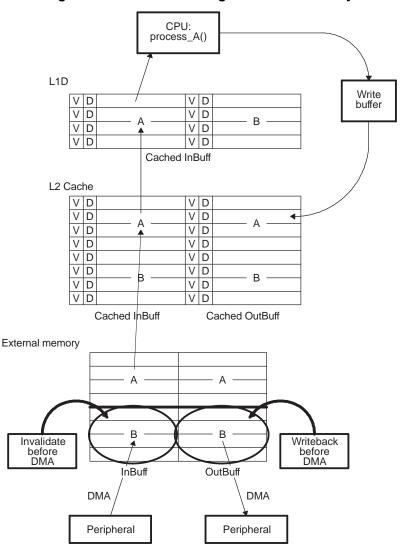

| 2-6 | Double Buffering in External Memory                                |    |

| 2-7 | Changing L2 Cache Size During Run-Time                             | 40 |

| 3-1 | C64x+ Cache Memory Architecture                                    | 48 |

| 3-2 | Memory Access Pattern of Touch Loop                                | 50 |

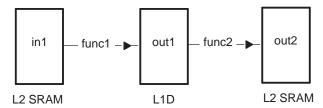

| 3-3 | Processing Chain With 2 Functions                                  | 55 |

| 3-4 | Memory Layout for Channel FIR/Dot Product Processing Chain Routine | 56 |

| 3-5 | Avoiding L1P Evictions                                             |    |

| 3-6 | Mapping of Arrays to L1D Sets for Dot Product Example              | 61 |

| 3-7 | Memory Layout and Contents of L1D After the First Two Iterations   | 64 |

| 3-8 | Memory Layout for Dotprod Example                                  | 65 |

| 3-9 | Memory Layout for Vecaddc/Dotprod Example                          | 68 |

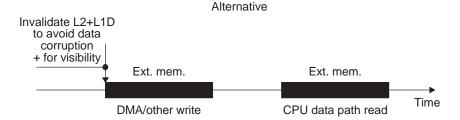

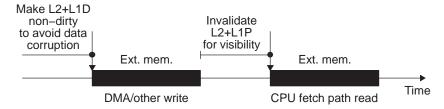

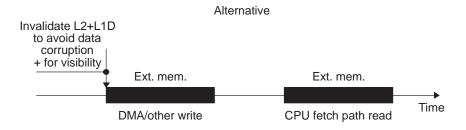

| B-1 | External Memory: DMA Write, CPU Read (Data)                        | 76 |

| B-2 | External Memory: DMA Write, CPU Read (Code)                        | 76 |

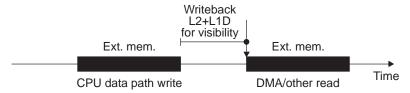

| B-3 | External Memory: CPU Write, DMA Read (Data)                        | 76 |

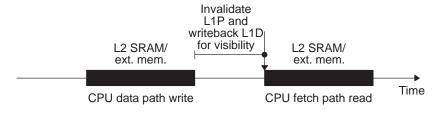

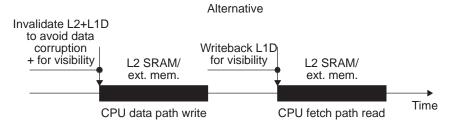

| B-4 | L2 SRAM/External Memory: CPU Write (Data), CPU Read (Code)         | 77 |

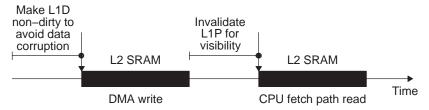

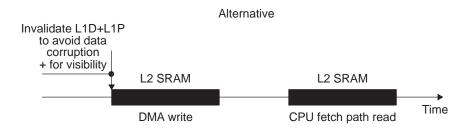

| R-5 | L2 SRAM: DMA Write CPU Read (Code)                                 | 77 |

## **List of Tables**

| 1-1 | Cache Terms and Definitions                                                                    | 10 |

|-----|------------------------------------------------------------------------------------------------|----|

| 1-2 | L1P Cache Characteristics                                                                      | 18 |

| 1-3 | L1P Miss Stall Characteristics                                                                 | 18 |

| 1-4 | L1D Cache Characteristics                                                                      | 20 |

| 1-5 | L1D Miss Stall Characteristics                                                                 | 21 |

| 1-6 | L2 Cache Characteristics                                                                       | 23 |

| 2-1 | L2 Cache Coherence Operations                                                                  | 36 |

| 2-2 | Scenarios and Required L2 Coherence Operations on External Memory                              | 37 |

| 2-3 | L1D Cache Coherence Operations                                                                 | 38 |

| 2-4 | L1P Cache Coherence Operations                                                                 | 38 |

| 2-5 | Scenarios and Required L1 Coherence Operations                                                 | 38 |

| 2-6 | Procedure for Changing Cache Sizes for L1P, L1D, and L2                                        | 41 |

| 3-1 | L1P Miss Pipelining Performance (Average Number of Stalls per Execute Packet)                  | 49 |

| 3-2 | L1D Performance Parameters (Number of Stalls)                                                  | 49 |

| 3-3 | Contents of an L1D Set at the Time When an Array is Accessed (Weighted Dot Product Example)    | 63 |

| 3-4 | Interaction of Read Miss and Write Buffer Activity for the First Call of Vecaddc (n = 0 to 62) | 69 |

| A-1 | Cache Differences Between C64x+ DSP and C64x DSP                                               | 71 |

| B-1 | Coherence Matrix for L2 SRAM Addresses                                                         | 73 |

| B-2 | Coherence Matrix for an External Memory Address                                                | 74 |

| C-1 | Document Revision History                                                                      | 79 |

### Read This First

#### **About This Manual**

This document describes how the cache-based memory system of the TMS320C64x+™ digital signal processor (DSP) can be efficiently used in DSP applications. The internal memory architecture of these devices is organized in a two-level hierarchy consisting of a dedicated program memory (L1P) and a dedicated data memory (L1D) on the first level. Accesses by the CPU to the these first level memories can complete without CPU pipeline stalls. Both L1P and L1D can be configured into SRAM and cache. If the data requested by the CPU is not contained in cache, it is fetched from the next lower memory level, L2 or external memory. A detailed technical description of the C64x+™ memory architecture is given in *TMS320C64x+ DSP Megamodule Reference Guide* (SPRU871).

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the C6000 devices and related support tools. Copies of these documents are available on the Internet at <a href="www.ti.com">www.ti.com</a>. Tip: Enter the literature number in the search box provided at <a href="www.ti.com">www.ti.com</a>.

The current documentation that describes the C6000 devices, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <a href="www.ti.com/c6000">www.ti.com/c6000</a>.

- SPRU732 TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

- <u>SPRU871</u> *TMS320C64x+ DSP Megamodule Reference Guide.* Describes the TMS320C64x+ digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

- SPRAA84 TMS320C64x to TMS320C64x+ CPU Migration Guide. Describes migrating from the Texas Instruments TMS320C64x digital signal processor (DSP) to the TMS320C64x+ DSP. The objective of this document is to indicate differences between the two cores. Functionality in the devices that is identical is not included.

#### **Trademarks**

TMS320C64x+, C64x+, TMS320C64x+, C64x+, Code Composer Studio, TMS320C64x are trademarks of Texas Instruments.

# Introduction

This chapter discusses the basic operation of memory caches and describes the operation of the TMS320C64x+ $^{TM}$  digital signal processor (DSP) two-level cache architecture.

| Topic |                                              | Page |

|-------|----------------------------------------------|------|

|       |                                              |      |

| 1.1   | Purpose of This User's Guide                 | 10   |

| 1.2   | Chip Support Library (CSL)                   | 10   |

| 1.3   | Cache Terms and Definitions                  | 10   |

| 1.4   | Cache Differences Between C64x and C64x+ DSP | 14   |

| 1.5   | Why Use Cache                                | 15   |

| 1.6   | Principle of Locality                        | 16   |

| 1.7   | Cache Memory Architecture Overview           | 17   |

| 1.8   | Cache Basics                                 | 18   |

|       |                                              |      |

#### 1.1 Purpose of This User's Guide

This user's guide describes how the cache-based memory system of the C64x+™ DSP can be efficiently used in DSP applications. The internal memory architecture of these devices is organized in a two-level hierarchy consisting of a dedicated program memory (L1P) and a dedicated data memory (L1D) on the first level. Accesses by the CPU to the these first level memories can complete without CPU pipeline stalls. Both L1P and L1D can be configured into SRAM and cache. If the data requested by the CPU is not contained in cache, it is fetched from the next lower memory level, L2 or external memory. A detailed technical description of the C64x+ memory architecture is given in *TMS320C64x+ DSP Megamodule Reference Guide* (SPRU871).

The following topics are covered in this user's guide:

- The necessity of caches in high-performance DSPs (Chapter 1)

- General introduction into cache-based architectures (Chapter 1)

- Configuring and using the cache on C64x+ devices (Chapter 2)

- Maintaining cache coherence between different requestors (Chapter 2 and Appendix B)

- Linking code and data for increased cache efficiency (Chapter 3)

- Code-optimization techniques for increased cache efficiency (Chapter 3)

#### 1.2 Chip Support Library (CSL)

This user's guide makes references to the Chip Support Library (CSL). The CSL provides APIs for easy control of cache, DMA and peripheral functions of a device. The CSL for your device either comes with the Code Composer Studio<sup>™</sup> integrated development environment (IDE) or may be downloaded from www.ti.com. Note that cache APIs are also available through BIOS (version 5.21 or higher).

#### 1.3 Cache Terms and Definitions

Table 1-1 lists the terms used throughout this document that relate to the operation of the C64x+ DSP two-level cache.

Table 1-1. Cache Terms and Definitions

| Term                | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Allocation          | The process of finding a location in the cache to store newly cached data. This process can include evicting data that is presently in the cache to make room for the new data.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Associativity       | The number of line frames in each set. This is specified as the number of ways in the cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Capacity miss       | A cache <i>miss</i> that occurs because the cache does not have sufficient room to hold the entire <i>working</i> set for a program. Compare with <i>compulsory miss</i> and <i>conflict miss</i> .                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Clean               | A cache <i>line</i> that is <i>valid</i> and that has not been written to by upper levels of memory or the CPU. The opposite state for a clean cache line is <i>dirty</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Coherence           | Informally, a memory system is coherent if any read of a data item returns the most recently written value of that data item. This includes accesses by the CPU and the DMA.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Compulsory miss     | Sometimes referred to as a <i>first-reference miss</i> . A compulsory miss is a cache <i>miss</i> that must occur because the data has had no prior opportunity to be allocated in the cache. Typically, compulsory misses for particular pieces of data occur on the first access of that data. However, some cases can be considered compulsory even if they are not the first reference to the data. Such cases include repeated write misses on the same location in a cache that does not <i>write allocate</i> , and cache misses to noncacheable locations. Compare with <i>capacity miss</i> and <i>conflict miss</i> . |

| Conflict miss       | A cache <i>miss</i> that occurs due to the limited <i>associativity</i> of a cache, rather than due to capacity constraints. A <i>fully-associative cache</i> is able to allocate a newly cached <i>line</i> of data anywhere in the cache. Most caches have much more limited associativity (see <i>set-associative cache</i> ), and so are restricted in where they may place data. This results in additional cache misses that a more flexible cache would not experience.                                                                                                                                                  |

| Direct-mapped cache | A direct-mapped cache maps each address in the <i>lower-level memory</i> to a single location in the cache. Multiple locations may map to the same location in the cache. This is in contrast to a multi-way <i>set-associative cache</i> , which selects a place for the data from a set of locations in the cache. A direct-mapped cache can be considered a single-way set-associative cache.                                                                                                                                                                                                                                |

Table 1-1. Cache Terms and Definitions (continued)

| Term                                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Dirty                                | In a <i>writeback cache</i> , writes that reach a given level in the memory hierarchy may update that level, but not the levels below it. Therefore, when a cache <i>line</i> is <i>valid</i> and contains updates that have not been sent to the next lower level, that line is said to be dirty. The opposite state for a dirty cache line is <i>clean</i> .                                                                                                                                                                                                                                                                                                                              |  |

| DMA                                  | irect Memory Access. Typically, a DMA operation copies a block of memory from one range of ddresses to another, or transfers data between a peripheral and memory. From a cache <i>coherence</i> andpoint, DMA accesses can be considered accesses by a parallel processor.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Eviction                             | The process of removing a <i>line</i> from the cache to make room for newly cached data. Eviction can also occur under user control by requesting a <i>writeback-invalidate</i> for an address or range of addresses from the cache. The evicted line is referred to as the <i>victim</i> . When a victim line is <i>dirty</i> (that is, it contains updated data), the data must be written out to the next level memory to maintain <i>coherency</i> .                                                                                                                                                                                                                                    |  |

| Execute packet                       | A block of instructions that begin execution in parallel in a single cycle. An execute packet may contain between 1 and 8 instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Fetch packet                         | A block of 8 instructions that are fetched in a single cycle. One fetch packet may contain multiple execute packets, and thus may be consumed over multiple cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| First-reference miss                 | A cache <i>miss</i> that occurs on the first reference to a piece of data. First-reference misses are a form of <i>compulsory miss</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Fully-associative cache              | A cache that allows any memory address to be stored at any location within the cache. Such caches are very flexible, but usually not practical to build in hardware. They contrast sharply with direct-mapped caches and set-associative caches, both of which have much more restrictive allocation policies. Conceptually, fully-associative caches are useful for distinguishing between conflict misses and capacity misses when analyzing the performance of a direct-mapped or set-associative cache. In terms of set-associative caches, a fully-associative cache is equivalent to a set-associative cache that has as many ways as it does line frames, and that has only one set. |  |

| Higher-level memory                  | In a hierarchical memory system, higher-level memories are memories that are closer to the CPU. The highest level in the memory hierarchy is usually the Level 1 caches. The memories at this level exist directly next to the CPU. Higher-level memories typically act as caches for data from <i>lower-level memory</i> .                                                                                                                                                                                                                                                                                                                                                                 |  |

| Hit                                  | A cache hit occurs when the data for a requested memory location is present in the cache. The opposite of a hit is a <i>miss</i> . A cache hit minimizes stalling, since the data can be fetched from the cach much faster than from the source memory. The determination of hit versus miss is made on each level of the memory hierarchy separately-a miss in one level may hit in a lower level.                                                                                                                                                                                                                                                                                         |  |

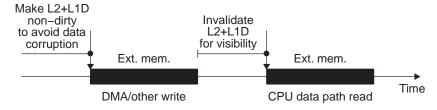

| Invalidate                           | The process of marking <i>valid</i> cache <i>lines</i> as invalid in a particular cache. Alone, this action discards contents of the affected cache lines, and does not write back any updated data. When combined with <i>writeback</i> , this effectively updates the next lower level of memory that holds the data, while complete removing the cached data from the given level of memory. Invalidates combined with writebacks are referred to as <i>writeback-invalidates</i> , and are commonly used for retaining <i>coherence</i> between cache                                                                                                                                   |  |

| Least Recently Used (LRU) allocation | For set-associative and <i>fully-associative caches</i> , least-recently used <i>allocation</i> refers to the method used to choose among <i>line frames</i> in a set when allocating space in the cache. When all of the <i>line frames</i> in the <i>set</i> that the address maps to contain <i>valid data</i> , the line frame in the set that was read or written the least recently (furthest back in time) is selected to hold the newly cached data. The selected line frame is then <i>evicted</i> to make room for the new data.                                                                                                                                                  |  |

| Line                                 | A cache line is the smallest block of data that the cache operates on. The cache line is typically much larger than the size of data accesses from the CPU or the next higher level of memory. For instance, although the CPU may request single bytes from memory, on a read <i>miss</i> the cache reads an entire line's worth of data to satisfy the request.                                                                                                                                                                                                                                                                                                                            |  |

| Line frame                           | A location in a cache that holds cached data (one <i>line</i> ), an associated <i>tag</i> address, and status information for the line. The status information can include whether the line is <i>valid</i> , <i>dirty</i> , and the current state of that line's <i>LRU</i> .                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Line size                            | The size of a single cache <i>line</i> , in bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Load through                         | When a CPU request misses both the first-level and second-level caches, the data is fetched from the external memory and stored to both the first-level and second-level cache simultaneously. A cache that stores data and sends that data to the upper-level cache at the same time is a load-through cache. Using a load-through cache reduces the stall time compared to a cache that first stores the data in a lower level and then sends it to the higher-level cache as a second step.                                                                                                                                                                                              |  |

| Long-distance access                 | Accesses made by the CPU to a noncacheable memory. Long-distance accesses are used when accessing external memory that is not marked as cacheable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Lower-level memory                   | In a hierarchical memory system, lower-level memories are memories that are further from the CPU. In a C64x+ DSP system, the lowest level in the hierarchy includes the system memory below L2 and any memory-mapped peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

### Table 1-1. Cache Terms and Definitions (continued)

| Term                  | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LRU                   | Least Recently Used. See <i>least recently used allocation</i> for a description of the LRU replacement policy. When used alone, LRU usually refers to the status information that the cache maintains for identifying the least-recently used <i>line</i> in a set. For example, consider the phrase "accessing a cache line updates the LRU for that line."                                                                                                                                                                                                                                                                                                                             |

| Memory ordering       | Defines what order the effects of memory operations are made visible in memory. (This is sometimes referred to as consistency.) Strong memory ordering at a given level in the memory hierarchy indicates it is not possible to observe the effects of memory accesses in that level of memory in an order different than program order. Relaxed memory ordering allows the memory hierarchy to make the effects of memory operations visible in a different order. Note that strong ordering does not require that the memory system execute memory operations in program order, only that it makes their effects visible to other requestors in an order consistent with program order. |

| Miss                  | A cache miss occurs when the data for a requested memory location is not in the cache. A miss may stall the requestor while the <i>line frame</i> is allocated and data is fetched from the next lower level of memory. In some cases, such as a CPU write miss from L1D, it is not strictly necessary to stall the CPU. Cache misses are often divided into three categories: <i>compulsory misses</i> , <i>conflict misses</i> , and <i>capacity misses</i> .                                                                                                                                                                                                                           |

| Miss pipelining       | The process of servicing a single cache miss is pipelined over several cycles. By pipelining the miss, it is possible to overlap the processing of several misses, should many occur back-to-back. The net result is that much of the overhead for the subsequent misses is hidden, and the incremental stall penalty for the additional misses is much smaller than that for a single miss taken in isolation.                                                                                                                                                                                                                                                                           |

| Read allocate         | A read-allocate cache only allocates space in the cache on a read <i>miss</i> . A write miss does not cause an allocation to occur unless the cache is also a <i>write-allocate cache</i> . For caches that do not write allocate, the write data would be passed on to the next lower-level cache.                                                                                                                                                                                                                                                                                                                                                                                       |

| Set                   | A collection of <i>line frames</i> in a cache that a single address can potentially reside. A <i>direct-mapped</i> cache contains one line frame per set, and an N-way set-associative cache contains N line frames per set. A <i>fully-associative cache</i> has only one set that contains all of the line frames in the cache.                                                                                                                                                                                                                                                                                                                                                         |

| Set-associative cache | A set-associative cache contains multiple <i>line frames</i> that each <i>lower-level memory</i> location can be held in. When allocating room for a new <i>line</i> of data, the selection is made based on the <i>allocation</i> policy for the cache. The C64x+ devices employ a <i>least recently used allocation</i> policy for its set-associative caches.                                                                                                                                                                                                                                                                                                                          |

| Snoop                 | A method by which a <i>lower-level memory</i> queries a <i>higher-level memory</i> to determine if the higher-level memory contains data for a given address. The primary purpose of snoops is to retain coherency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Tag                   | A storage element containing the most-significant bits of the address stored in a particular <i>line</i> . Tag addresses are stored in special tag memories that are not directly visible to the CPU. The cache queries the tag memories on each access to determine if the access is a <i>hit</i> or a <i>miss</i> .                                                                                                                                                                                                                                                                                                                                                                     |

| Thrash                | An algorithm is said to thrash the cache when its access pattern causes the performance of the cache to suffer dramatically. Thrashing can occur for multiple reasons. One possible situation is that the algorithm is accessing too much data or program code in a short time frame with little or no reuse. That is, its working set is too large, and thus the algorithm is causing a significant number of capacity misses. Another situation is that the algorithm is repeatedly accessing a small group of different addresses that all map to the same set in the cache, thus causing an artificially high number of conflict misses.                                              |

| Touch                 | A memory operation on a given address is said to touch that address. Touch can also refer to reading array elements or other ranges of memory addresses for the sole purpose of allocating them in a particular level of the cache. A CPU-centric loop used for touching a range of memory in order to allocate it into the cache is often referred to as a touch loop. Touching an array is a form of software-controlled prefetch for data.                                                                                                                                                                                                                                             |

| Valid                 | When a cache <i>line</i> holds data that has been fetched from the next level memory, that <i>line frame</i> is valid. The invalid state occurs when the line frame holds no data, either because nothing has been cached yet, or because previously cached data has been <i>invalidated</i> for whatever reason ( <i>coherence</i> protocol, program request, etc.). The valid state makes no implications as to whether the data has been modified since it was fetched from the <i>lower-level memory</i> ; rather, this is indicated by the <i>dirty</i> or <i>clean</i> state of the line.                                                                                           |

| Victim                | When space is allocated in a set for a new <i>line</i> , and all of the <i>line frames</i> in the set that the address maps to contain valid data, the cache controller must select one of the <i>valid</i> lines to evict in order to make room for the new data. Typically, the <i>least-recently used</i> (LRU) line is selected. The line that is <i>evicted</i> is known as the victim line. If the victim line is dirty, its contents are written to the next lower level of memory using a <i>victim writeback</i> .                                                                                                                                                               |

| Victim Buffer         | A special buffer that holds <i>victims</i> until they are <i>written</i> back. Victim <i>lines</i> are moved to the victim buffer to make room in the cache for incoming data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 1-1. Cache Terms and Definitions (continued)

| Term                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Victim Writeback     | When a <i>dirty</i> line is <i>evicted</i> (that is, a line with updated data is evicted), the updated data is written to the lower levels of memory. This process is referred to as a victim writeback.                                                                                                                                                                                                                                                                                                                                                                                                            |

| Way                  | In a set-associative cache, each set in the cache contains multiple line frames. The number of line frames in each set is referred to as the number of ways in the cache. The collection of corresponding line frames across all sets in the cache is called a way in the cache. For instance, a 4-way set-associative cache has 4 ways, and each set in the cache has 4 line frames associated with it, one associated with each of the 4 ways. As a result, any given cacheable address in the memory map has 4 possible locations it can map to in a 4-way set-associative cache.                                |

| Working set          | The working set for a program or algorithm is the total set of data and program code that is referenced within a particular period of time. It is often useful to consider the working set on an algorithm-by-algorithm basis when analyzing upper levels of memory, and on a whole-program basis when analyzing lower levels of memory.                                                                                                                                                                                                                                                                            |

| Write allocate       | A write-allocate cache allocates space in the cache when a write miss occurs. Space is allocated according to the cache's <i>allocation</i> policy ( <i>LRU</i> , for example), and the data for the <i>line</i> is read into the cache from the next lower level of memory. Once the data is present in the cache, the write is processed. For a <i>writeback cache</i> , only the current level of memory is updated-the write data is not immediately passed to the next level of memory.                                                                                                                        |

| Writeback            | The process of writing updated data from a <i>valid</i> but <i>dirty</i> cache <i>line</i> to a <i>lower-level memory</i> . After the writeback occurs, the cache line is considered <i>clean</i> . Unless paired with an <i>invalidate</i> (as in <i>writeback-invalidate</i> ), the line remains valid after a writeback.                                                                                                                                                                                                                                                                                         |

| Writeback cache      | A writeback cache will only modify its own data on a write hit. It will not immediately send the update to the next lower-level of memory. The data will be written back at some future point, such as when the cache line is evicted, or when the lower-level memory snoops the address from the higher-level memory. It is also possible to directly initiate a writeback for a range of addresses using cache control registers. A write hit to a writeback cache causes the corresponding line to be marked as dirty-that is, the line contains updates that have yet to be sent to the lower levels of memory. |

| Writeback-invalidate | A writeback operation followed by an invalidation. See <i>writeback</i> and <i>invalidate</i> . On the C64x+ devices, a writeback-invalidate on a group of cache <i>lines</i> only writes out data for <i>dirty</i> cache lines, but invalidates the contents of all of the affected cache lines.                                                                                                                                                                                                                                                                                                                   |

| Write merging        | Write merging combines multiple independent writes into a single, larger write. This improves the performance of the memory system by reducing the number of individual memory accesses it needs to process. For instance, on the C64x+ device, the L1D write buffer can merge multiple writes under some circumstances if they are to the same double-word address. In this example, the result is a larger effective write-buffer capacity and a lower bandwidth impact on L2.                                                                                                                                    |

| Write-through cache  | A write-through cache passes all writes to the <i>lower-level memory</i> . It never contains updated data that it has not passed on to the lower-level memory. As a result, cache <i>lines</i> can never be <i>dirty</i> in a write-through cache. The C64x+ devices do not utilize write-through caches.                                                                                                                                                                                                                                                                                                           |

#### 1.4 Cache Differences Between C64x and C64x+ DSP

Readers who are familiar with the TMS320C64x<sup>™</sup> DSP cache architecture may want to take note of features that are new or have changed for C64x+ DSPs. The features discussed in this chapter are listed below. For a complete list of new and changed features, see Appendix A.

#### Memory sizes and types:

- On C64x+ devices, each L1D and L1P implement SRAM additionally to cache. The size of cache is

user-configurable and can be set to 4K, 8K, 16K, or 32K bytes. The amount of available SRAM is

device dependent and specified in the device-specific data manual. On C64x devices, only cache with

a fixed size of 16K bytes is implemented.

- On C64x+ devices, the maximum possible size of L2 is increased. See the data manual for the actual amount of available L2 memory. L2 cache size configurations are the same as on C64x devices.

#### Write buffer:

• The width of the write buffer on C64x+ devices is increased to 128 bits; on C64x devices, the width is 64 bits.

#### Cacheability:

- The cacheability settings of external memory addresses (through the MAR bits) only affect L1D and L2 caches on C64x+ devices; that is, program fetches to external memory addresses are always cached in L1P, regardless of the cacheability setting. This is not the case on C64x devices, where the settings affects all caches, L1P, L1D, and L2.

- The cacheability control of external memory addresses covers the entire external address space on C64x+ devices. In contrast, on C64x devices, only a subset of the address space is covered.

#### Snooping protocol:

- The snooping cache coherence protocol on C64x+ devices directly forwards data to L1D cache and the DMA. C64x devices invalid and writeback cache lines to maintain coherence. The C64x+ snooping mechanism is more efficient since it eliminates cache miss overhead caused by invalidates.

- The snoop coherence protocol on C64x+ devices does not maintain coherence between L1P cache and L2 SRAM, as is the case on C64x devices. This is the responsibility of the programmer.

#### Cache coherence operations:

- On C64x+ devices, the L2 cache coherence operations always operate on L1P and L1D even if L2 cache is disabled. This is not the case on C64x devices, which requires the explicit use of L1 coherence operations.

- C64x+ devices support a complete set of range and global L1D cache coherence operations. In contrast, C64x devices support only L1D range invalidate and writeback-invalidate.

- On cache size changes, C64x+ devices automatically writeback—invalidate cache before initializing it with the new size. In contrast, C64x devices required an explicit writeback—invalidate to be issued by the programmer (however, this is handled as part of the CSL function).

- On C64x+ devices, L2 cache is noninclusive of L1D and L1P. This means that a line eviction from L2 does not cause the corresponding lines in L1P and L1D to be evicted. However, this is the case on C64x devices. The advantage of noninclusivity is that line allocations in L2 due to program fetches do not evict data from L1D cache, and line allocations in L2 due to data accesses do not evict program code from L1P. This helps reduce the number of cache misses.

www.ti.com Why Use Cache

#### 1.5 Why Use Cache

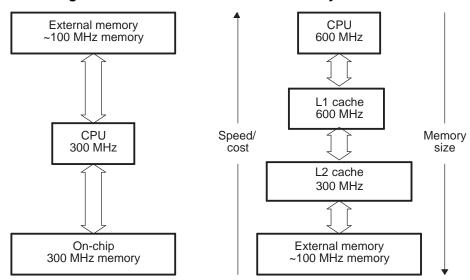

From a DSP application perspective, a large amount of fast on-chip memory would be ideal. However, over the past years the performance of processors has improved at a much faster pace than that of memory. As a result, there is now a performance gap between CPU and memory speed. High-speed memory is available but consumes much more size and is more expensive compared with slower memory.

Consider the flat memory architecture shown on the left in Figure 1-1. Both CPU and internal memory are clocked at 300 MHz such that no memory stalls occur. However for accesses to the slower external memory, there will be CPU stalls. If the CPU clock was now increased to 600 MHz, the internal memory could only service CPU accesses every two CPU cycles and the CPU would stall for one cycle on every memory access. The penalty would be particularly large for highly optimized inner loops that may access memory on every cycle. In this case, the effective CPU processing speed would approach the slower memory speed. Unfortunately, today's available memory technology is not able to keep up with increasing processor speeds, and a same size internal memory running at the same CPU speed would be far too expensive.

The solution is to use a memory hierarchy, as shown on the right in Figure 1-1. A fast but small memory is placed close to the CPU that can be accessed without stalls. The next lower memory levels are increasingly larger but also slower the further away they are from the CPU. Addresses are mapped from a larger memory to a smaller but faster memory higher in the hierarchy. Typically, the higher–level memories are cache memories that are automatically managed by a cache controller. Through this type of architecture, the average memory access time will be closer to the access time of the fastest memory rather than to the access time of the slowest memory.

Figure 1-1. Flat Versus Hierarchical Memory Architecture

Principle of Locality www.ti.com

#### 1.6 Principle of Locality

Caches reduce the average memory access time by exploiting the locality of memory accesses. The principle of locality assumes that if a memory location was referenced it is very likely that the same or a neighboring location will be referenced soon again. Referencing memory locations within some period of time is referred to as *temporal locality*. Referencing neighboring memory locations is referred to as *spatial locality*. A program typically reuses data from the same or adjacent memory locations within a small period of time. If the data is fetched from a slow memory into a fast cache memory and is accessed as often as possible before it is being replaced with another set of data, the benefits become apparent.

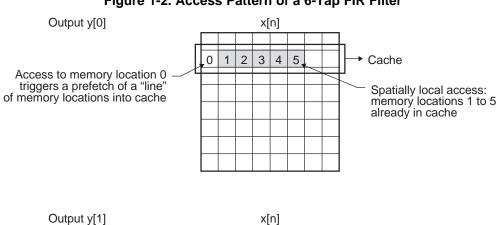

The following example illustrates the concept of spatial and temporal locality. Consider the memory access pattern of a 6-tap FIR filter. The required computations for the first two outputs y[0] and y[1] are:

$$y[0] = h[0] \times x[0] + h[1] \times x[1] + ... + h[5] \times x[5]$$

$y[1] = h[0] \times x[1] + h[1] \times x[2] + ... + h[5] \times x[6]$

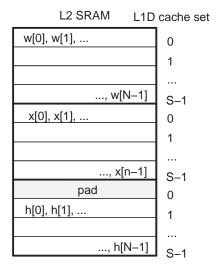

Consequently, to compute one output we have to read six data samples from an input data buffer x[ ]. Figure 1-2 shows the memory layout of this buffer and how its elements are accessed. When the first access is made to memory location 0, the cache controller fetches the data for the address accessed and also the data for a certain number of the following addresses into cache. This range of addresses is called a *cache line*. The motivation for this behavior is that accesses are assumed to be spatially local. This is true for the FIR filter, since the next five samples are required as well. Then all accesses will go to the fast cache instead of the slow lower-level memory.

Consider now the calculation of the next output, y[1]. The access pattern again is shown in Figure 1-2. Five of the samples are being reused from the previous computation and only one sample is new; but all of them are already held in cache and no CPU stalls occur. This access pattern exhibits high spatial and temporal locality: the same data that was used in the previous step is being used again for processing.

Cache builds on the fact that data accesses are spatially and temporally local. The number of accesses to a slower, lower-level memory are greatly reduced, and the majority of accesses can be serviced at CPU speed from the high-level cache memory.

Figure 1-2. Access Pattern of a 6-Tap FIR Filter

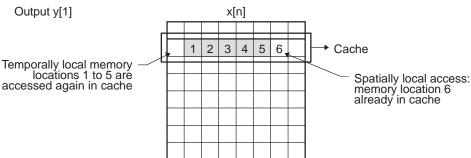

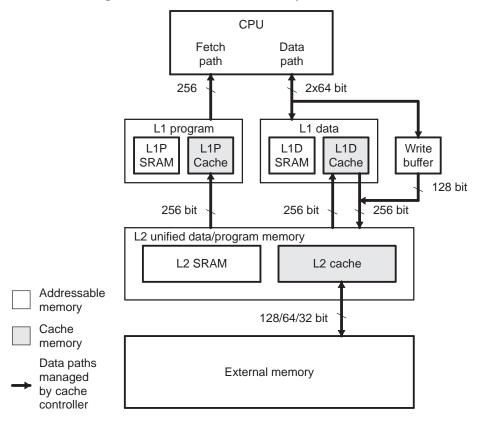

#### 1.7 Cache Memory Architecture Overview

The C64x+ DSP memory architecture consists of a two-level internal cache-based memory architecture plus external memory. Level 1 memory is split into program (L1P) and data (L1D). Both L1P and L1D can be configured into SRAM and cache with up to 32K bytes of cache. All caches and data paths shown in Figure 1-3 are automatically managed by the cache controller. Level 1 memory is accessed by the CPU without stalls. Level 2 memory is also configurable and can be split into L2 SRAM and cache with up to 256K bytes of cache. External memory can be several Megabytes large. The access time depends on the interface and the memory technology used.

Figure 1-3. C64x+ Cache Memory Architecture

Cache Basics www.ti.com

#### 1.8 Cache Basics

This section explains the different types of cache architectures and how they work. Generally, one can distinguish between direct-mapped caches and set-associative caches. The types of caches described use the C64x+ L1P (direct-mapped) and L1D (set-associative) as examples; however, the concept is similar for all cache-based computer architectures. This section focuses on the behavior of the cache system. Any performance considerations, including various stall conditions and associated stall cycles are discussed in Section 3.2.

### 1.8.1 Direct-Mapped Caches

The C64x+ program cache (L1P) shall be used as an example to explain how a direct-mapped cache functions. Whenever the CPU accesses instructions in L2 SRAM or external memory, the instructions are brought into L1P cache. The characteristics of the C64x+ and the C64x L1P caches are summarized and compared in Table 1-2. The L1P miss stall characteristics are provided in Table 1-3.

Table 1-2. L1P Cache Characteristics

| Characteristic               | C64x+ DSP                 | C64x DSP      |  |

|------------------------------|---------------------------|---------------|--|

| Organization                 | Direct-mapped             | Direct-mapped |  |

| Protocol                     | Read Allocate             | Read Allocate |  |

| CPU access time              | 1 cycle                   | 1 cycle       |  |

| Capacity                     | 4K, 8K, 16K, or 32K bytes | 16K bytes     |  |

| Line size                    | 32 bytes                  | 32 bytes      |  |

| External Memory Cacheability | Always cached             | Configurable  |  |

Table 1-3, L1P Miss Stall Characteristics

|                                 |                 | L2 1            | L2 Type         |                 |

|---------------------------------|-----------------|-----------------|-----------------|-----------------|

|                                 | 0 Wait-State, 2 | × 128-bit Banks | 1 Wait-State, 4 | × 128-bit Banks |

| Instructions per Execute Packet | L2 SRAM         | L2 Cache        | L2 SRAM         | L2 Cache        |

| 1                               | 0.000           | 0.000           | 0.000           | 0.000           |

| 2                               | 0.001           | 0.497           | 0.167           | 0.499           |

| 3                               | 0.501           | 1.247           | 0.751           | 1.249           |

| 4                               | 0.997           | 1.997           | 1.329           | 1.999           |

| 5                               | 1.499           | 2.747           | 1.915           | 2.749           |

| 6                               | 2.001           | 3.497           | 2.501           | 3.499           |

| 7                               | 2.497           | 4.247           | 3.079           | 4.249           |

| 8                               | 2.999           | 4.997           | 3.665           | 4.999           |

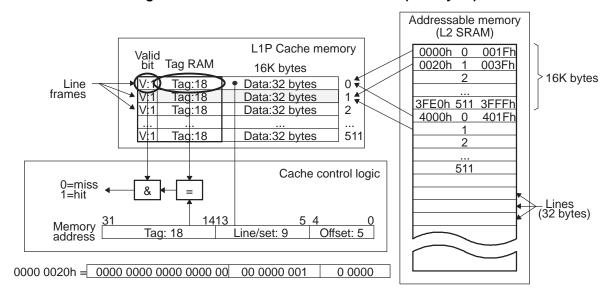

Figure 1-4 shows the architecture of the C64+x L1P cache that consists of the cache memory and the cache control logic. Additionally, addressable memory (L2 SRAM or external memory) is shown. The cache memory size is 16K bytes in the example and consists of 512 32-byte lines. Each line frame always maps to the same fixed addresses in memory. For instance, as shown in Figure 1-4, addresses 0000h to 0019h are always cached in line frame 0 and addresses 3FE0h to 3FFFh are always cached in line frame 511. Since the capacity of the cache has been exhausted, addresses 4000h to 4019h map to line frame 0, and so forth. Note that one line contains exactly one instruction fetch packet.

www.ti.com Cache Basics

Figure 1-4. C64x+ L1P Cache Architecture (16K Bytes)

#### 1.8.1.1 Read Misses

Consider a CPU program fetch access to address location 0020h. Assume that cache is completely invalidated, meaning that no line frame contains cached data. The valid state of a line frame is indicated by the valid (V) bit. A valid bit of 0 means that the corresponding cache line frame is invalid, that is, does not contain cached data. When the CPU makes a request to read address 0020h, the cache controller splits up the address into three portions as shown in Figure 1-5.

Figure 1-5. Memory Address from Cache Controller (For 16K Byte Cache Size)

The set portion (bits 13-5) indicates to which set the address maps to (in case of direct caches, a set is equivalent to a line frame). For the address 0020h, the set portion is 1. The controller then checks the tag (bits 31–14) and the valid bit. Since we assumed that the valid bit is 0, the controller registers a miss, that is the requested address is not contained in cache.

A miss also means that a line frame will be allocated for the line containing the requested address. Then the controller fetches the line (0020h-0039h) from memory and stores the data in line frame 1. The tag portion of the address is stored in the tag RAM and the valid bit is changed to 1 to indicate that the set now contains valid data. The fetched data is also forwarded to the CPU, and the access is complete. Why a tag portion of the address has to be stored becomes clear when address 0020h is accessed again. This is explained next.

#### 1.8.1.2 Read Hits

The cache controller splits up the address into the three portions, as shown in Figure 1-5. The set portion determines the set, and the stored tag portion is now compared against the tag portion of the address requested. This comparison is necessary since multiple lines in memory are mapped to the same set. If we had accessed address 4020h that also maps to the same set, the tag portions would be different and the access would have been a miss. If address 0020h is accessed, the tag comparison is true and the valid bit is 1; thus, the controller registers a hit and forwards the data in the cache line to the CPU. The access is complete.

Cache Basics www.ti.com

#### 1.8.2 Types of Cache Misses

Before set-associative caches are discussed, it is beneficial to acquire a better understanding of the properties of different types of cache misses. The ultimate purpose of a cache is to reduce the average memory access time. For each miss, there is a penalty for fetching a line of data from memory into cache. Therefore, the more often a cache line is reused the lower the impact of the initial penalty and the shorter the average memory access time becomes. The key is to reuse this line as much as possible before it is replaced with another line.

Replacing a line involves *eviction* of the line from cache and using the same line frame to store another line. If later the evicted line is accessed again, the access misses and the line has to be fetched again from slower memory. Therefore, it is important to avoid eviction of a line as long as it is still used.

#### 1.8.2.1 Conflict and Capacity Misses

Evictions are caused by conflicts, that is, a memory location is accessed that maps to the same set as a memory location that was cached earlier. This type of miss is referred to as a *conflict miss*, a miss that occurred because the line was evicted due to a conflict before it was reused. It is further distinguished whether the conflict occurred because the capacity of the cache was exhausted or not. If the capacity was exhausted, all line frames in the cache were allocated when the miss occurred, then the miss is referred to as a *capacity miss*. Capacity misses occur if a data set that exceeds the cache capacity is reused. When the capacity is exhausted, new lines accessed start replacing lines from the beginning of the array.

Identifying the cause of a miss may help to choose the appropriate measure for avoiding the miss. Conflict misses mean that the data accessed fits into cache but lines get evicted due to conflicts. In this case, we may want to change the memory layout so that the data accessed is located at addresses in memory that do not conflict (map to the same set) in cache. Alternatively, from a hardware design, we can create sets that can hold two or more lines. Thus, two lines from memory that map to the same set can both be kept in cache without evicting one another. This is the idea of *set-associative* caches, described in Section 1.8.3.

In case of capacity misses, one may want to reduce the amount of data that is operated on at a time. Alternatively, from a hardware design, the capacity of the cache can be increased.

#### 1.8.2.2 Compulsory Misses

A third category of misses are *compulsory misses* or first reference misses. They occur when the data is brought in cache for the first time. Unlike the other two misses, they cannot be avoided, hence, they are compulsory.

#### 1.8.3 Set-Associative Caches

Set-associative caches have multiple *cache ways* to reduce the probability of conflict misses. The C64x+L1D cache is a 2-way set-associative cache with 4K, 8K, 16K, or 32K bytes capacity and 64-byte lines. The characteristics of the L1D cache are summarized in Table 1-4. The L1D miss stall characteristics are provided in Table 1-5.

Table 1-4. L1D Cache Characteristics

| Characteristic               | C64x+ DSP                 | C64x DSP                  |

|------------------------------|---------------------------|---------------------------|

| Organization                 | 2-way set-associative     | 2-way set-associative     |

| Protocol                     | Read Allocate, Write-back | Read Allocate, Write-back |

| CPU access time              | 1 cycle                   | 1 cycle                   |

| Capacity                     | 4K, 8K, 16K, or 32K bytes | 16K bytes                 |

| Line size                    | 64 bytes                  | 64 bytes                  |

| Replacement strategy         | Least recently used (LRU) | Least recently used (LRU) |

| Write Buffer                 | 4 x 128-bit entries       | 4 x 64-bit entries        |

| External Memory Cacheability | Configurable              | Configurable              |

www.ti.com Cache Basics

**Table 1-5. L1D Miss Stall Characteristics**

|                                                   | L2 Type                                               |                                                       |                                                       |                                                       |  |

|---------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|--|

|                                                   | 0 Wait-State, 2 × 128-bit Banks                       |                                                       | 1 Wait-State, 4 × 128-bit Banks                       |                                                       |  |

| Parameter                                         | L2 SRAM                                               | L2 Cache                                              | L2 SRAM                                               | L2 Cache                                              |  |

| Single Read Miss                                  | 10.5                                                  | 12.5                                                  | 12.5                                                  | 14.5                                                  |  |

| 2 Parallel Read Misses (pipelined)                | 10.5 + 4                                              | 12.5 + 8                                              | 12.5 + 4                                              | 14.5 + 8                                              |  |

| M Consecutive Read Misses (pipelined)             | 10.5 + 3 × (M - 1)                                    | 12.5 + 7 × (M - 1)                                    | $12.5 + 3 \times (M - 1)$                             | 14.5 + 7 × (M - 1)                                    |  |

| M Consecutive Parallel Read<br>Misses (pipelined) | 10.5 + 4 × (M/2 - 1) +<br>3 × M/2                     | 12.5 + 8 × (M/2 - 1) +<br>7 × M/2                     | 12.5 + 4 × (M - 1)                                    | 14.5 + 8 × (M/2 - 1) +<br>7 × M/2                     |  |

| Victim Buffer Flush on Read Miss                  | disrupts miss<br>pipelining plus<br>maximum 11 stalls | disrupts miss<br>pipelining plus<br>maximum 11 stalls | disrupts miss<br>pipelining plus<br>maximum 10 stalls | disrupts miss<br>pipelining plus<br>maximum 10 stalls |  |

| Write Buffer Drain Rate                           | 2 cycles/entry                                        | 6 cycles/entry                                        | 2 cycles/entry                                        | 6 cycles/entry                                        |  |

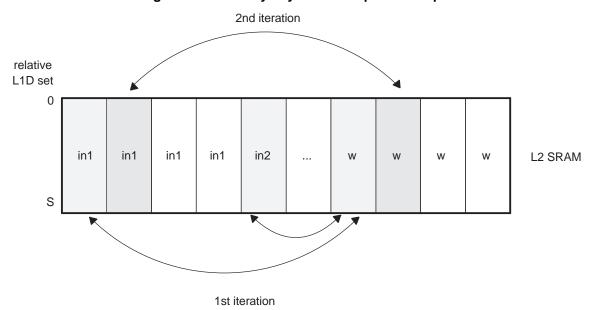

Compared to a direct-mapped cache, each set of a 2-way set-associative cache consists of two line frames, one line frame in way 0 and another line frame in way 1. A line in memory still maps to one set, but now can be stored in either of the two line frames. In this sense, a direct-mapped cache can also be viewed as a 1-way cache.

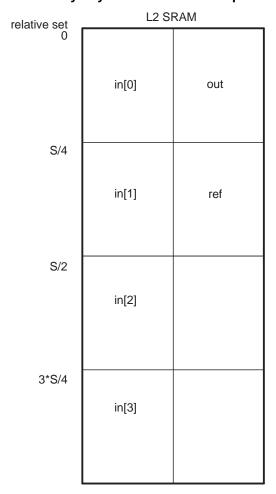

The set-associative cache architecture is explained by examining how misses and hits are handled for the C64x+ L1D cache, shown in Figure 1-6. Hits and misses are determined similar as in a direct-mapped cache, except that two tag comparisons, one for each way, are necessary to determine which way the requested data is kept.

Memory (L2 SRAM) LRU L1D Cache memory 0 0 Tag RAM 16K bytes way0 D: 1 (V: 1 0 Tag: 18 0 \$ 2 8K bytes LRU: 1 Data: 64 bytes LRU: 1 D: 1 V: 1 Tag: 18 Data: 64 bytes 127 Tag: 18 Data: 64 bytes LRU: 1 V: 1 2 way1 D: 1 0 0 4 D: 1 ( V: 1 0 Data: 64 bytes Tag: 18 LRU: 1 D: 1 1 D: 1 V: 1 Tag: 18 Data: 64 bytes 1 2 D: 1 V: 1 Tag: 18 Data: 64 bytes 2 127 D: 1 V: 1 Tag: 18 Data: 64 bytes 127 Cache control logic 0: miss 1: hit in way 0 0: miss hit in way 1 13 12 Memory address Tag: 18 Set: 7 Offset: 6

Figure 1-6. C64x+ L1D Cache Architecture (16K Bytes)

Cache Basics www.ti.com

#### 1.8.3.1 Read Misses

If both ways miss, the data first needs to be fetched from memory. The LRU bit determines in which cache way the line frame is allocated. An LRU bit exists for each set and can be thought of as a switch. If the LRU bit is 0, the line frame in way 0 is allocated; if the LRU bit is 1, the line frame in way 1 is allocated. The state of the LRU bit changes whenever an access is made to the line frame. When a way is accessed, the LRU bit always switches to the opposite way, as to protect the most-recently-used line frame from being evicted. Conversely, on a miss, the least-recently-used (LRU) line frame in a set is allocated to the new line evicting the current line. The reason behind this line replacement scheme is based on the principle of locality: if a memory location was accessed, then the same or a neighboring location will be accessed soon again. Note that the LRU bit is only consulted on a miss, but its status is updated every time a line frame is accessed regardless whether it was a hit or a miss, a read or a write.

#### 1.8.3.2 Write Misses

L1D is a *read–allocate* cache, meaning that a line is allocated on a read miss only. On a write miss, the data is written to the lower-level memory through a *write buffer*, bypassing L1D cache (see Figure 1-3). The write buffer consists of 4 entries. On C64x+ devices, each entry is 128-bits wide.

#### 1.8.3.3 Read Hits

If there is a read hit in way 0, the data of the line frame in way 0 is accessed; if there is a hit in way 1, the data of the line frame in way 1 is accessed.

#### 1.8.3.4 Write Hits