# TMS320C64x+ DSP Megamodule

# **Reference Guide**

Literature Number: SPRU871K August 2010

# **Contents**

| Pref |          |                                                             |    |

|------|----------|-------------------------------------------------------------|----|

| 1    | Overv    | <i>r</i> iew 1                                              | 7  |

|      | 1.1      | Introduction 1                                              | 8  |

|      | 1.2      | C64x+ Megamodule Overview 1                                 | 9  |

|      |          | 1.2.1 C64x+ CPU 1                                           | 9  |

|      |          | 1.2.2 Level 1 Program (L1P) Memory Controller 1             | 9  |

|      |          | 1.2.3 Level 1 Data (L1D) Memory Controller 1                | 9  |

|      |          | 1.2.4 Level 2 (L2) Memory Controller 1                      | 9  |

|      |          | 1.2.5 Internal DMA (IDMA)                                   |    |

|      |          | 1.2.6 Bandwidth Management (BWM) 2                          | 20 |

|      |          | 1.2.7 Interrupt Controller (INTC)                           | 20 |

|      |          | 1.2.8 Memory Protection Architecture (MPA)                  |    |

|      |          | 1.2.9 Power-Down Controller (PDC)                           | 21 |

|      |          | 1.2.10 Extended Memory Controller (EMC) 2                   | 21 |

| 2    | Level    | 1 Program Memory and Cache 2                                | 3  |

| -    | 2.1      | Introduction                                                |    |

|      |          | 2.1.1 Purpose of the Level 1 Program (L1P) Memory and Cache |    |

|      |          | 2.1.2 Features                                              |    |

|      | 2.2      | Terms and Definitions                                       |    |

|      | 2.3      | L1 Program Memory Architecture                              |    |

|      |          | 2.3.1 L1P Memory                                            |    |

|      | 2.4      | L1P Cache                                                   |    |

|      |          | 2.4.1 L1P Cache Architecture                                | -  |

|      |          | 2.4.2 Replacement and Allocation Strategy                   |    |

|      |          | 2.4.3 L1P Mode Change Operations                            |    |

|      |          | 2.4.4 L1P Freeze Mode                                       |    |

|      | 2.5      | Program Initiated Coherence Operations                      |    |

|      |          | 2.5.1 Global Coherence Operation                            |    |

|      |          | 2.5.2 Block Coherence Operation                             |    |

|      | 2.6      | L1P Cache Control Registers                                 |    |

|      |          | 2.6.1 Memory Mapped Cache Control Register Overview         |    |

|      |          | 2.6.2 CPU Cache Control Registers                           |    |

|      |          | 2.6.3 L1P Cache Configuration Registers                     |    |

|      |          | 2.6.4 Privilege and Cache Control Operations                |    |

|      | 2.7      | L1P Performance                                             |    |

|      |          | 2.7.1 L1P Miss Penalty                                      |    |

|      |          | 2.7.2 L1P Miss Pipelining                                   | 34 |

|      | 2.8      | Power-Down Support                                          |    |

|      |          | 2.8.1 Static Power-Down                                     |    |

|      |          | 2.8.2 Dynamic Power-Down                                    |    |

|      |          | 2.8.3 Feature-Oriented Power-Down                           |    |

|      | 2.9      | L1P Memory Protection                                       |    |

|      | -        | 2.9.1 Protection Checks on L1P Accesses                     |    |

|      |          | 2.9.2 Memory Protection Registers                           |    |

| 3    |          | 1 Data Memory and Cache                                     |    |

| 5    | Level    |                                                             |    |

| SPRU | J871K–Au | Igust 2010 Contents                                         | 3  |

| www. |  |

|------|--|

|      |  |

|      |  |

| 3.1 | Introdu                                                                                                                                        | iction                                                                                                                                                                                            | 50                                                                                                   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|     | 3.1.1                                                                                                                                          | Purpose of the Level 1 Data (L1D) Memory and Cache                                                                                                                                                | 50                                                                                                   |

|     | 3.1.2                                                                                                                                          | Features                                                                                                                                                                                          | 50                                                                                                   |

|     | 3.1.3                                                                                                                                          | Terms and Definitions                                                                                                                                                                             | 50                                                                                                   |

| 3.2 | L1D M                                                                                                                                          | emory Architecture                                                                                                                                                                                | 50                                                                                                   |

|     | 3.2.1                                                                                                                                          | L1D Memory                                                                                                                                                                                        | 50                                                                                                   |

| 3.3 |                                                                                                                                                | ache                                                                                                                                                                                              |                                                                                                      |

|     | 3.3.1                                                                                                                                          | L1D Cache Architecture                                                                                                                                                                            |                                                                                                      |

|     | 3.3.2                                                                                                                                          | Replacement and Allocation Strategy                                                                                                                                                               |                                                                                                      |

|     |                                                                                                                                                | L1D Mode Change Operations                                                                                                                                                                        |                                                                                                      |

|     |                                                                                                                                                | L1D Freeze Mode                                                                                                                                                                                   |                                                                                                      |

|     | 3.3.5                                                                                                                                          | Program-Initiated Cache Coherence Operations                                                                                                                                                      |                                                                                                      |

|     |                                                                                                                                                | Cache Coherence Protocol                                                                                                                                                                          |                                                                                                      |

| 3.4 |                                                                                                                                                | ache Control Registers                                                                                                                                                                            |                                                                                                      |

| 0.1 | 3.4.1                                                                                                                                          | Memory Mapped L1D Cache Control Register Overview                                                                                                                                                 |                                                                                                      |

|     | -                                                                                                                                              | CPU L1D Cache Control Registers                                                                                                                                                                   |                                                                                                      |

|     |                                                                                                                                                | L1D Cache Configuration Registers                                                                                                                                                                 |                                                                                                      |

|     |                                                                                                                                                | L1D Cache Coherence Operation Registers                                                                                                                                                           |                                                                                                      |

|     | 3.4.4<br>3.4.5                                                                                                                                 | Privilege and Cache Control Operations                                                                                                                                                            |                                                                                                      |

| 3.5 |                                                                                                                                                | emory Performance                                                                                                                                                                                 |                                                                                                      |

| 3.5 | 3.5.1                                                                                                                                          | L1D Memory Banking                                                                                                                                                                                |                                                                                                      |

|     |                                                                                                                                                | L1D Miemory Banking                                                                                                                                                                               |                                                                                                      |

|     |                                                                                                                                                | ,                                                                                                                                                                                                 |                                                                                                      |

|     |                                                                                                                                                | L1D Write Buffer                                                                                                                                                                                  |                                                                                                      |

| 2.0 |                                                                                                                                                |                                                                                                                                                                                                   |                                                                                                      |

| 3.6 |                                                                                                                                                | ower-Down Support                                                                                                                                                                                 |                                                                                                      |

| 3.7 |                                                                                                                                                | emory Protection                                                                                                                                                                                  |                                                                                                      |

|     | 3.7.1                                                                                                                                          | Protection Checks on L1D Accesses                                                                                                                                                                 |                                                                                                      |

|     |                                                                                                                                                | L1D Memory Protection Registers                                                                                                                                                                   |                                                                                                      |

|     |                                                                                                                                                | Protection Checks on Accesses to Memory Protection Registers                                                                                                                                      |                                                                                                      |

|     |                                                                                                                                                | nory and Cache                                                                                                                                                                                    |                                                                                                      |

| 4.1 |                                                                                                                                                | iction                                                                                                                                                                                            |                                                                                                      |

|     | 4.1.1                                                                                                                                          | Purpose of the Level 2 (L2) Memory and Cache                                                                                                                                                      |                                                                                                      |

|     | 4.1.2                                                                                                                                          | Features                                                                                                                                                                                          | 82                                                                                                   |

|     | 4.1.3                                                                                                                                          | Terms and Definitions                                                                                                                                                                             | 02                                                                                                   |

| 4.2 | Level 2                                                                                                                                        |                                                                                                                                                                                                   | 02                                                                                                   |

|     |                                                                                                                                                | 2 Memory Architecture                                                                                                                                                                             |                                                                                                      |

| 4.3 | 4.2.1                                                                                                                                          | 2 Memory Architecture                                                                                                                                                                             | 82                                                                                                   |

| 4.5 |                                                                                                                                                | •                                                                                                                                                                                                 | 82<br>82                                                                                             |

| 4.5 |                                                                                                                                                | L2 Memory                                                                                                                                                                                         | 82<br>82<br>84                                                                                       |

| 4.5 | L2 Cad                                                                                                                                         | L2 Memory                                                                                                                                                                                         | 82<br>82<br>84<br>84                                                                                 |

| 4.5 | L2 Cac<br>4.3.1                                                                                                                                | L2 Memory<br>che<br>L2 Cache Architecture                                                                                                                                                         | 82<br>82<br>84<br>84<br>85                                                                           |

| 4.3 | L2 Cao<br>4.3.1<br>4.3.2                                                                                                                       | L2 Memory<br>che<br>L2 Cache Architecture<br>Replacement and Allocation Strategy                                                                                                                  | 82<br>82<br>84<br>84<br>85<br>85                                                                     |

| 4.3 | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                                                                     | L2 Memory<br>che<br>L2 Cache Architecture<br>Replacement and Allocation Strategy<br>Reset Behavior                                                                                                | 82<br>82<br>84<br>84<br>85<br>85<br>85                                                               |

| 4.5 | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                                                                     | L2 Memory<br>che<br>L2 Cache Architecture<br>Replacement and Allocation Strategy<br>Reset Behavior<br>L2 Mode Change Operations                                                                   | 82<br>84<br>84<br>85<br>85<br>86<br>87                                                               |

| 4.5 | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5                                                                                            | L2 Memory<br>che<br>L2 Cache Architecture<br>Replacement and Allocation Strategy<br>Reset Behavior<br>L2 Mode Change Operations<br>L2 Freeze Mode                                                 | 82<br>84<br>84<br>85<br>85<br>86<br>87<br>88                                                         |

| 4.5 | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7                                                                          | L2 Memory<br>che<br>L2 Cache Architecture<br>Replacement and Allocation Strategy<br>Reset Behavior<br>L2 Mode Change Operations<br>L2 Freeze Mode<br>Program Initiated Cache Coherence Operations | 82<br>84<br>84<br>85<br>85<br>86<br>87<br>88<br>90                                                   |

| 4.3 | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8                                                                 | L2 Memory<br>che                                                                                                                                                                                  | 82<br>84<br>84<br>85<br>85<br>86<br>87<br>88<br>90<br>91                                             |

| -   | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8                                                                 | L2 Memory                                                                                                                                                                                         | 82<br>84<br>84<br>85<br>85<br>86<br>87<br>88<br>90<br>91<br>93                                       |

| -   | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>L2 Cac                                                       | L2 Memory                                                                                                                                                                                         | 82<br>84<br>84<br>85<br>85<br>86<br>87<br>88<br>90<br>91<br>93<br>93                                 |

| -   | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>L2 Cac<br>4.4.1<br>4.4.2                                     | L2 Memory                                                                                                                                                                                         | 82<br>84<br>84<br>85<br>85<br>86<br>87<br>88<br>90<br>91<br>93<br>93<br>93                           |

| -   | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>L2 Cac<br>4.4.1<br>4.4.2                                     | L2 Memory                                                                                                                                                                                         | 82<br>84<br>84<br>85<br>85<br>86<br>87<br>88<br>90<br>91<br>93<br>93<br>93                           |

| -   | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>L2 Cac<br>4.4.1<br>4.4.2<br>4.4.3                            | L2 Memory                                                                                                                                                                                         | 82<br>84<br>84<br>85<br>85<br>86<br>87<br>88<br>90<br>91<br>93<br>93<br>93<br>94                     |

| -   | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>L2 Cac<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4                   | L2 Memory                                                                                                                                                                                         | 82<br>82<br>84<br>85<br>85<br>86<br>87<br>88<br>90<br>91<br>93<br>93<br>93<br>94<br>95<br>100        |

| -   | L2 Cac<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>L2 Cac<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6 | L2 Memory<br>he                                                                                                                                                                                   | 82<br>82<br>84<br>85<br>85<br>86<br>87<br>88<br>90<br>91<br>93<br>93<br>93<br>94<br>95<br>100<br>106 |

4

4

|   |        | 451     | L2 Memory Dynamic Power-Down                                          | 107 |

|---|--------|---------|-----------------------------------------------------------------------|-----|

|   |        |         | L2 Memory Static Power-Down                                           |     |

|   |        |         | L2 Power-Down Control Registers                                       |     |

|   | 4.6    |         | mory Protection                                                       |     |

|   |        | 4.6.1   | Protection Checks on CPU, IDMA and Other System Master Accesses       |     |

|   |        | 4.6.2   | L2 Memory Protection Registers                                        |     |

|   |        | 4.6.3   | Protection Checks on Accesses to Memory Protection Registers          |     |

| 5 | Interr |         | ect Memory Access (IDMA) Controller                                   |     |

| 5 | 5.1    |         |                                                                       |     |

|   | 0.1    | 5.1.1   | Purpose of the Internal Direct Memory Access (IDMA) Controller        |     |

|   |        | 5.1.2   | Features                                                              |     |

|   | 5.2    | ••••=   | and Definitions                                                       |     |

|   | 5.3    |         | Architecture                                                          |     |

|   | 0.0    | 5.3.1   | IDMA Channel 0                                                        |     |

|   |        | 5.3.2   | IDMA Channel 1                                                        |     |

|   | 5.4    | Reaist  | ers                                                                   |     |

|   | -      | 5.4.1   | IDMA Channel 0 Status Register (IDMA0_STAT)                           |     |

|   |        | 5.4.2   | IDMA Channel 0 Mask Register (IDMA0_MASK)                             |     |

|   |        | 5.4.3   | IDMA Channel 0 Source Address Register (IDMA0_SOURCE)                 |     |

|   |        | 5.4.4   | IDMA Channel 0 Destination Address Register (IDMA0_DEST)              |     |

|   |        | 5.4.5   | IDMA Channel 0 Count Register (IDMA0_COUNT)                           |     |

|   |        | 5.4.6   | IDMA Channel 1 Status Register (IDMA1_STAT)                           |     |

|   |        | 5.4.7   | IDMA Channel 1 Source Address Register (IDMA1_SOURCE)                 |     |

|   |        | 5.4.8   | IDMA Channel 1 Destination Address Register (IDMA1_DEST)              |     |

|   |        | 5.4.9   | IDMA Channel 1 Count Register (IDMA1_COUNT)                           |     |

|   | 5.5    | Privile | ge Levels and IDMA Operation                                          | 141 |

| 6 | Band   | width   | Management Architecture                                               | 143 |

| • | 6.1    |         | uction                                                                |     |

|   |        | 6.1.1   | Purpose of the Bandwidth Management                                   |     |

|   |        | 6.1.2   | Resource Bandwidth Protected by Bandwidth Management                  |     |

|   |        | 6.1.3   | Requestors Managed by Bandwidth Management                            |     |

|   |        | 6.1.4   | Terms and Definitions                                                 | 144 |

|   | 6.2    | Archite | ecture                                                                | 145 |

|   |        | 6.2.1   | Bandwidth Arbitration via Priority Levels                             | 145 |

|   |        | 6.2.2   | Priority Level: -1                                                    | 145 |

|   |        | 6.2.3   | Priority Declaration                                                  | 145 |

|   | 6.3    | Regist  | ers                                                                   | 146 |

|   |        | 6.3.1   | CPU Arbitration Control Register (CPUARBD, CPUARBU, CPUARBE)          | 147 |

|   |        | 6.3.2   | User Coherence Arbitration Control Register (UCARBD, UCARBU)          | 149 |

|   |        | 6.3.3   | IDMA Arbitration Control Register (IDMAARBD, IDMAARBU, IDMAARBE)      | 150 |

|   |        | 6.3.4   | Slave DMA Arbitration Control Register (SDMAARBD, SDMAARBU, SDMAARBE) | 151 |

|   |        | 6.3.5   | Master DMA Arbitration Control Register (MDMAARBE)                    | 152 |

|   | 6.4    | Privile | ge and Bandwidth Management Registers                                 | 153 |

| 7 | Interr | upt Co  | ontroller                                                             | 155 |

|   | 7.1    | •       | uction                                                                |     |

|   |        | 7.1.1   | Purpose of the C64x+ Megamodule Interrupt Controller (INTC)           |     |

|   |        | 7.1.2   | Features                                                              |     |

|   |        | 7.1.3   | Functional Block Diagram                                              |     |

|   |        | 7.1.4   | Terms and Definitions                                                 |     |

|   | 7.2    | Interru | pt Controller Architecture                                            | 158 |

|   |        | 7.2.1   | Event Registers                                                       |     |

|   |        | 7.2.2   | Event Combiner                                                        |     |

|   |        | 7.2.3   | Interrupt Selector                                                    |     |

|   |        | -       |                                                                       |     |

| www.ti.com |

|------------|

|------------|

|    |       | 724     | Exception Combiner                                        | 164        |

|----|-------|---------|-----------------------------------------------------------|------------|

|    | 7.3   |         | Megamodule Events                                         |            |

|    | 7.4   |         | pt Controller - CPU Interaction                           |            |

|    |       | 7.4.1   | CPU – Interrupt Controller Interface                      |            |

|    |       | 7.4.2   | CPU Servicing of Interrupt Events                         |            |

|    | 7.5   |         | ers                                                       |            |

|    | 1.0   | 7.5.1   | Event Registers                                           |            |

|    |       | 7.5.2   | Event Combiner Registers                                  |            |

|    |       | 7.5.3   | CPU Interrupt Selector Registers                          |            |

|    |       | 7.5.4   | CPU Exception Registers                                   |            |

|    |       | 7.5.5   | Advanced Event Generator Mux Registers (AEGMUX <i>n</i> ) |            |

|    |       | 7.5.6   | Privilege and Interrupt Controller Registers              |            |

| 8  | Memo  | orv Pro | otection                                                  | 187        |

| -  | 8.1   |         | uction                                                    |            |

|    |       | 8.1.1   | Purpose of the Memory Protection                          |            |

|    |       | 8.1.2   | Privilege Levels                                          |            |

|    | 8.2   | Terms   | and Definitions                                           |            |

|    | 8.3   | Memo    | ry Protection Architecture                                | 188        |

|    |       | 8.3.1   | Memory Protection Pages                                   | 188        |

|    |       | 8.3.2   | Permission Structure                                      | 189        |

|    |       | 8.3.3   | Invalid Accesses and Exceptions                           | 190        |

|    | 8.4   | Memo    | ry Protection Architecture Registers                      | 191        |

|    |       | 8.4.1   | Memory Protection Page Attribute (MPPA) Registers         | 192        |

|    |       | 8.4.2   | Memory Protection Fault Registers (MPFAR, MPFSR, MPFCR)   | 192        |

|    |       | 8.4.3   | Memory Protection Lock Registers (MPLKn)                  | 196        |

|    |       | 8.4.4   | Keys Shorter than 128 Bits                                |            |

|    | 8.5   | Permis  | ssion Checks on Accesses to Memory Protection Registers   | 199        |

| 9  | Powe  | r-Dow   | n Controller                                              | <b>201</b> |

|    | 9.1   | Introdu | uction                                                    | 202        |

|    |       | 9.1.1   | C64x+ Megamodule Power Down-Management                    | 202        |

|    |       | 9.1.2   | Power-Down Capabilities Overview                          | 202        |

|    | 9.2   | Power   | -Down Features                                            | 202        |

|    |       | 9.2.1   | L1P Memory                                                |            |

|    |       | 9.2.2   | L2 Memory                                                 |            |

|    |       | 9.2.3   | Cache Power-Down Modes                                    | 203        |

|    |       | 9.2.4   | CPU Power-Down                                            |            |

|    |       | 9.2.5   | C64x+ Megamodule Power-Down                               |            |

|    |       | 9.2.6   | Miscellaneous Power-Down                                  |            |

|    | 9.3   | Power   | -Down Controller Command Register (PDCCMD)                | 204        |

| 10 | Misce | llaneo  | us                                                        | <b>207</b> |

|    | 10.1  | Introdu | uction                                                    | 208        |

|    | 10.2  | -       | nodule Revision ID Register (MM_REVID)                    |            |

|    | 10.3  |         | rror Register (BUSERR)                                    |            |

|    | 10.4  | Bus Er  | rror Details Register (BUSERRCLR)                         | 210        |

| Α  | Gene  | ral Ter | ms and Definitions                                        | 211        |

| В  | Cache | e Term  | is and Definitions                                        | 213        |

| С  | Revis | ion Hi  | story                                                     | 217        |

|    |       |         |                                                           |            |

# List of Figures

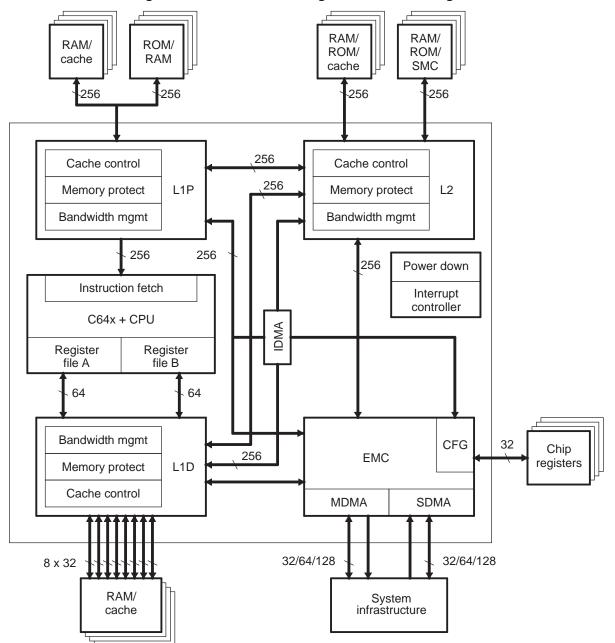

| 1-1.  | TMS320C64x+ Megamodule Block Diagram                              | 18               |

|-------|-------------------------------------------------------------------|------------------|

| 2-1.  | Data Access Address Organization                                  | 25               |

| 2-2.  | L1P Configuration Register (L1PCFG)                               | 31               |

| 2-3.  | L1P Cache Control Register (L1PCC)                                | 32               |

| 2-4.  | L1P Invalidate Base Address Register (L1PIBAR)                    | 32               |

| 2-5.  | L1P Invalidate Word Count Register (L1PIWC)                       | 33               |

| 2-6.  | L1P Invalidate Register (L1PINV)                                  | 33               |

| 2-7.  | Memory Page Protection Attribute Registers (L1PMPPAx)             | 40               |

| 2-8.  | Memory Protection Lock Register 0 (L1PMPLK0)                      | 42               |

| 2-9.  | Memory Protection Lock Register 1 (L1PMPLK1)                      | 42               |

| 2-10. | Memory Protection Lock Register 2 (L1PMPLK2)                      | 42               |

| 2-11. | Memory Protection Lock Register 3 (L1PMPLK3)                      | 43               |

| 2-12. | Memory Protection Lock Command Register (L1PMPLKCMD)              | 43               |

| 2-13. | Memory Protection Lock Status Register (L1PMPLKSTAT)              | 44               |

| 2-14. | L1P Memory Protection Fault Address Register (L1PMPFAR)           | 45               |

| 2-15. | L1P Memory Protection Fault Set Register (L1PMPFSR)               | 46               |

| 2-16. | L1P Memory Protection Fault Clear Register (L1PMPFCLR)            | 47               |

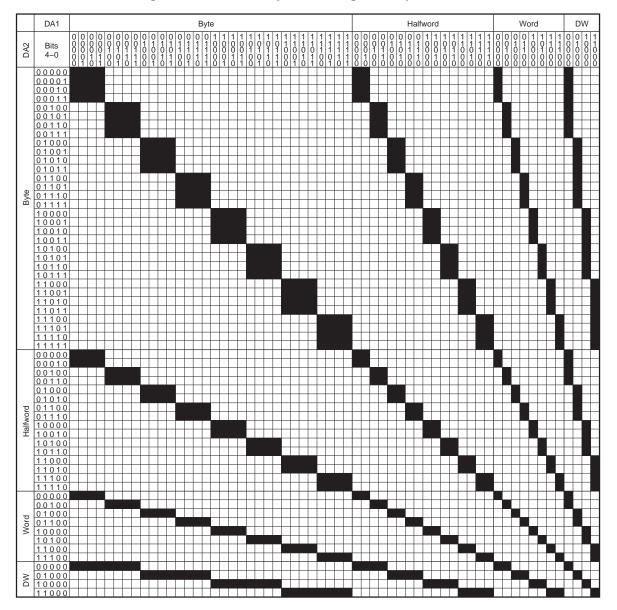

| 3-1.  | Data Access Address Organization                                  | 51               |

| 3-2.  | L1D Cache Configuration Register (L1DCFG)                         | <b>60</b>        |

| 3-3.  | L1D Cache Control Register (L1DCC)                                | 61               |

| 3-4.  | L1D Invalidate Register (L1DINV)                                  | 62               |

| 3-5.  | L1P Writeback Register (L1DWB)                                    | 63               |

| 3-6.  | L1D Writeback-Invalidate Register (L1DWBINV)                      | 63               |

| 3-7.  | L1D Invalidate Base Address Register (L1DIBAR)                    | <mark>6</mark> 4 |

| 3-8.  | L1D Invalidate Word Count Register (L1DIWC)                       | 64               |

| 3-9.  | L1D Writeback Base Address Register (L1DWBAR)                     | 65               |

| 3-10. | L1D Writeback-Invalidate Word Count Register (L1DWIWC)            | 65               |

| 3-11. | Address to Bank Number Mapping                                    | 66               |

| 3-12. | Potentially Conflicting Memory Accesses                           | 67               |

| 3-13. | Memory Protection Register (MPPAxx)                               | 72               |

| 3-14. | Level 1 Data Memory Protection Lock Register 0 (L1DMPLK0)         | 74               |

| 3-15. | Level 1 Data Memory Protection Lock Register 1 (L1DMPLK1)         | 74               |

| 3-16. | Level 1 Data Memory Protection Lock Register 2 (L1DMPLK2)         | 74               |

| 3-17. | Level 1 Data Memory Protection Lock Register 3 (L1DMPLK3)         | 74               |

| 3-18. | Level 1 Data Memory Protection Lock Command Register (L1DMPLKCMD) | 75               |

| 3-19. | Level 1 Data Memory Protection Lock Status Register (L1DMPLKSTAT) | 76               |

| 3-20. | Memory Protection Fault Address Register (L1DMPFAR)               | 76               |

| 3-21. | Memory Protection Fault Set Register (L1DMPFSR)                   | 77               |

| 3-22. | Memory Protection Fault Clear Register (L1DMPFCR)                 | 78               |

| 4-1.  | L2 Cache Address Organization                                     | 84               |

| 4-2.  | L2 Configuration Register (L2CFG)                                 | 94               |

| 4-3.  | L2 Writeback Base Address Register (L2WBAR)                       | 95               |

| 4-4.  | L2 Writeback Word Count Register (L2WWC)                          | 95               |

| 4-5.  | L2 Writeback-Invalidate Base Address Register (L2WIBAR)           | 96               |

| 4-6.  | L2 Writeback-Invalidate Word Count Register (L2WIWC)              |                  |

| 4-7.  | L2 Invalidate Base Address Register (L2IBAR)                      |                  |

| 4-8.  | L2 Invalidate Word Count Register (L2IWC)                         | 97               |

|       |                                                                   |                  |

7

# TEXAS INSTRUMENTS

www.ti.com

| 4-9.                   | L2 Writeback Register (L2WB)                                          | 98         |

|------------------------|-----------------------------------------------------------------------|------------|

| 4-10.                  | L2 Writeback-Invalidate Register (L2WBINV)                            | 98         |

| 4-11.                  | L2 Invalidate Register (L2INV)                                        | 99         |

| 4-12.                  | Memory Attribute Register (MARn)                                      | 106        |

| 4-13.                  | Level 2 Power-Down Wake Register (L2PDWAKEn)                          | 109        |

| 4-14.                  | Level 2 Power-Down Sleep Register (L2PDSLEEPn)                        | 110        |

| 4-15.                  | Level 2 Power-Down Status Register (L2PDSTATn)                        | 111        |

| 4-16.                  | L2 Memory Protection Page Attribute Registers (L2MPPAn)               | 116        |

| 4-17.                  | Level 2 Memory Protection Lock 0 Register (L2MPLK0)                   | 117        |

| 4-18.                  | Level 2 Memory Protection Lock 1 Register (L2MPLK1)                   | 118        |

| 4-19.                  | Level 2 Memory Protection Lock 2 Register (L2MPLK2)                   | 118        |

| 4-20.                  | Level 2 Memory Protection Lock 3 Register (L2MPLK3)                   | 118        |

| 4-21.                  | Level 2 Memory Protection Lock Command Register (L2MPLKCMD)           | 119        |

| 4-22.                  | Level 2 Memory Protection Lock Status Register (L2MPLKSTAT)           | 120        |

| 4-23.                  | Level 2 Memory Protection Fault Address Register (L2MPFAR)            | 121        |

| 4-24.                  | Level 2 Memory Protection Fault Set Register (L2MPFSR)                | 122        |

| 4-25.                  |                                                                       | 123        |

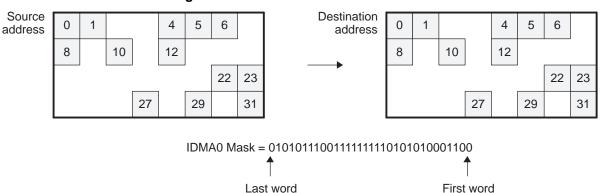

| 5-1.                   | IDMA Channel 0 Transaction                                            | 128        |

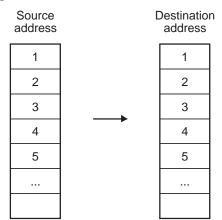

| 5-2.                   | IDMA Channel 1 Transaction                                            | 129        |

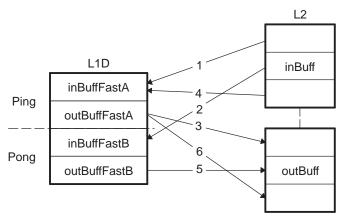

| 5-3.                   | Example of IDMA Channel 1                                             | 130        |

| 5-4.                   | IDMA Channel 0 Status Register (IDMA0_STAT)                           | 132        |

| 5-5.                   | IDMA Channel 0 Mask Register (IDMA0_MASK)                             | 133        |

| 5-6.                   | IDMA Channel 0 Source Address Register (IDMA0_SOURCE)                 | 134        |

| 5-7.                   | IDMA Channel 0 Destination Address Register (IDMA0_DEST)              | 135        |

| 5-8.                   | IDMA Channel 0 Count Register (IDMA0_COUNT)                           | 136        |

| 5-9.                   | IDMA Channel 1 Status Register (IDMA1_STAT)                           | 137        |

| 5-10.                  | IDMA Channel 1 Source Address Register (IDMA1_SOURCE)                 | 138        |

| 5-11.                  | IDMA Channel 1 Destination Address Register (IDMA1_DEST)              | 139        |

| 5-12.                  | IDMA Channel 1 Count Register (IDMA1_COUNT)                           | 140        |

| 6-1.                   | CPU Arbitration Control Register (CPUARBD, CPUARBU, CPUARBE)          | 148        |

| 6-2.                   | User Coherence Arbitration Control Register (UCARBD, UCARBU)          | 149        |

| 6-3.                   | IDMA Arbitration Control Register (IDMAARBD, IDMAARBU, IDMAARBE)      | 150        |

| 6-4.                   | Slave DMA Arbitration Control Register (SDMAARBD, SDMAARBU, SDMAARBE) | 151        |

| 6-5.                   | Master DMA Arbitration Control Register (MDMAARBE)                    | 152        |

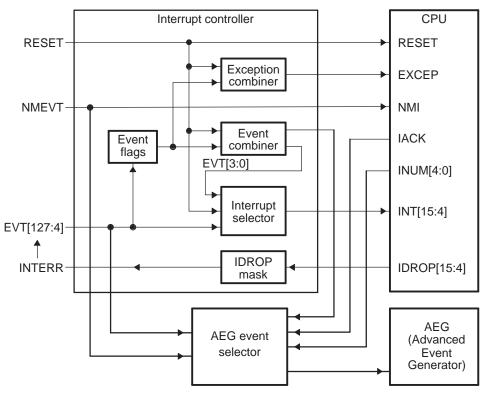

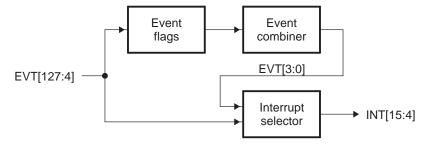

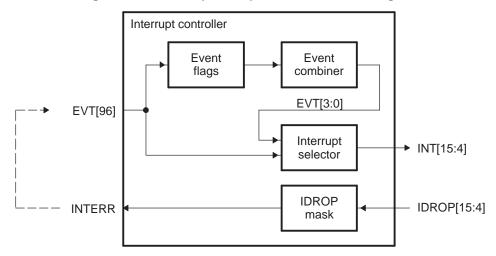

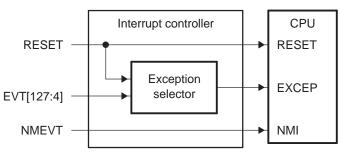

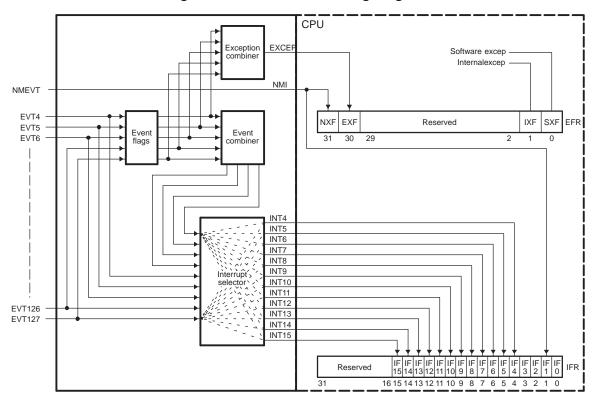

| 7-1.                   | C64x+ Megamodule Interrupt Controller Block Diagram                   | 157        |

| 7-2.                   | Event Flag Register Structure                                         | 158        |

| 7-3.                   | Event Clear Register Structure                                        | 159        |

| 7-4.<br>7-5.           | Event Set Register Structure                                          | 159        |

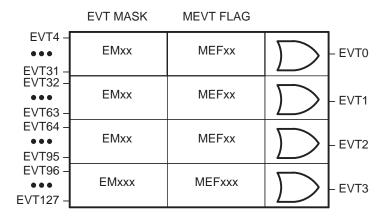

| 7-5.<br>7-6.           | Event Combiner                                                        | 160<br>160 |

| 7-0.<br>7-7.           | 32-Masked Event Flag Register Structure                               | 161        |

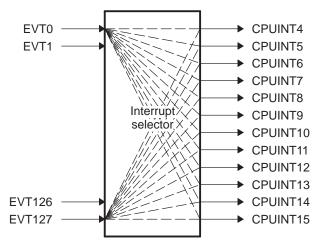

| 7-8.                   | Interrupt Selector Block Diagram                                      | 162        |

| 7-9.                   | CPU Interrupt Routing Diagram                                         | 162        |

| 7- <u>9</u> .<br>7-10. | Interrupt Exception Event Block Diagram                               | 163        |

| 7-10.<br>7-11.         | System Exception Routing Diagram                                      | 164        |

| 7-12.                  | Exception Mask Register Structure                                     | 164        |

| 7-13.                  | Masked Exception Flag Register Structure                              | 165        |

| 7-14.                  | CPU Event Routing Diagram                                             | 167        |

| 7-15.                  | Event Flag Register 0 (EVTFLAG0)                                      | 170        |

|                        |                                                                       |            |

8

| 7-16.          | Event Flag Register 1 (EVTFLAG1)                  | 17 |

|----------------|---------------------------------------------------|----|

| 7-17.          | Event Flag Register 2 (EVTFLAG2)                  |    |

| 7-18.          | Event Flag Register 3 (EVTFLAG3)                  |    |

| 7-19.          | Event Ag Register 0 (EVT EAGS)                    |    |

| 7-19.<br>7-20. | Event Set Register 1 (EVTSET0)                    |    |

| 7-20.<br>7-21. | Event Set Register 2 (EVTSET2)                    |    |

| 7-21.<br>7-22. | Event Set Register 3 (EVTSET3)                    |    |

| 7-22.          | Event Clear Register 0 (EVTCLR0)                  |    |

| 7-23.<br>7-24. | Event Clear Register 1 (EVTCLR0)                  |    |

| 7-24.          | Event Clear Register 2 (EVTCLR2)                  |    |

| 7-25.<br>7-26. | Event Clear Register 2 (EVTCLR2)                  |    |

| 7-20.          | Event Olean Register 3 (EVTOLR3)                  |    |

| 7-27.<br>7-28. | Event Mask Register 0 (EVTMASK0)                  |    |

| 7-20.<br>7-29. | Event Mask Register 1 (EVTMASK1)                  |    |

| 7-29.<br>7-30. | Event Mask Register 2 (EVTMASK2)                  |    |

|                |                                                   |    |

| 7-31.          | Masked Event Flag Register 0 (MEVTFLAG0)          |    |

| 7-32.          | Masked Event Flag Register 1 (MEVTFLAG1)          |    |

| 7-33.          | Masked Event Flag Register 2 (MEVTFLAG2)          |    |

| 7-34.          | Masked Event Flag Register 3 (MEVTFLAG3)          |    |

| 7-35.          | Interrupt Mux Register 1 (INTMUX1)                |    |

| 7-36.          | Interrupt Mux Register 2 (INTMUX2)                |    |

| 7-37.          | Interrupt Mux Register 3 (INTMUX3)                |    |

| 7-38.          | Interrupt Exception Status Register (INTXSTAT)    |    |

| 7-39.          | Interrupt Exception Clear Register (INTXCLR)      |    |

| 7-40.          | Dropped Interrupt Mask Register (INTDMASK)        |    |

| 7-41.          | Exception Combiner Mask Register 0 (EXPMASK0)     |    |

| 7-42.          | Exception Mask Register 1 (EXPMASK1)              |    |

| 7-43.          | Exception Mask Register 2 (EXPMASK2)              |    |

| 7-44.          | Exception Mask Register 3 (EXPMASK3)              |    |

| 7-45.          | Masked Exception Flag Register 0 (MEXPFLAG0)      |    |

| 7-46.          | Masked Exception Flag Register 1 (MEXPFLAG1)      |    |

| 7-47.          |                                                   |    |

| 7-48.          | Masked Exception Flag Register 3 (MEXPFLAG3)      |    |

| 7-49.          | Advanced Event Generator Mux Register 0 (AEGMUX0) |    |

| 7-50.          | Advanced Event Generator Mux Register 1 (AEGMUX1) |    |

| 8-1.           | Permission Fields                                 |    |

| 8-2.           |                                                   |    |

| 8-3.           | Memory Protection Fault Address Register (MPFAR)  |    |

| 8-4.           | Memory Protection Fault Status Register (MPFSR)   |    |

| 8-5.           | Memory Protection Fault Command Register (MPFCR)  |    |

| 8-6.           | Memory Protection Lock Register (MPLK0)           | 1  |

| 8-7.           | Memory Protection Lock Register (MPLK1)           | 1  |

| 8-8.           | Memory Protection Lock Register (MPLK2)           | 1  |

| 8-9.           | Memory Protection Lock Register (MPLK3)           | 1  |

| 8-10.          | Memory Protection Lock Command Register (MPLKCMD) | 1  |

| 8-11.          | Memory Protection Lock Status Register (MPLKSTAT) | 1  |

| 9-1.           | Power-Down Controller Command Register (PDCCMD)   | 2  |

| 10-1.          | Megamodule Revision ID Register (MM_REVID)        | 2  |

| 10-2.          | Bus Error Register (BUSERR)                       |    |

| 10-3. Bus Error Details Register (BUSERRCLR) | :10 |

|----------------------------------------------|-----|

|----------------------------------------------|-----|

# List of Tables

| 2-1.                                                                                                            | L1P Cache Registers Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-2.                                                                                                            | Cache Size Specified by the L1PMODE bit in the L1PCFG Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26                                                                                                                                                         |

| 2-3.                                                                                                            | Switching L1P Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27                                                                                                                                                         |

| 2-4.                                                                                                            | L1P Global Coherence Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29                                                                                                                                                         |

| 2-5.                                                                                                            | L1P Block Cache Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                                                                                                                                                         |

| 2-6.                                                                                                            | L1P Specific Cache Control Operations Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30                                                                                                                                                         |

| 2-7.                                                                                                            | L1P Configuration Register (L1PCFG) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31                                                                                                                                                         |

| 2-8.                                                                                                            | L1P Cache Control Register (L1PCC) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                                                                                                                         |

| 2-9.                                                                                                            | L1P Invalidate Base Address Register (L1PIBAR) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                                                                                                                                         |

| 2-10.                                                                                                           | L1P Invalidate Word Count Register (L1PIWC) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33                                                                                                                                                         |

| 2-11.                                                                                                           | L1P Invalidate Register (L1PINV) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33                                                                                                                                                         |

| 2-12.                                                                                                           | Permissions for L1P Cache Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34                                                                                                                                                         |

| 2-13.                                                                                                           | L1P Miss Pipelining Performance (Average Number of Stalls per Execute Packet)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                                                                                                                         |

| 2-14.                                                                                                           | Permission Bits Examined With Each Fetch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                                                                                         |

| 2-15.                                                                                                           | Memory Protection Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38                                                                                                                                                         |

| 2-16.                                                                                                           | Memory Page Protection Attribute Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                            |

| 2-17.                                                                                                           | Memory Page Protection Attribute Register (L1PMPPAx) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                            |

| 2-18.                                                                                                           | Memory Protection Lock Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |