## TMS320TCI648x DSP Bootloader

# **User's Guide**

Literature Number: SPRUEA7G June 2007–Revised June 2011

## Contents

| Prefa | ace      |                                                                                            |

|-------|----------|--------------------------------------------------------------------------------------------|

| 1     | Introduo | ction                                                                                      |

|       | 1.1      | Bootloader Features 9                                                                      |

|       | 1.2      | Terms and Abbreviations    9                                                               |

| 2     | TCI6482  | 2 Bootloader Operation 11                                                                  |

|       | 2.1      | Bootloader Initialization                                                                  |

|       | 2.2      | Boot Mode Selection                                                                        |

|       | 2.3      | Boot Mode Options 12                                                                       |

|       |          | 2.3.1 Direct Execution From External Asynchronous Memory - No Boot 12                      |

|       |          | 2.3.2 Host Boot Mode (HPI/PCI) 12                                                          |

|       |          | 2.3.2.1 PCI Auto-Initialization                                                            |

|       |          | 2.3.3 EMIFA Boot Mode 13                                                                   |

|       |          | 2.3.4 I2C EEPROM Boot Mode                                                                 |

|       |          | 2.3.4.1 I2C EEPROM Data Blocking 14                                                        |

|       |          | 2.3.4.2 TCI6482 Boot Parameter Structure                                                   |

|       |          | 2.3.5 I2C Slave Boot Mode                                                                  |

|       |          | 2.3.6 SRIO Boot Mode                                                                       |

|       | 2.4      | TCI6482 Bootloader Versions                                                                |

|       |          | 2.4.1 Determining the Bootloader Version                                                   |

| _     |          | 2.4.2 Differences Between Bootloader Versions                                              |

| 3     | TCI6484  | Bootloader Operation                                                                       |

|       | 3.1      | Bootloader Operation                                                                       |

|       | 3.2      | Boot Mode Selection                                                                        |

|       | 3.3      | Boot Mode Options 20                                                                       |

|       |          | 3.3.1 No Boot Mode                                                                         |

|       |          | 3.3.2 I2C Master Mode                                                                      |

|       |          | 3.3.2.1 I2C Boot Parameter Structure                                                       |

|       |          | 3.3.3 I2C Slave Boot Mode                                                                  |

|       |          | 3.3.4         HPI Boot Mode         23           3.3.5         EMIFA Boot Mode         25  |

|       |          | 3.3.5         EMIFA Boot Mode         25           3.3.6         EMAC Boot Mode         25 |

|       |          | 3.3.7 SRIO Boot Mode                                                                       |

|       |          | 3.3.7.1 SRIO Boot Parameter Structure                                                      |

|       | 3.4      | TCI6484 Bootloader Version                                                                 |

| 4     | -        | 6 Bootloader Operation                                                                     |

| 4     | 4.1      | Bootloader Operation                                                                       |

|       | 4.1      | Boot Mode Selection                                                                        |

|       |          |                                                                                            |

|       | 4.3      | Boot Mode Options         31           4.3.1         No Boot Mode         31               |

|       |          | 4.3.1 No Boot Mode                                                                         |

|       |          | 4.3.2 HPT BOOT Mode                                                                        |

|       |          | 4.3.3.1 I2C EEPROM Boot Mode                                                               |

|       |          | 4.3.3.2 I2C Boot Parameter Structure                                                       |

|       |          |                                                                                            |

3

| www | .ti.com |

|-----|---------|

|-----|---------|

|     |          | 4.3.4 UTOPIA Boot Mode 34                                                                                                          |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------|

|     |          | 4.3.4.1 UTOPIA Boot Parameter Structure                                                                                            |

|     |          | 4.3.5 EMAC Boot Mode                                                                                                               |

|     |          | 4.3.5.1 EMAC Boot Parameter Structure                                                                                              |

|     |          | 4.3.5.2 Ethernet-Ready Announcement Format                                                                                         |

|     |          | 4.3.5.3 EMAC Boot Table Frame Format                                                                                               |

|     |          | 4.3.6 SRIO Boot Mode                                                                                                               |

|     |          | 4.3.6.1 SRIO Boot Parameter Structure                                                                                              |

| _   | 4.4      | TCI6486 Bootloader Version                                                                                                         |

| 5   |          | 87/TCl6488 Bootloader Operation                                                                                                    |

|     | 5.1      | Bootloader Initialization                                                                                                          |

|     | 5.2      | Boot Mode Selection                                                                                                                |

|     | 5.3      | Boot Mode Options                                                                                                                  |

|     |          | 5.3.1 No Boot                                                                                                                      |

|     |          | 5.3.2 I2C EEPROM Boot Mode                                                                                                         |

|     |          | 5.3.2.1I2C EEPROM Data Blocking415.3.2.2I2C Boot Parameter Structure41                                                             |

|     |          | 5.3.2 EMAC Boot Mode                                                                                                               |

|     |          | 5.3.3.1 EMAC Boot Parameter Structure                                                                                              |

|     |          | 5.3.4 SRIO Boot Mode                                                                                                               |

|     |          | 5.3.4.1 SRIO Boot Parameter Structure                                                                                              |

|     | 5.4      | TCI6488 Bootloader Version                                                                                                         |

| 6   | -        | ng Boot Images                                                                                                                     |

| U   | 6.1      | Host/PCI Boot                                                                                                                      |

|     | 0.1      | 6.1.1 PCI Auto-Initialization                                                                                                      |

|     | <u> </u> |                                                                                                                                    |

|     | 6.2      | I2C Boot         46           6.2.1         Boot Parameter Table         46                                                        |

|     |          | 6.2.1       Boot Parameter Table       40         6.2.1.1       Boot Parameter Example for Setting Up Boot Table Download       46 |

|     |          | 6.2.1.2 Boot Parameter Example for Setting Up Boot Configuration Table Download                                                    |

|     |          | 6.2.2 Boot Table                                                                                                                   |

|     |          | 6.2.2.1 Boot Table Structure                                                                                                       |

|     |          | 6.2.2.2 Code and Data Sections in the Boot Table                                                                                   |

|     |          | 6.2.2.3 Creating the Boot Table                                                                                                    |

|     |          | 6.2.3 Boot Configuration Table 49                                                                                                  |

|     |          | 6.2.4 Creating the Combined EEPROM Image 50                                                                                        |

|     | 6.3      | EMAC Boot                                                                                                                          |

| 7   |          | bader Expansion                                                                                                                    |

|     | 7.1      | Second Stage Bootloader                                                                                                            |

|     | 7.2      | Boot to DDR2 Memory                                                                                                                |

|     | =        | 7.2.1 Create a Boot Table Mapped to DDR2 Memory                                                                                    |

|     |          | 7.2.2 Create a DDR2 Configuration Table                                                                                            |

|     |          | 7.2.3 Create the Combined EEPROM Image                                                                                             |

|     |          | 7.2.4 Perform the Boot Test                                                                                                        |

| App | endix A  | Revision History                                                                                                                   |

|     |          |                                                                                                                                    |

4

## List of Figures

| Signal Connections for I2C EEPROM Boot Mode                                        | 14                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program Flow for No-Boot Mode                                                      | 21                                                                                                                                                                                                                         |

| Boot Code Flow for HPI Boot Mode                                                   | 24                                                                                                                                                                                                                         |

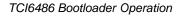

| Creating an I2C EEPROM Image Containing the Application Program                    | 50                                                                                                                                                                                                                         |

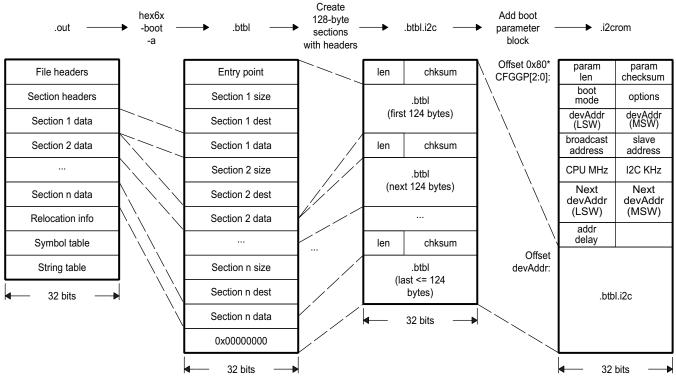

| Creating an I2C EEPROM Image Containing Boot Configuration and Application Program | 51                                                                                                                                                                                                                         |

| I2C Tables Illustration                                                            | 54                                                                                                                                                                                                                         |

|                                                                                    | Program Flow for No-Boot Mode<br>Boot Code Flow for HPI Boot Mode<br>Creating an I2C EEPROM Image Containing the Application Program<br>Creating an I2C EEPROM Image Containing Boot Configuration and Application Program |

## List of Tables

| 1  | TCI6482 Bootloader Initialization                   | 11 |

|----|-----------------------------------------------------|----|

| 2  | TCI6482 Cache Settings                              | 11 |

| 3  | Boot Mode Selection Options                         | 12 |

| 4  | I2C EEPROM Memory Layout                            | 13 |

| 5  | TCI6482 I2C EEPROM Block Format                     | 14 |

| 6  | TCI6482 I2C Boot Parameter Table                    | 15 |

| 7  | TCI6482 SRIO Boot Configurations                    | 17 |

| 8  | Differences Between TCI6482 Bootloader Versions     | 18 |

| 9  | TCI6484 Bootloader Initialization                   | 19 |

| 10 | L2 Memory Map for Bootloader Code                   | 19 |

| 11 | TCI6484 Boot Mode Selection                         | 20 |

| 12 | I2C Boot Parameter Block Format                     | 22 |

| 13 | TCI6484 Extended Boot Mode                          | 22 |

| 14 | Boot-Table Processing Status Values and Enumeration | 23 |

| 15 | EMAC Boot Configuration                             | 25 |

| 16 | TCI6484 EMAC Boot Parameter Structure               | 25 |

| 17 | TCI6484 SRIO Boot Configuration                     | 26 |

| 18 | TCI6484 SRIO Boot Parameter Block                   | 27 |

| 19 | TCI6486 Bootloader Initialization                   | 28 |

| 20 | TCI6486 Cache Settings                              | 28 |

| 21 | TCI6486 Boot Mode Selection                         | 30 |

| 22 | TCI6486 I2C EEPROM Common Block Format              | 33 |

| 23 | TCI6486 Extended Boot Mode                          | 33 |

| 24 | TCI6486 I2C Boot Parameter Table                    | 33 |

| 25 | UTOPIA Boot Parameter Table                         | 34 |

| 26 | TCI6486 EMAC Boot Parameter Table                   | 35 |

| 27 | EMAC Boot Table Frame Format                        | 37 |

| 28 | TCI6486 SRIO Boot Configurations                    | 38 |

| 29 | TCI6486 SRIO Boot Parameter Table                   | 38 |

| 30 | TCI6488 Bootloader Initialization                   | 39 |

| 31 | TCI6488 Cache Settings                              | 39 |

| 32 | L2 Memory Map for Bootloader Code                   | 40 |

| 33 | TCI6488 Boot Mode Selection                         | 40 |

| 34 | TCI6488 I2C EEPROM Common Block Format              | 41 |

| 35 | TCI6488 Extended Boot Mode                          | 41 |

| 36 | TCI6488 I2C Boot Parameter Table                    | 41 |

| 37 | TCI6488 EMAC Boot Parameter Table                   | 42 |

| 38 | TCI6488 SRIO Boot Configurations                    | 44 |

| 39 | TCI6488 SRIO Boot Parameter Table                   | 44 |

|    |                                                     |    |

| 40 | Differences Between TCI6488 Bootloader Versions          | 45 |

|----|----------------------------------------------------------|----|

| 41 | Boot Parameter Table Example for Boot Table Load         | 47 |

| 42 | Boot Parameter Table Example for Boot Configuration Load | 47 |

| 43 | Boot Configuration Table Example                         | 49 |

| 44 | TCI648x Bootloader Revision History                      | 57 |

## **Read This First**

#### About This Manual

This document describes the features of the on-chip bootloader provided with the following TMS320TCI648x Digital Signal Processors (DSPs): TCI6482, TCI6484, TCI6486, TCI6487, and TCI6488 .

This document contains preliminary data current as of the publication date and is subject to change without notice.

#### Important Notice Regarding Bootloader Program Contents:

Texas Instruments may periodically update the bootloader code supplied in the ROM to correct known problems, provide additional features or improve functionality. These changes may be made without notice as needed. Although changes to the ROM code preserve functional compatibility with prior versions, the locations of functions within the main bootloader code may change. You should avoid calling these functions directly as the code may change in the future.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320C6000<sup>™</sup> devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at <u>www.ti.com</u>.

- SPRU732 TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

- SPRU198 TMS320C6000 Programmer's Guide. Describes ways to optimize C and assembly code for the TMS320C6000<sup>™</sup> DSPs and includes application program examples.

- SPRU871 TMS320C64x+ Megamodule Reference Guide. Describes the TMS320C64x+ digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

- <u>SPRUE11</u> TMS320TCI648x DSP Inter-Integrated Circuit (I2C) Module User's Guide. This document describes the inter-integrated circuit (I2C) module in the TMS320TCI648x digital signal processors (DSPs).

- <u>SPRUE69</u> *TMS320TCI648x DSP Peripheral Component Interconnect (PCI) User's Guide.* This document describes the peripheral component interconnect (PCI) port in TMS320TCI648x devices.

TMS320C6000, Code Composer Studio are trademarks of Texas Instruments. RapidIO is a registered trademark of RapidIO Trade Association. All other trademarks are the property of their respective owners.

## TMS320TCI648x Bootloader

### 1 Introduction

This section provides a description of the features of the on-chip bootloader provided with the following TMS320TCI648x Digital Signal Processors (DSPs): TCI6482, TCI6484, TCI6486, TCI6487, and TCI6488.

This document should be used in conjunction with the device-specific data manuals and user's guides for peripherals used during the boot. This document covers non-secure booting only.

#### 1.1 Bootloader Features

The bootloader is DSP code that transfers application code from an external source into internal or external program memory after the DSP is taken out of reset. The bootloader allows application code to reside in slow non-volatile external memory and be transferred to high-speed internal memory for execution, or to be transferred from a host processor to the DSP after the DSP is taken out of reset. The bootloader is permanently stored in the ROM of the DSP starting at byte address 0x00100000 for TCI6482 and TCI6486 devices, 0x3C000000 for TCI6484, TCI6487, and TCI6488 devices.

To accommodate different system requirements, the bootloader offers a variety of methods (boot modes) to transfer the application into DSP memory. The following is a list of the available boot modes and a summary of their functional operation:

- Direct execution from internal memory (L2), No boot: The CPU executes directly out of L2 (operation is invalid if there is no valid code in L2). Typically only used during debug on emulator.

- Host boot (HPI/PCI): In this mode, the bootloader waits until the code to be executed is loaded into on-chip memory by a host device via the HPI or the PCI. Code execution begins when the host indicates to the bootloader that the application has been loaded.

- EMIF boot from 8-bit external asynchronous memory: The code executes out of external memory.

- Master I2C boot: The application is loaded from an I2C EEPROM, one section at a time, using a boot table to determine the length and the starting address for each section.

- Slave I2C boot: An external I2C master sends the application to the DSP, also using a boot table.

- Serial RapidIO<sup>®</sup> (SRIO) boot: An external host loads the application via the SRIO peripheral, using directIO protocol. A doorbell interrupt is used to indicate that the code has been loaded.

- EMAC boot: An external host loads the application via EMAC peripheral.

- UTOPIA boot: An external host loads the application via UTOPIA peripheral.

#### 1.2 Terms and Abbreviations

1X mode — 1 Tx and 1 Rx differential pair

**CPPI** — Communications Port Programming Interface

DDR2 — Double Data Rate 2

**DIX** — Digital, Intel, and Xerox

DSK — Developer Starter Kit

**EEPROM** — Electrically Erasable Programmable ROM

EMAC — Ethernet Media Access Control

**EMIF** — External Memory Interface

9

- GEL Gain Extension Language used in Code Composer Studio™

- **GMII** Gigabit Media Independent Interface

- HPI Host Port Interface

- I2C Inter-Integrated Circuit

- L2 Level 2

- MAC Media Access Control

- MII Media Independent Interface

- PCI Peripheral Component Interconnect

- PDMA Packet Direct Memory Access

- PHY Physical Layer Device

- RMII Reduced Media-Independent Interface

- SERDES Serializer/Deserializer

- S3MII Source Synchronous Serial Media Independent Interface

- SGMII Serial Gigabit Media Independent Interface

- SMII Serial Media Independent Interface

- SRIO Serial RapidIO

- UTOPIA Universal Test and Operations Physical Interface for ATM

### 2 TCI6482 Bootloader Operation

The structure and operation of the TCI6482 bootloader are described in the following sections.

### 2.1 Bootloader Initialization

When the bootloader begins execution, the program performs some initialization of the DSP prior to loading code. Table 1 describes the DSP resources that are configured by the bootloader. Table 2 lists the cache settings while L2 cache is always disabled.

| Resource                                                                                                                                                                                                                                                       | Initialization Value                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Interrupts                                                                                                                                                                                                                                                     | Interrupts are left enabled (GIE=1). PCI and SRIO boot interrupts are enabled, with the interrupt mux registers configured to route the PCI and SRIO interrupts to the core. ISTP (the vector table pointer) is set to point into the ROM at 0x103c00. After the interrupt arrives, the ISTP and interrupt mux registers are restored to their default values. |  |  |  |

| Memory                                                                                                                                                                                                                                                         | L2 Memory from 0x9ff080 to 0x9fffff is reserved during the boot and can be reclaimed by application after the boot.                                                                                                                                                                                                                                            |  |  |  |

| PLL1 Controller For SRIO and PCI boot, the bootloader configures the PLL1 Controller such that CLKIN1 is multiplic<br>For all other boot modes, the PLL1 Controller is in Bypass mode. The PLL1 Controller configuration<br>changed when the bootloader exits. |                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Peripheral Powerup                                                                                                                                                                                                                                             | Peripherals are enabled as required by the bootloader in the selected mode. Peripherals are not disabled when the bootloader exits.                                                                                                                                                                                                                            |  |  |  |

| Registers                                                                                                                                                                                                                                                      | The state of all CPU registers, with the exception of the PC, must be considered random on bootloader exit.                                                                                                                                                                                                                                                    |  |  |  |

#### Table 1. TCI6482 Bootloader Initialization

| BOOTMODE[3:0] | Boot Description | L1P/L1D Cache Settings                                                                                                                                                      |

|---------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | No boot          | If PCI_EEAI = 1, 0 KB<br>If PCI_EEAI = 0, 32 KB by default. However, without valid code in L2, PC<br>may branch into the ROM and cache defaults settings may be overwritten |

| 1             | HPI/PCI boot     | 32KB                                                                                                                                                                        |

| 2             | EMIFA fast boot  | 32KB                                                                                                                                                                        |

| 3             | Reserved         | N/A                                                                                                                                                                         |

| 4             | EMIFA ROM boot   | 32KB                                                                                                                                                                        |

| From 5 to 15  | Other boots      | 0 KB                                                                                                                                                                        |

#### Table 2. TCI6482 Cache Settings

After the initialization is performed, the bootloader loads the on-chip RAM according to the boot mode selected, and then causes the DSP to begin execution of the loaded code. At that point, the boot load process is complete. Whenever the DSP is reset, the CPU starts execution of the bootloader again, and the entire boot load process is repeated.

The following sections describe the various TCI6482 boot modes and boot tables in detail.

#### 2.2 Boot Mode Selection

The desired boot mode is selected by setting the four boot mode select pins BOOTMODE[3:0], which are sampled during reset. The BOOTMODE pins are shared with EMIFA address pins [19:16].

Table 3 describes the available boot mode options and their corresponding BOOTMODE pin configurations.

| BOOTM3 | BOOTM2 | BOOTM1 | BOOTM0 | Boot Mode Source                                         | See           |

|--------|--------|--------|--------|----------------------------------------------------------|---------------|

| 0      | 0      | 0      | 0      | No boot, execution begins from the base of L2 (0x800000) | Section 2.3.1 |

| 0      | 0      | 0      | 1      | Host boot (HPI)                                          | Section 2.3.2 |

| 0      | 0      | 1      | 0      | Reserved                                                 | -             |

| 0      | 0      | 1      | 1      | Reserved                                                 | -             |

| 0      | 1      | 0      | 0      | EMIFA ROM boot                                           | Section 2.3.4 |

| 0      | 1      | 0      | 1      | Master I2C boot                                          | Section 2.3.4 |

| 0      | 1      | 1      | 0      | Slave I2C boot                                           | Section 2.3.5 |

| 0      | 1      | 1      | 1      | Host boot (PCI)                                          | Section 2.3.2 |

| 1      | Х      | 0      | 0      | Serial RapidIO boot, Configuration 0 (4 1x ports)        | Section 2.3.6 |

| 1      | х      | 0      | 1      | Serial RapidIO boot, Configuration 1 (1 4x port)         | Section 2.3.6 |

| 1      | х      | 1      | 0      | Serial RapidIO boot, Configuration 2 (1 4x port)         | Section 2.3.6 |

| 1      | х      | 1      | 1      | Serial RapidIO boot, Configuration 3 (1 4x port)         | Section 2.3.6 |

#### **Table 3. Boot Mode Selection Options**

#### 2.3 Boot Mode Options

#### 2.3.1 Direct Execution From External Asynchronous Memory - No Boot

When BOOTMODE[3:0] = 0000b, the no boot option is selected. In this mode, the bootloader program does not execute. The DSP begins execution at the base of internal L2 memory at byte address 0x800000.

#### 2.3.2 Host Boot Mode (HPI/PCI)

In host boot mode, an external host can load code and data directly into the DSP memory while the CPU waits. Host boot does not use a boot table. The code and/or data sections are directly loaded to the desired locations by the host. When the host has finished loading the application, it generates a host interrupt (HPI or PCI), the CPU then begins executing at the base of L2.

An HPI host can use the DSPINT bit of the Host Port Interface Control register (HPIC) to generate an interrupt to the CPU while a PCI host can use the DSPINT bit of the PCI Status Set register (PCISTATSET). In the case of PCI, the DSPINT bit of the Back End Application Interrupt Enable register must also be set to 1.

If PCI boot is selected, the bootloader configures the PLL1 Controller such that CLKIN1 is multiplied by 15. More specifically, PLLM is set to 0Eh (x15) and RATIO is set to 0 (÷1) in the PLL1 Multiplier Control register (PLLM) and PLL1 Pre-Divider register (PREDIV), respectively.

#### 2.3.2.1 PCI Auto-Initialization

If PCI auto-initialization through I2C EEPROM is enabled through the PCI\_EEAI configuration pin, regardless of the selected boot mode, the on-chip bootloader also powers-on the PCI and I2C peripherals, initializes the I2C interface, and reads the PCI configuration values and a 16-bit checksum from an I2C EEPROM (starting at I2C address 0x400). Table 4 shows the register layout in I2C EEPROM. If the checksum verification passes, the bootloader writes the values read from I2C EEPROM into the appropriate PCI Hook Configuration registers and PCI Back End Configuration registers (back end registers written to only after power-on reset). Additional details about auto-initialization and PCI reset can be found in the *TMS320TCI648x Peripheral Component Interconnect (PCI) Interface User's Guide* (SPRUE69).

| Byte Address | Contents                   |

|--------------|----------------------------|

| 0x400        | Vendor ID [15:8]           |

| 0x401        | Vendor ID [7:0]            |

| 0x402        | Device ID [15:8]           |

| 0x403        | Device ID [7:0]            |

| 0x404        | Class code [7:0]           |

| 0x405        | Revision ID [7:0]          |

| 0x406        | Class code [23:16]         |

| 0x407        | Class code [15:8]          |

| 0x408        | Subsystem vendor ID [15:8] |

| 0x409        | Subsystem vendor ID [7:0]  |

| 0x40a        | Subsystem ID [15:8]        |

| 0x40b        | Subsystem ID [7:0]         |

| 0x40c        | Max_Latency                |

| 0x40d        | Min_Grant                  |

| 0x40e        | Reserved (use 0x00)        |

| 0x40f        | Reserved (use 0x00)        |

| 0x410        | Reserved (use 0x00)        |

| 0x411        | Reserved (use 0x00)        |

| 0x412        | Reserved (use 0x00)        |

| 0x413        | Reserved (use 0x00)        |

| 0x414        | Reserved (use 0x00)        |

| 0x415        | Reserved (use 0x00)        |

| 0x416        | Reserved (use 0x00)        |

| 0x417        | Reserved (use 0x00)        |

| 0x418        | Reserved (use 0x00)        |

| 0x419        | Reserved (use 0x00)        |

| 0x41a        | Checksum [15:8]            |

| 0x41b        | Checksum [7:0]             |

|              |                            |

| Table 4. I2C EEPROM | Memory Layout |

|---------------------|---------------|

|---------------------|---------------|

#### 2.3.3 EMIFA Boot Mode

In EMIFA boot mode, the bootloader simply branches to the base address of EMIFA CE3 (0xB000 0000). Interrupts are disabled.

TCI6482 Bootloader Operation

#### 2.3.4 I2C EEPROM Boot Mode

This section assumes familiarity with the I2C operation using the master receiver and master transmitter modes. For detailed information on the I2C, see the *TMS320TCI648x DSP Inter-Integrated Circuit (I2C) Module User's Guide* (SPRUE11).

The bootloader supports boot from I2C EEPROMs or devices operating as I2C slaves that emulate the appropriate format. The bootloader has the following requirements for the I2C EEPROMs:

- The memory device complies with Philips I2C Bus Specification v 2.1.

- The memory device uses two bytes for internal addressing.

- The memory device has the capability to auto-increment its internal address counter such that the contents of the memory device can be read sequentially.

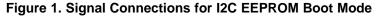

In I2C boot mode, the DSP acts as the master and the I2C EEPROM acts as the slave. Figure 1 shows the minimum connection required between the DSP and one I2C EEPROM. The required pull-ups must be placed on SDA and SCL to ensure that the I2C EEPROM interface works correctly.

Some I2C EEPROMs have a write-protect (WP) feature that prevents unauthorized writes to memory. This feature is not needed for boot loading purposes because the DSP only reads data from the I2C EEPROMs. The write protect feature can be enabled or disabled without impacting bootloader operation.

The bootloader requires the I2C EEPROM slave address to be 0x50. Other EEPROM slave addresses can then be used as specified in the boot parameter table loaded from the initial EEPROM.

The frequency of the I2C bus is initially set to CLKIN1/6600. For example, with a CLKIN1 frequency of 50 MHz, the serial clock frequency would be set to 7.57 kHz. Subsequently, the bootloader reads the actual CPU frequency and desired I2C frequency values from boot parameters (see Table 6) and reprograms the I2C.

#### 2.3.4.1 I2C EEPROM Data Blocking

All data stored on the I2C EEPROM are stored in blocks. Each block has a maximum length of 128 bytes, including the 4 byte block header. Table 5 shows the format of the block.

| Offset (bytes) | Size (bytes) | Name       | Value                                                                                                            |

|----------------|--------------|------------|------------------------------------------------------------------------------------------------------------------|

| 0              | 2            | Block size | The size of the block, including the header.                                                                     |

| 2              | 2            | Checksum   | The ones complement check sum, including the block size and checksum fields. Valid checksum values are 0 and -0. |

| 4-126          | 0-124        | Data       | Data                                                                                                             |

#### Table 5. TCI6482 I2C EEPROM Block Format

The bootloader reads data from the I2C EEPROM in blocks. If the checksum shows a failure, the block is re-read until the checksum is valid. A value of 0 in the checksum field disables the checksum check.

#### 2.3.4.2 TCI6482 Boot Parameter Structure

The I2C boot sequence begins with the DSP reading a block of boot parameters from the I2C EEPROM. The boot parameter table complies with I2C EEPROM data blocking format. The boot parameters begin at EEPROM address 0, and a boot parameter block consists of 128 bytes. The DSP calculates the address of boot parameter block to load based on the value of the CFGGP[2:0] bits of the Device Status Register (DEVSTAT) as follows: address = 0x80 \* CFGGP[2:0]. This allows the DSP to read one of eight possible boot parameter blocks. The values in this block determine how the boot process proceeds. Table 6 shows the structure of these boot parameters. Each value is 2 bytes, and the bytes must be stored in big endian format (most significant byte at the lowest address), regardless of the endianness setting of the processor. The structure has a total length of 26 bytes.

| Offset (byte) | Field                     | Value                                                                                                                                                                |                                                                                                                                                                                       |  |  |

|---------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4             | Boot mode                 | The boot mode                                                                                                                                                        | e that is used by the bootloader                                                                                                                                                      |  |  |

|               |                           | 0x0-0xF                                                                                                                                                              | See Table 3.                                                                                                                                                                          |  |  |

|               |                           | 0x100                                                                                                                                                                | I2C Master Write (extended mode)                                                                                                                                                      |  |  |

| 6             | Options                   | I2C options:                                                                                                                                                         |                                                                                                                                                                                       |  |  |

|               |                           | Bits 01-00                                                                                                                                                           | Boot table type                                                                                                                                                                       |  |  |

|               |                           | 00                                                                                                                                                                   | Boot parameter mode                                                                                                                                                                   |  |  |

|               |                           | 01                                                                                                                                                                   | Boot table mode                                                                                                                                                                       |  |  |

|               |                           | 10                                                                                                                                                                   | Boot configuration mode                                                                                                                                                               |  |  |

|               |                           | 11                                                                                                                                                                   | Slave receive boot                                                                                                                                                                    |  |  |

|               |                           | Bits 04-02                                                                                                                                                           | EEPROM type                                                                                                                                                                           |  |  |

|               |                           | 00                                                                                                                                                                   | 24C00 to 24C16A                                                                                                                                                                       |  |  |

|               |                           | 01                                                                                                                                                                   | 24C32 to 24C1024                                                                                                                                                                      |  |  |

|               |                           | 10                                                                                                                                                                   | 24CW256                                                                                                                                                                               |  |  |

|               |                           | 11                                                                                                                                                                   | Reserved                                                                                                                                                                              |  |  |

| 8             | Device address (LSW)      | For further I2C boot, the lower 16 bits of the address in the I2C EEPROM                                                                                             |                                                                                                                                                                                       |  |  |

| 10            | Device address (MSW)      | For further I2C boot, the upper 16 bits of the address in the I2C EEPROM. This is an abstraction; this value is used as the I2C EEPROM slave address (default 0x50). |                                                                                                                                                                                       |  |  |

| 12            | Broadcast address         | If the boot mode is master broadcast, the boot tables are read from the I2C EEPROM and are re-sent to this slave address (default 0x0).                              |                                                                                                                                                                                       |  |  |

| 14            | Slave address             | The address used by the DSP as its local slave address                                                                                                               |                                                                                                                                                                                       |  |  |

| 16            | CPU frequency (MHz)       | This parameter                                                                                                                                                       | U frequency as measured from SYSREFCLK of the PLL1 Controller.<br>r configures the I2C clock. Note that the PLL1 Controller is<br>y the bootloader for some boot modes (see Table 1). |  |  |

| 18            | I2C clock frequency (kHz) | The desired I2C serial clock frequency                                                                                                                               |                                                                                                                                                                                       |  |  |

| 20            | Next device address (LSW) | If options indicate a boot configuration table load, this address is used as the address in the I2C ROM to find the next boot parameter table to load.               |                                                                                                                                                                                       |  |  |

| 22            | Next device address (MSW) | The upper 16 bits of the address, used as the slave address of the I2C EEPROM                                                                                        |                                                                                                                                                                                       |  |  |

| 24            | Address delay             | Delay between                                                                                                                                                        | address write and read from I2C EEPROM (in cycles)                                                                                                                                    |  |  |

#### Table 6. TCI6482 I2C Boot Parameter Table

The two LSBs of the options field (offset 6 bytes) define what the bootloader expects to find in the I2C EEPROM at the offset specified by the Device Address (LSW), and how it should proceed. A value of 0 indicates another boot parameter table. A value of 1 indicates a boot table (i.e., a table which contains initialized code and data sections, see Section 6.2.2). A value of 2 indicates a boot configuration table (table used to configure registers, see Section 6.2.3). A value of 3 is reserved, and the remaining bits must be set to 0.

After the DSP reads and remembers the boot parameter table, the bootloader performs a boot re-entry. On this pass the code executes based on the values provided by the boot parameter table.

If the options indicate a boot table is loading, then the bootloader reads from the I2C EEPROM address specified in the boot table until the end of the table is reached (i.e., until all code and data sections are loaded), and immediately begin execution of the loaded code by branching to the entry point specified at the beginning of the boot table (see Section 6.2.2.1).

#### TCI6482 Bootloader Operation

www.ti.com

If the options indicate a boot configuration table is loading, then the bootloader reads from the specified I2C EEPROM address until the end of the boot configuration table. This typically initializes various registers (see Section 6.2.3). The next device address previously read from the boot parameter block is copied into device address, the boot options are cleared, and the bootloader performs a boot re-entry. This directs the ROM to read the I2C EEPROM at the specified device address, which should have another boot parameter table.

#### 2.3.5 I2C Slave Boot Mode

In the I2C slave boot mode, the DSP is programmed as an I2C slave and waits for an I2C Master to send data, using a standard boot table format.

The procedure is the same as Section 2.3.4, except for how the DSP receives data. In this case, rather than performing a master address write followed by a master data read, the DSP configures its I2C interface for slave reads, its device address to the default slave address (0x4), and polls for receiver ready, reading one byte at a time.

This boot mode can be used when it is desired to boot multiple DSPs at the same time from the same I2C EEPROM. One DSP is configured for I2C Master Write (in the Options boot parameters field), and the remaining DSPs are configured for I2C slave boot mode. The slave DSPs come out of reset first, followed by the master DSP. The master DSP reads from I2C EEPROM and re-transmits to the broadcast address (default 0x4). Therefore, all DSPs boot at the same time. In some cases, if in the design, another I2C master is booting the slave TCI6482 DSP through the I2C. Then, the I2C master needs to act similarly to a TCI6482 DSP during I2C boot. First, the I2C bus on the master side needs to be configured to have the exact same frequency as the I2C module within the DSP. Second, the I2C master needs to send 6 bytes (count does not include slave address) to the slave DSP before sending the boot table:

04 xx xx yy yy zz zz

Where:

04 = the slave address for the TCI6482 DSP in slave I2C boot mode

xx xx = length

yy yy = checksum

zz zz = boot option

For example:

04 00 06 00 00 00 01 - Order: slave address, length, checksum, boot option

Length = 6

Checksum = 0 (not used)

Boot option = 1 (for telling the slave DSP that the next coming data is the boot table); for other options, see the Options field in Table 6.

#### 2.3.6 SRIO Boot Mode

In the SRIO boot mode, an external host can load code and data directly into the DSP memory while the CPU waits, similar to the HPI/PCI boot mode. The code and/or data sections are directly loaded to the desired locations, using the directIO model. When the host has finished loading the application, it signals through a doorbell interrupt and the CPU then begins executing at the base of L2.

The on-chip bootloader first configures the PLL1 Controller such that CLKIN1 is multiplied by 15. It then determines the SRIO boot configuration (0, 1, 2 or 3) and initializes and enables required blocks of the SRIO peripheral.

The SRIO boot configuration is determined by the BOOTMODE[1:0] pins (see Table 3). In boot configuration 0, the SRIO peripheral is configured as four 1x ports and the boot is performed on port 0. In the remaining configurations, the SRIO peripheral is configured as a single 1x/4x port.

The logical layer local device ID within the Serial RapidIO network is configured using BOOTMODE[2] as the address MSB and configuration pins CFGGP[2:0] as the three LSBs. If BOOTMODE[2]:CFGGP[2:0] is 0b1111, the default value of the device ID is 0xFF or 0xFFFF, and it must be configured/assigned by the host (maintenance packet to DEVICEID\_REG1); otherwise, device ID = 2 + BOOTMODE[2]:CFGGP[2:0].

In the SRIO boot configuration 0, the bootloader configures the SRIO peripheral in the following sequence:

- 1. Peripheral blocks (registers BLK*n*\_EN, GBL\_EN): Blocks 0, 1, 2 and 5 are enabled (MMRs, LSU, MAU and Port 0, respectively). Global enable is also set.

- 2. PLL (register CFG0\_CNTL): Multiplier is set to 10x, loop bandwidth to 1/12th of the reference clock, and the PLL is enabled. A delay of 1usec follows PLL enabling.

- 3. Receiver (registers CFGRX*n*\_CNTL): Half rate, 10-bit width, set comma aligned, set normal polarity, etc.

- 4. Transmitter (registers CFGTX*n*\_CNTL): Half rate, 10-bit width, set common mode, set output swing, set emphasis, set normal polarity, etc.

- 5. Processing Element Feature CAR (register PE\_FEAT): 34-bit address, extended features pointer valid; common transport large systems support.

- 6. Source/Destination Operations CAR (registers SRC\_OP, DEST\_OP): All source operations, all destination operations, except atomic.

- 7. Maintenance block header (register SP\_MB\_HEAD): General endpoint device with software assisted error recovery.

- 8. Input/Output Port Enable (registers SPn\_CTL).

- 9. Base ID: Same as the local Device ID.

- 10. IP-Level Port Mode (register SP\_IP\_MODE): 4 ports (1x mode each), Port-Write disabled, Packet accepted by the Phy layer with any DestID and forwarded to the logical layer.

- 11. Packet Forwarding (registers PF\_16B\_CNTL*n*, PF\_8B\_CNTL*n*): Disabled.

- 12. Doorbell interrupt routing (register DOORBELL0\_ICRR): Routed to INTDST4.

- 13. Prescaler for physical layer timers (register IP\_PRESCAL): 333 MHz.

- 14. Check Port OK: Continue if the port is initialized and is exchanging error-free control symbols with the attached device; otherwise, record an error in setting up the peripheral.

- 15. Boot Complete (register SP\_PER\_SET\_CNTL): Writes to read-only registers are disabled after this point.

- 16. Assert Peripheral Enable (PCR register) to enable logical layer data flow.

- 17. Clear any pending interrupts (register ICRR).

Registers not mentioned above retain their default values.

In the SRIO boot configurations 1-3, the initialization is the same as in SRIO boot configuration 0, except for the registers that configure the SERDES ports.

Table 7 lists the required SerDES reference clock and associated link rate settings.

#### Table 7. TCI6482 SRIO Boot Configurations

| Boot Configuration        | SerDes Reference Clock | SRIO Link Rate |

|---------------------------|------------------------|----------------|

| SRIO boot configuration 0 | 125 MHz                | 1.25 Gbps      |

| SRIO boot configuration 1 | 156.25 MHz             | 3.125 Gbps     |

| SRIO boot configuration 2 | 125 MHz                | 3.125 Gbps     |

| SRIO boot configuration 3 | 312.5 MHz              | 3.125 Gbps     |

#### 2.4 TCI6482 Bootloader Versions

#### 2.4.1 Determining the Bootloader Version

The boot ROM can be identified by reading the ROM signature. The ROM address may very from one bootloader address to the next (see Table 8). The signature is a string of characters, stored one byte per 32 bit word. If the ROM boot executes this signature is copied as a packed byte string (order depends on the endianness configuration) to L2 at 0x9ff040.

#### 2.4.2 Differences Between Bootloader Versions

Different versions of the on-chip bootloader exit on silicon revision 1.1 and 2.0 of the TCI6482 DSP. Table 8 summarizes the differences between two versions.

#### Feature TCI6482 Silicon Revision 1.1 TCI6482 Silicon Revision 2.0 Signature v2.2 Wed Jul 27 17:25:44 2005 v2.3 Wed Feb 01 13:37:24 2006 i2c pci\_eeai Serial RapidIO i2c pci\_eeai Serial RapidIO Starting address of the 0x103aa0 0x103b30 signature string in ROM I2C address delay Not programmable Programmable (see Table 6) SRIO PLL Function not available to second stage bootloaders Function available to second stage bootloaders or boot configuration tables and boot configuration tables EMIF boot EMIF boot with PCI auto-initialization enabled is EMIF boot with PCI auto-initialization enabled is not supported supported SERDES in SRIO boot Only SERDES 0 configured All SERDES (0-3) configured configuration 0 Default I2C frequency 15\*(CLKIN1/6600) if PCI auto-initialization is CLKIN1/6600 enabled, CLKIN1/6600 otherwise (see Section 2.3.4)

#### Table 8. Differences Between TCI6482 Bootloader Versions

#### 3 TCI6484 Bootloader Operation

This section describes the structure and operation of the TCI6484 bootloader. The bootloader code is executed in the L3 ROM. All boot modes on TCI6484 are ROM based; i.e., execution is transferred to the L3 ROM base when the DSP is released from reset and, depending on the boot pins strapped, the relevant boot mode is executed.

### 3.1 Bootloader Operation

When the bootloader begins execution, the program performs some DSP initialization prior to loading the code. Table 9 describes the DSP resources that are configured by the bootloader.

| Resource           | Initialization Value                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupts         | Interrupts are left disabled (GIE=0) except for NO BOOT, HPI, and SRIO boot modes. When interrupts are enabled, the interrupt mux registers are configured to route the correct system event to the core. ISTP (vector table pointer) is set to point to the start of L3 ROM (0x3C000000) and the IER mask is set to enable the correct interrupts (Reset and NMI interrupts are always enabled). After interrupt, the ISTP and GIE are restored to their default values. |

| Memory             | L1P/L1D is set to all cache. L2 memory from byte address 0x009FA000 - 0x009FFFFF (20480 bytes) is reserved for use as scratch memory during the boot process and can be reclaimed by the application after the boot.                                                                                                                                                                                                                                                      |

| PLL1 Controller    | For I2C, HPI, SRIO, and MAC boot modes, the PLL1 is set to x16 mode.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Peripheral Powerup | Peripherals are powered up as required by the bootloader in the selected mode. Peripherals are not powered down when the bootloader exits. HPI, EMAC, and EMIFA modules need to be powered on.                                                                                                                                                                                                                                                                            |

| Registers          | The state of all CPU registers, with the exception of PC, must be considered random on bootloader exit.                                                                                                                                                                                                                                                                                                                                                                   |

| Table 9. TCI6484 Bootloader Initial | ization |

|-------------------------------------|---------|

|-------------------------------------|---------|

L2 is configured as RAM only (no cache). The boot code uses a portion of L2 during the boot process (see the shaded area in Table 10). When the boot is complete, the application can reclaim this reserved memory.

| Memory Range        | Size (bytes) | Description                                                                                                                                                     |

|---------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x800000 - 0x9F9FFF |              | Not used by boot code. Application can use this space to download code and data sections.                                                                       |

| 0x9FA000 - 0x9FDFFF | 16K          | Allocated for storing received EMAC packets. In addition, it is used to store SRIO and HPI boot packets when boot table processing is selected for these modes. |

| 0x9FE000 - 0x9FE7FF | 2K           | Allocated as stack by boot code.                                                                                                                                |

| 0x9FE800 - 0x9FE8FF | 256          | Used by boot code to store boot parameters.                                                                                                                     |

| 0x9FE900 - 0x9FEAFF | 512          | Allocated for un-initialized data structures used by the boot code.                                                                                             |

| 0x9FEB00 - 0x9FFAFF | 4K           | Used for boot table processing by the boot code                                                                                                                 |

| 0x9FFB00 - 0x9FFBFF | 256          | Boot version string                                                                                                                                             |

| 0X9FFC00 - 0x9FFDFF | 512          | Boot Statistics/diagnostics                                                                                                                                     |

| 0X9FFF00 - 0x9FFF0F | 16           | Boot ROM table pointers                                                                                                                                         |

| 0X9FFFFC - 0x9FFFFF | 4            | Application entry point (boot exit address)                                                                                                                     |

#### Table 10. L2 Memory Map for Bootloader Code

#### 3.2 Boot Mode Selection

The boot mode is selected by setting the boot mode pins BOOTMODE[3:0], which are latched during reset. The configuration pins GPIO[13:9] are mapped to CFGGP[4:0] which are are referred to as CFG[3:0] in Table 11 and throughout this chapter for the TCI6484 device.

| BOOTMODE[3:0] | Description                      | CFG[3:0]                                                          | See           |

|---------------|----------------------------------|-------------------------------------------------------------------|---------------|

| 0             | No boot                          | None                                                              | Section 3.3.1 |

| 1             | I2C Master (device address 0x50) | First EEPROM boot parameter block<br>address                      | Section 3.3.2 |

| 2             | I2C Master (device address 0x51) | First EEPROM boot parameter block<br>address                      | Section 3.3.2 |

| 3             | I2C Slave                        | 3:0 + 1= Device ID                                                | Section 3.3.3 |

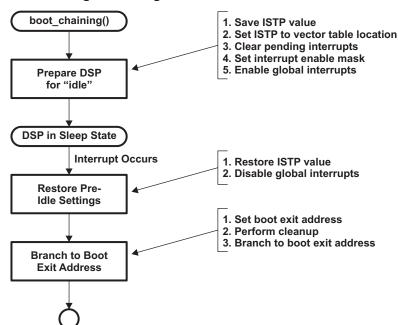

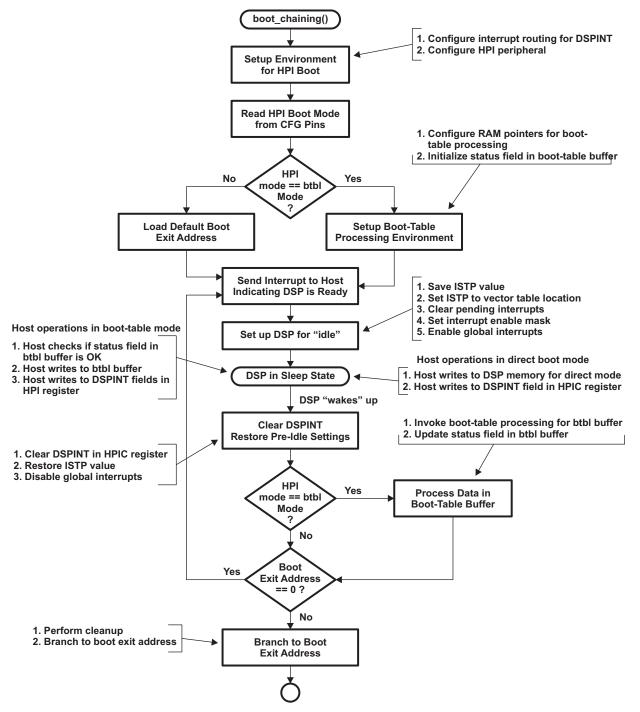

| 4             | HPI                              | 3:0 = 2 boot table loading mode,<br>otherwise direct loading mode | Section 3.3.4 |

| 5             | EMIFA                            | None                                                              | Section 3.3.5 |

| 6             | EMAC Master                      | 3:0 Device ID                                                     | Section 3.3.6 |

| 7             | EMAC Slave                       | 3:0 Device ID                                                     | Section 3.3.6 |

| 8             | EMAC Forced                      | 3:0 Device ID                                                     | Section 3.3.6 |

| 9             | Reserved                         | N/A                                                               |               |

| 10            | RapidIO Configuration 0          | 3:0 Node (0xF for default)                                        | Section 3.3.7 |

| 11            | RapidIO Configuration 1          | 3:0 Node (0xF for default)                                        | Section 3.3.7 |

| 12            | RapidIO Configuration 2          | 3:0 Node (0xF for default)                                        | Section 3.3.7 |

| 13            | RapidIO Configuration 3          | 3:0 Node (0xF for default)                                        | Section 3.3.7 |

| 14-15         | Reserved                         | N/A                                                               |               |

| Table 11 | TCI6484 | <b>Boot Mode</b> | e Selection |

|----------|---------|------------------|-------------|

|          | 1010404 | DOOL MOUG        |             |

#### 3.3 Boot Mode Options

#### 3.3.1 No Boot Mode

The TCI6484 deivce no boot mode is similar to the TCI6482 device's process, described in Section 2.3.1, with the following differences:

- 1. No-boot mode is ROM based instead of completely hardware based.

- 2. The bootloader puts the DSP in sleep state until an interrupt arrives. The boot code sets the IER mask to 0xFF and GIE=1 prior to entering sleep state.

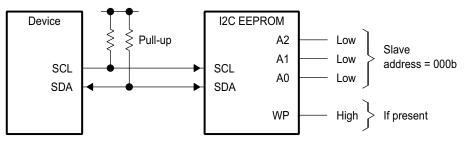

The boot ROM code flow is shown in Figure 2.

#### Figure 2. Program Flow for No-Boot Mode

The following points should be noted for no-boot mode usage:

- No-boot mode is usually selected when the user wants to download the application using an emulator in conjunction with Code Composer Studio (CCStudio). In this usage case, when CCStudio connects to the DSP, it brings the DSP out of the sleep state and PC execution is halted. CCStudio downloads the application image in DSP memory and the start address for execution is set to the application entry point (CCStudio uses the default entry point \_c\_int00). Application code execution starts when the user invokes the CCStudio Run command.

- The other usage option is a host that downloads the application to L2 (using an emulation protocol like RTDX) and provides an NMI to the DSP so that the application execution can start. The entry point to the application is always the L2 base. The application must be linked so that the entry point for the application is the L2 base (\_cint\_00 should be mapped to 0x0080000).

#### 3.3.2 I2C Master Mode

The TCI6484 device I2C master boot process is similar to the TCI6482 device's process, described in Section 2.3.4 and Section 2.3.5, with the following differences:

- 1. The PLL1 multiplier is set to 16.

- 2. The TCI6484 device supports both slave device addresses 0x50 and 0x51

- 3. Changes in the I2C boot parameter block format.

#### 3.3.2.1 I2C Boot Parameter Structure

Parameter blocks read from the EEPROM override the default settings stored in ROM. In addition, they allow the boot modes to be chained (e.g., I2C master boot followed by I2C master write boot or I2C master boot followed by SRIO boot mode). This gives the user flexibility to choose the settings. BOOTMODE[3:0] pins must be set to I2C master boot mode for a parameter block to be read. It is mandatory that the first block read in I2C master boot mode is a parameter block.

There are three different formats for parameter blocks: I2C, SRIO, and EMAC. These allow the user to customize settings for I2C, SRIO, and EMAC boot modes.

#### TCI6484 Bootloader Operation

\_

## www.ti.com

| Address<br>Offset<br>(bytes) | Name                          | Value                                                                                                                 | Default Value (in ROM)                                 |

|------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| (bytes)                      | Length                        | Length of the table, in bytes.                                                                                        | 30 bytes (size of I2C param block)                     |

| 2                            | Checksum                      | 1s complement checksum, 0 for disabled checksum.                                                                      | 0                                                      |

| 4                            | Boot mode                     | Boot modes as shown in Table 13.                                                                                      | BOOTMODE[3:0] translated to values in Table 13.        |

| 6                            | Port                          | Physical port number, always 0.                                                                                       | 0                                                      |

| 8                            | Software PLL                  | Software PLL multiply factor, not used.                                                                               | 16                                                     |

| 10                           | Option                        | 0b000 - Boot Parameter mode                                                                                           | 0b000 when BOOTMODE[3:0] is I2C master boot mode       |

|                              |                               | 0b001 - Boot Table mode                                                                                               | 0b001 when BOOTMODE[3:0] is I2C slave boot mode        |

|                              |                               | 0b010 - Boot Config mode                                                                                              |                                                        |

|                              |                               | 0b011 - Slave boot                                                                                                    |                                                        |

|                              |                               | 0b100 - Master broadcast boot                                                                                         |                                                        |

|                              |                               | 0b101-0b111 - Reserved                                                                                                |                                                        |

| 12                           | Device address<br>(low)       | I2C data address, LSW.                                                                                                | DEVNUM[3:0] * 0x80                                     |

| 14                           | Device address<br>(high)      | Slave device address on I2C bus address.                                                                              | 0x50 or 0x51 depending on I2C boot mode                |

| 16                           | Broadcast<br>address          | In I2C master write mode, the I2C data is sent to this address (after I2C EEPROM read).                               | 0                                                      |

| 18                           | Device ID                     | The address of this device on the I2C Bus (used for slave boot only).                                                 | 0x04 when BOOTMODE[3:0] is I2C master boot mode        |

|                              |                               |                                                                                                                       | CFG[3:0] + 1 when BOOTMODE[3:0] is I2C slave boot mode |

| 20                           | Core frequency,<br>MHz        | The frequency of the CPU core.                                                                                        | 800                                                    |

| 22                           | I2C bus<br>frequency, kHz     | The desired I2C bus frequency. Used only if the device is an I2C master.                                              | 10                                                     |