# TMS320DM646x DMSoC Video Port Interface (VPIF)

# **User's Guide**

Literature Number: SPRUER9D November 2009

| Pref | ace     |                                                                                                             | 10         |

|------|---------|-------------------------------------------------------------------------------------------------------------|------------|

| 1    | Introdu | ction                                                                                                       | 12         |

|      | 1.1     | Overview                                                                                                    | 12         |

|      | 1.2     | Features                                                                                                    | 13         |

|      | 1.3     | Features Not Supported                                                                                      | 13         |

|      | 1.4     | Functional Block Diagram                                                                                    | 13         |

|      | 1.5     | Supported Use Cases                                                                                         | 15         |

| 2    | Archite | cture                                                                                                       | 16         |

|      | 2.1     | Clock Control                                                                                               | 16         |

|      | 2.2     | Signal Descriptions                                                                                         | 16         |

|      | 2.3     | Pin Multiplexing                                                                                            | 16         |

|      | 2.4     | Video Stream Capture Mode                                                                                   | 16         |

|      | 2.5     | Clipping Function for Output                                                                                | 26         |

|      | 2.6     | Reset Considerations                                                                                        | 26         |

|      | 2.7     | Initialization                                                                                              | 26         |

|      | 2.8     | Interrupt Support                                                                                           | 27         |

|      | 2.9     | Power Management                                                                                            | 29         |

|      | 2.10    | Emulation Considerations                                                                                    | 29         |

|      | 2.11    | Rules for Module Control                                                                                    | 31         |

|      | 2.12    | PIXEL Enable                                                                                                | 31         |

|      | 2.13    | Operation                                                                                                   | 32         |

|      | 2.14    | Burst Size Between VPIF Module and SDRAM Control                                                            | 36         |

| 3    | Registe | rs                                                                                                          | <b>37</b>  |

|      | 3.1     | VPIF Peripheral Identification Register (PID)                                                               | 40         |

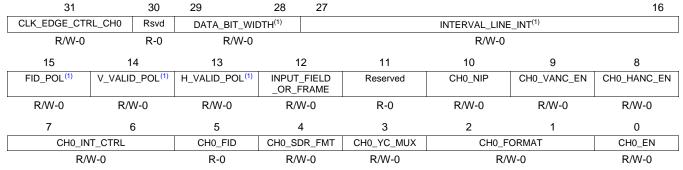

|      | 3.2     | Channel 0 Control Register (CH0_CTRL)                                                                       | 40         |

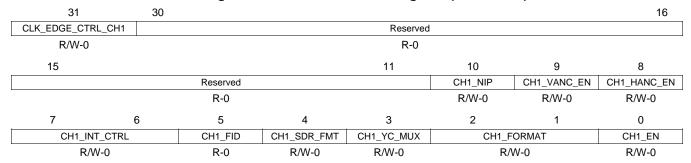

|      | 3.3     | Channel 1 Control Register (CH1_CTRL)                                                                       | 43         |

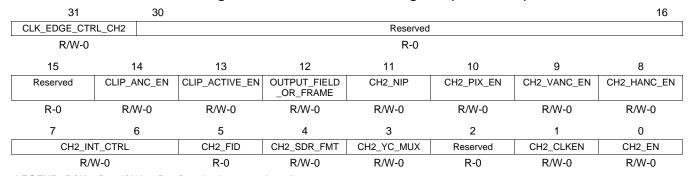

|      | 3.4     | Channel 2 Control Register (CH2_CTRL)                                                                       | 45         |

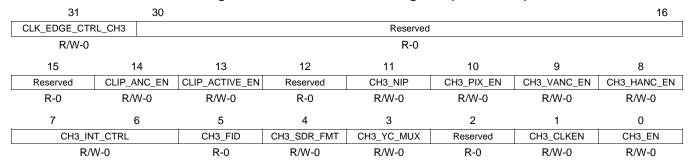

|      | 3.5     | Channel 3 Control Register (CH3_CTRL)                                                                       | 47         |

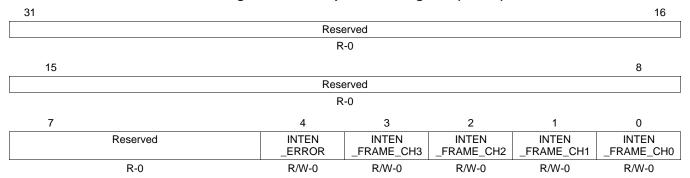

|      | 3.6     | Interrupt Enable Register (INTEN)                                                                           | 49         |

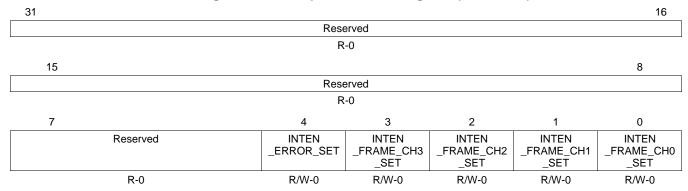

|      | 3.7     | Interrupt Enable Set Register (INTENSET)                                                                    | <b>5</b> 0 |

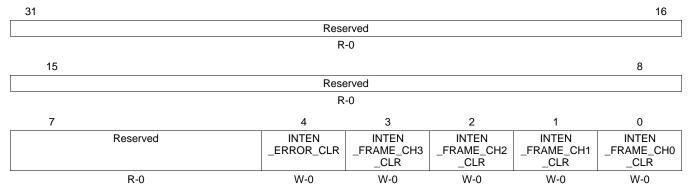

|      | 3.8     | Interrupt Enable Clear Register (INTENCLR)                                                                  | 52         |

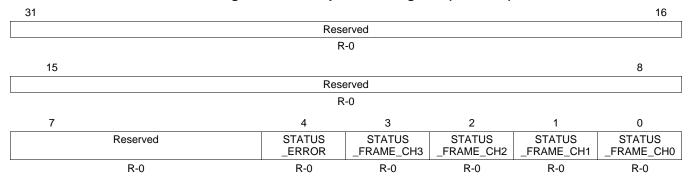

|      | 3.9     | Interrupt Status Register (INTSTAT)                                                                         | 54         |

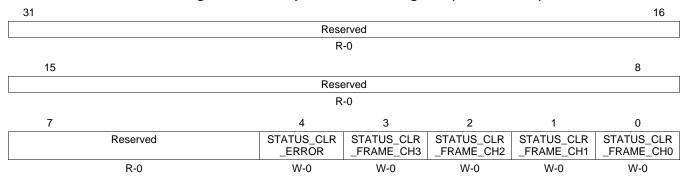

|      | 3.10    | Interrupt Status Clear Register (INTSTATCLR)                                                                | 55         |

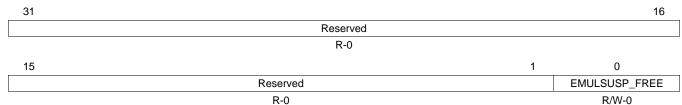

|      | 3.11    | Emulation Suspend Control Register (EMU_CTRL)                                                               | 56         |

|      | 3.12    | DMA Size Control Register (DMA_SIZE)                                                                        | 57         |

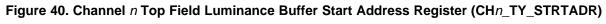

|      | 3.13    | Channel <i>n</i> Top Field Luminance Buffer Start Address Register (CH0_TY_STRTADR and CH1_TY_STRTADR)      | 58         |

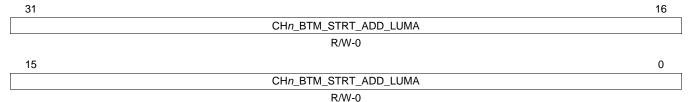

|      | 3.14    | Channel <i>n</i> Bottom Field Luminance Buffer Start Address Register (CH0_BY_STRTADR and CH1_BY_STRTADR)   | 61         |

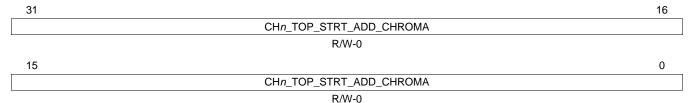

|      | 3.15    | Channel <i>n</i> Top Field Chrominance Buffer Start Address Register (CH0_TC_STRTADR and CH1_TC_STRTADR)    | 62         |

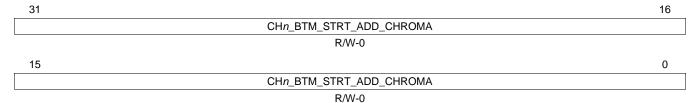

|      | 3.16    | Channel <i>n</i> Bottom Field Chrominance Buffer Start Address Register (CH0_BC_STRTADR and CH1_BC_STRTADR) | 63         |

|      | 3.17    | Channel <i>n</i> Top Field Horizontal Ancillary Data Buffer Start Address Register (CH0_THA_STRTADR         |            |

|      | and CH1_THA_STRTADR)                                                                                                         |

|------|------------------------------------------------------------------------------------------------------------------------------|

| 3.18 | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Buffer Start Address Register (CH0_BHA_STRTADR and CH1_BHA_STRTADR)  |

| 3.19 | Channel <i>n</i> Top Field Vertical Ancillary Data Buffer Start Address Register (CH0_TVA_STRTADR and CH1_TVA_STRTADR)       |

| 3.20 | Channel <i>n</i> Bottom Field Vertical Ancillary Data Buffer Start Address Register (CH0_BVA_STRTADR and CH1_BVA_STRTADR)    |

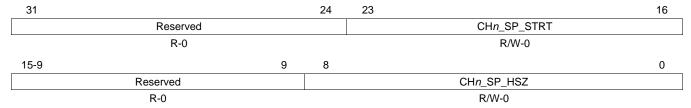

| 3.21 | Channel <i>n</i> Sub-Picture Configuration Register (CH0_SUBPIC_CFG and CH1_SUBPIC_CFG)                                      |

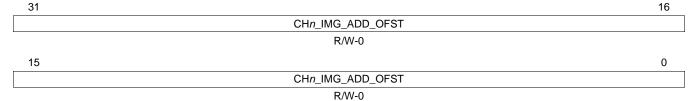

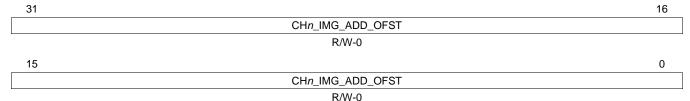

| 3.22 | Channel <i>n</i> Image Data Address Offset Register (CH0_IMG_ADD_OFST and CH1_IMG_ADD_OFST)                                  |

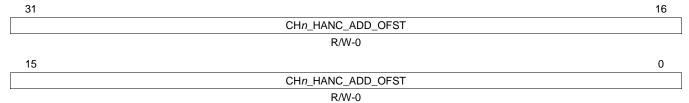

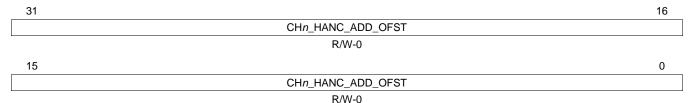

| 3.23 | Channel <i>n</i> Horizontal Ancillary Data Address Offset Register (CH0_HA_ADD_OFST and CH1_HA_ADD_OFST)                     |

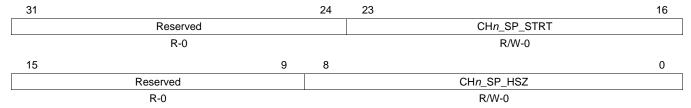

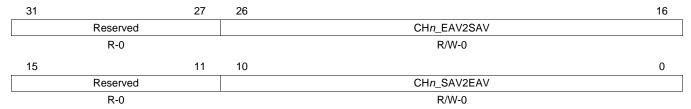

| 3.24 | Channel <i>n</i> Horizontal Data Size Configuration Register (CH0_HSIZE_CFG and CH1_HSIZE_CFG)                               |

| 3.25 | Channel <i>n</i> Vertical Data Size Configuration 0 Register (CH0_VSIZE_CFG0 and CH1_VSIZE_CFG0)                             |

| 3.26 | Channel <i>n</i> Vertical Data Size Configuration 1 Register (CH0_VSIZE_CFG_1 and CH1_VSIZE_CFG1)                            |

| 3.27 | Channel <i>n</i> Vertical Data Size Configuration 2 Register (CH0_VSIZE_CFG2 and CH1_VSIZE_CFG2)                             |

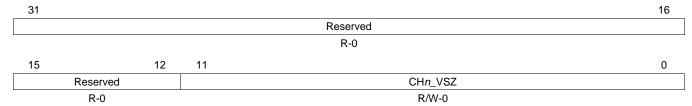

| 3.28 | Channel <i>n</i> Vertical Image Size Register (CH0_VSIZE and CH1_VSIZE)                                                      |

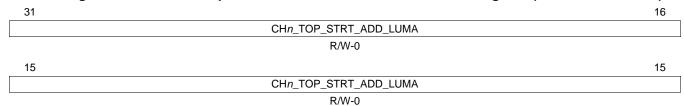

| 3.29 | Channel <i>n</i> Top Field Luminance Buffer Start Address Register (CH2_TY_STRTADR and CH3_TY_STRTADR)                       |

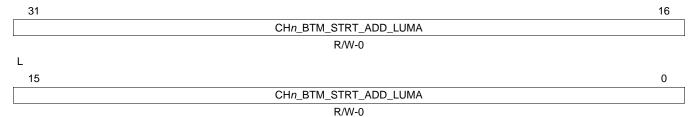

| 3.30 | Channel <i>n</i> Bottom Field Luminance Buffer Start Address Register (CH2_BY_STRTADR and CH3_BY_STRTADR)                    |

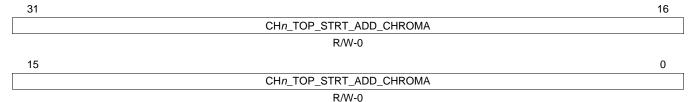

| 3.31 | Channel <i>n</i> Top Field Chrominance Buffer Start Address Register (CH2_TC_STRTADR and CH3_TC_STRTADR)                     |

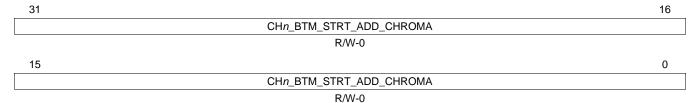

| 3.32 | Channel <i>n</i> Bottom Field Chrominance Buffer Start Address Register (CH2_BC_STRTADR and CH3_BC_STRTADR)                  |

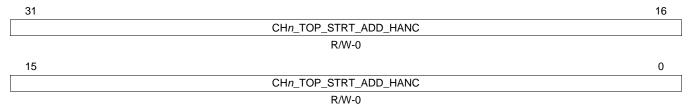

| 3.33 | Channel <i>n</i> Top Field Horizontal Ancillary Data Buffer Start Address Register (CH2_THA_STRTADR and CH3_THA_STRTADR)     |

| 3.34 | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Buffer Start Address Register (CH2_BHA_STRTADR and CH3_BHA_STRTADR)  |

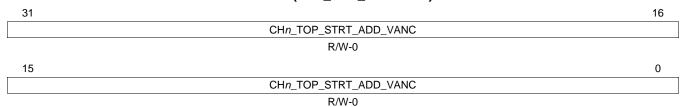

| 3.35 | Channel <i>n</i> Top Field Vertical Ancillary Data Buffer Start Address Register (CH2_TVA_STRTADR and CH3_TVA_STRTADR)       |

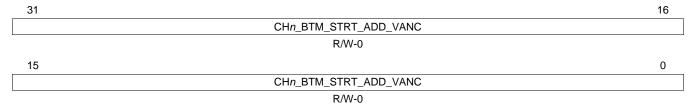

| 3.36 | Channel <i>n</i> Bottom Field Vertical Ancillary Data Buffer Start Address Register (CH2_BVA_STRTADR and CH3_BVA_STRTADR)    |

| 3.37 | Channel <i>n</i> Sub-Picture Configuration Register (CH2_SUBPIC_CFG and CH3_SUBPIC_CFG)                                      |

| 3.38 | Channel <i>n</i> Image Data Address Offset Register (CH2_IMG_ADD_OFST and CH3_IMG_ADD_OFST)                                  |

| 3.39 | Channel <i>n</i> Horizontal Ancillary Data Address Offset Register (CH2_HA_ADD_OFST and CH3_HA_ADD_OFST)                     |

| 3.40 | Channel <i>n</i> Horizontal Data Size Configuration Register (CH2_HSIZE_CFG and CH3_HSIZE_CFG)                               |

| 3.41 | Channel <i>n</i> Vertical Data Size Configuration 0 Register (CH2_VSIZE_CFG0 and CH3_VSIZE_CFG0)                             |

| 3.42 | Channel <i>n</i> Vertical Data Size Configuration 1 Register (CH2_VSIZE_CFG1 and CH3_VSIZE_CFG1)                             |

| 3.43 | Channel <i>n</i> Vertical Data Size Configuration 2 Register (CH2_VSIZE_CFG2 and CH3_VSIZE_CFG2)                             |

| 3.44 | Channel <i>n</i> Vertical Image Size Register (CH2_VSIZE and CH3_VSIZE)                                                      |

| 3.45 | Channel <i>n</i> Top Field Horizontal Ancillary Data Insertion Start Position Register (CH2_THA_STRTPOS and CH3_THA_STRTPOS) |

| 3.46 | Channel <i>n</i> Top Field Horizontal Ancillary Data Size Register (CH2_THA_SIZE and CH3_THA_SIZE)                           |

|      |                                                                                                                              |

#### www.ti.com

| 3.47         | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Insertion Start Position Register (CH2_BHA_STRTPOS and CH3_BHA_STRTPOS) | 91 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 3.48         | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Size Register (CH2_BHA_SIZE and CH3_BHA_SIZE)                           | 92 |

| 3.49         | Channel <i>n</i> Top Field Vertical Ancillary Data Insertion Start Position Register (CH2_TVA_STRTPOS and CH3_TVA_STRTPOS)      | 93 |

| 3.50         | Channel <i>n</i> Top Field Vertical Ancillary Data Size Register (CH2_TVA_SIZE and CH3_TVA_SIZE)                                | 94 |

| 3.51         | Channel <i>n</i> Bottom Field Vertical Ancillary Data Insertion Start Position Register (CH2_BVA_STRTPOS and CH3_BVA_STRTPOS)   | 95 |

| 3.52         | Channel n Bottom Field Vertical Ancillary Data Size Register (CH2_BVA_SIZE and CH3_BVA_SIZE)                                    | 96 |

| Appendix A F | Revision History                                                                                                                | 97 |

# **List of Figures**

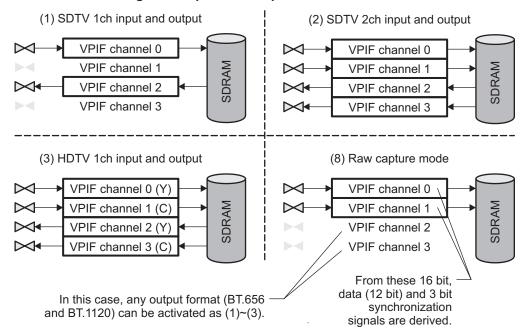

| 1  | Input and Output Channels of VPIF                                                                                | 12 |

|----|------------------------------------------------------------------------------------------------------------------|----|

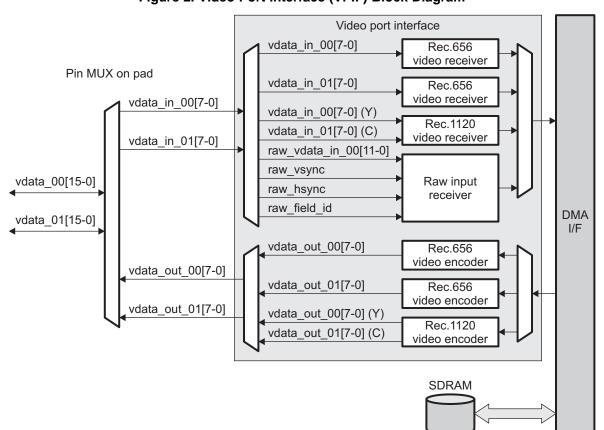

| 2  | Video Port Interface (VPIF) Block Diagram                                                                        |    |

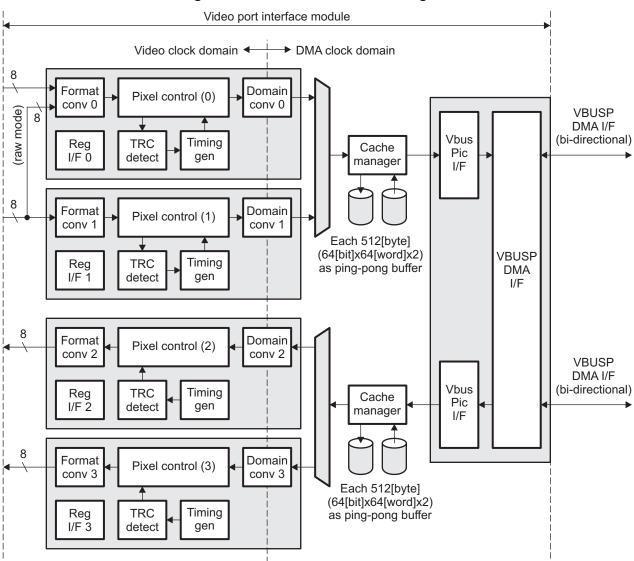

| 3  | VPIF Architecture Block Diagram                                                                                  |    |

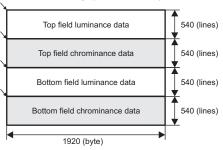

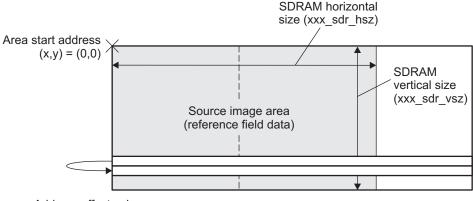

| 4  | Storage Format of Data in SDRAM (Interlaced Image)                                                               | 17 |

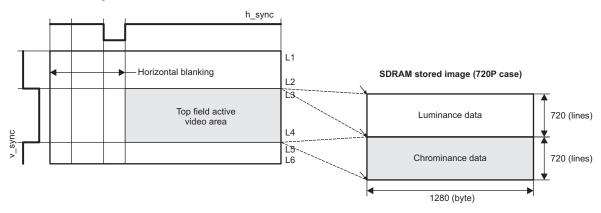

| 5  | Storage Format of Data in SDRAM (Progressive Image)                                                              |    |

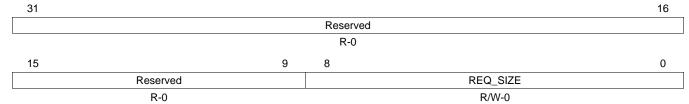

| 6  | Relationship Between SDRAM Stored Image and Incoming (Outgoing) Image                                            |    |

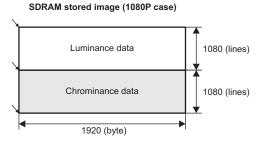

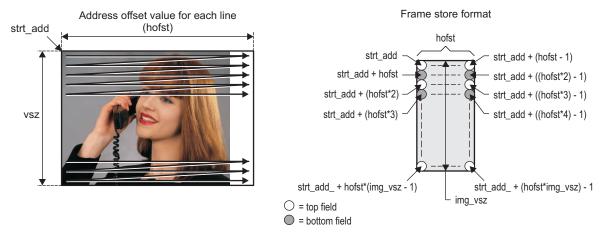

| 7  | SDRAM Storage Method                                                                                             |    |

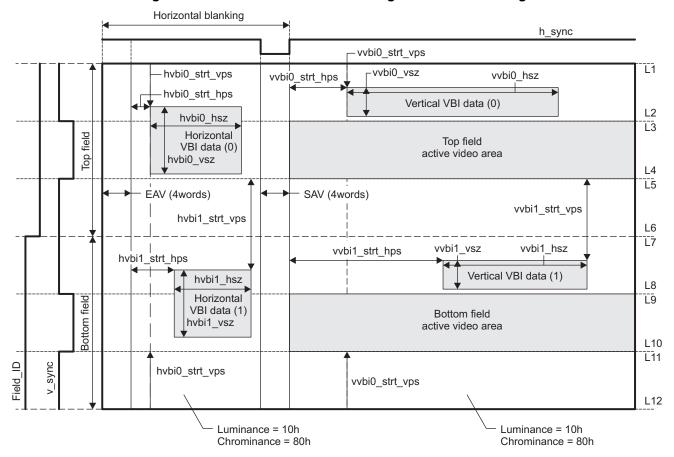

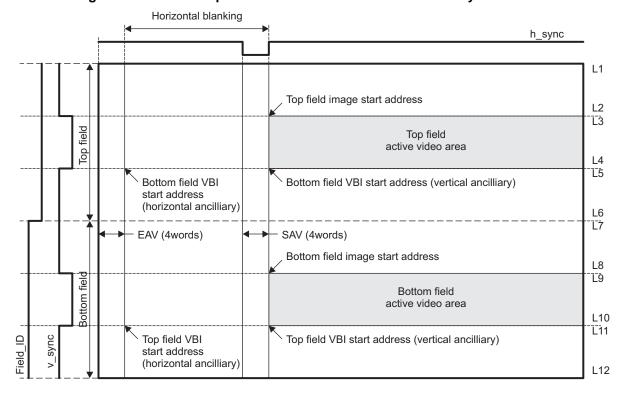

| 8  | VBI Result Data Transmit Image for Interlaced Image                                                              |    |

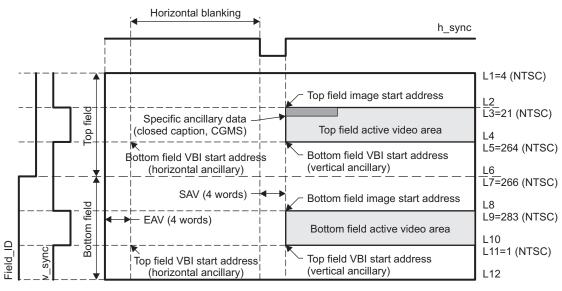

| 9  | Image of Specific Ancillary Data on NTSC                                                                         | 22 |

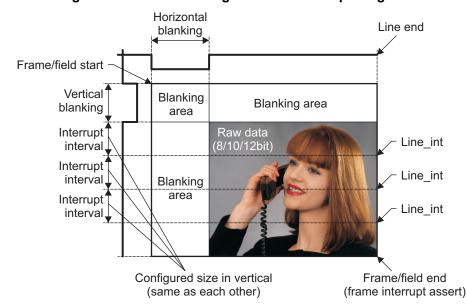

| 10 | Functional Image of Raw Data Capturing Mode                                                                      | 23 |

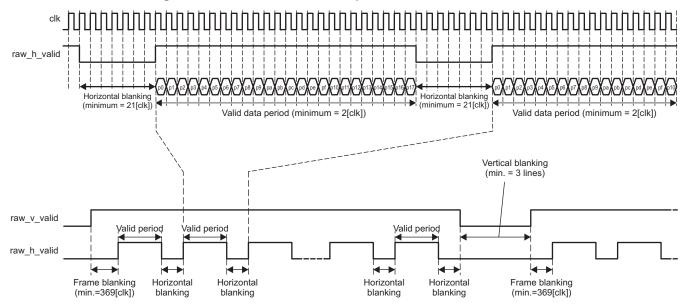

| 11 | Waveform on Raw Capture Interface Normal Mode                                                                    |    |

| 12 | Waveform on Raw Capture Interface Interlaced Normal Mode                                                         | 25 |

| 13 | Stuffing Manner in SDRAM Storage                                                                                 | 25 |

| 14 | VDD 3.3V I/O Power-Down Control Register (VDD3P3V_PWDN)                                                          | 26 |

| 15 | Relationship Between the First Interrupt and Incoming Data                                                       | 28 |

| 16 | Relationship Between the First Interrupt and Outgoing Data                                                       | 28 |

| 17 | Module Performance with Emulation Suspend Signal                                                                 | 29 |

| 18 | Emulation Suspend Function on Channels 2 and 3 (Transmit)                                                        | 30 |

| 19 | Method for Turning off Module Channel                                                                            | 31 |

| 20 | Clock Control on Video Input and Output with SDTV Encoding                                                       | 32 |

| 21 | Clock Control on Video Input and Output with HDTV Encoding                                                       | 33 |

| 22 | Clock Control on Video Input and Output with HDTV Encoding                                                       | 35 |

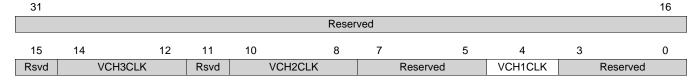

| 23 | Video Clock Control Register (VIDCLKCTL)                                                                         | 36 |

| 24 | Relationship Between Register and Data Access                                                                    | 37 |

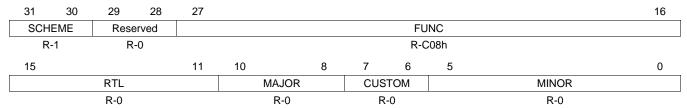

| 25 | VPIF Peripheral Identification Register (PID)                                                                    | 40 |

| 26 | Channel 0 Control Register (CH0_CTRL)                                                                            | 40 |

| 27 | Channel 1 Control Register (CH1_CTRL)                                                                            | 43 |

| 28 | Channel 2 Control Register (CH2_CTRL)                                                                            | 45 |

| 29 | Channel 3 Control Register (CH3_CTRL)                                                                            | 47 |

| 30 | Interrupt Enable Register (INTEN)                                                                                | 49 |

| 31 | Interrupt Enable Set Register (INTENSET)                                                                         | 50 |

| 32 | Interrupt Enable Clear Register (INTENCLR)                                                                       | 52 |

| 33 | Interrupt Status Register (INTSTAT)                                                                              | 54 |

| 34 | Interrupt Status Clear Register (INTSTATCLR)                                                                     | 55 |

| 35 | Emulation Suspend Control Register (EMU_CTRL)                                                                    | 56 |

| 36 | DMA Size Control Register (DMA_SIZE)                                                                             | 57 |

| 37 | Image of Storage Format on SDRAM in Sub-Picture Format                                                           | 58 |

| 38 | Image of Storage Format on SDRAM in Raster Scanning Format                                                       | 58 |

| 39 | Relationship Between SDRAM Start Address and Sync Position                                                       | 59 |

| 40 | Channel <i>n</i> Top Field Luminance Buffer Start Address Register (CH <i>n</i> _TY_STRTADR)                     | 60 |

| 41 | Channel <i>n</i> Bottom Field Luminance Buffer Start Address Register (CH <i>n</i> _BY_STRTADR)                  | 61 |

| 42 | Channel <i>n</i> Top Field Chrominance Buffer Start Address Register (CH <i>n</i> _TC_STRTADR)                   | 62 |

| 43 | Channel <i>n</i> Bottom Field Chrominance Buffer Start Address Register (CH <i>n</i> _BC_STRTADR)                | 63 |

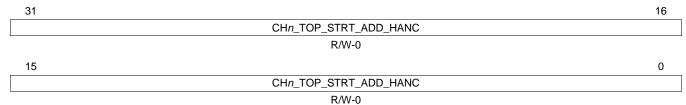

| 44 | Channel <i>n</i> Top Field Horizontal Ancillary Data Buffer Start Address Register (CH <i>n</i> _THA_STRTADR)    | 64 |

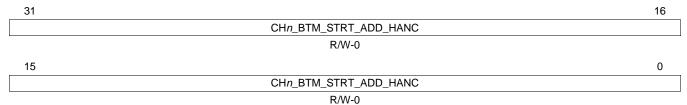

| 45 | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Buffer Start Address Register (CH <i>n</i> _BHA_STRTADR) | 65 |

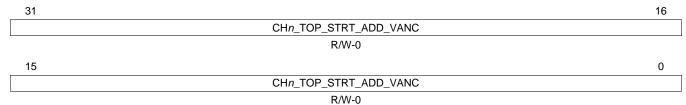

| 46 | Channel <i>n</i> Top Field Vertical Ancillary Data Buffer Start Address Register (CH <i>n</i> _TVA_STRTADR)      |    |

#### www.ti.com

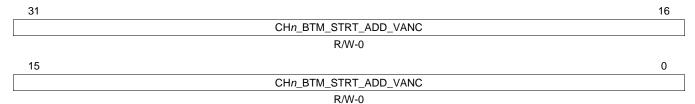

| 47 | Channel <i>n</i> Bottom Field Vertical Ancillary Data Buffer Start Address Register (CH <i>n</i> _BVA_STRTADR)       | 67         |

|----|----------------------------------------------------------------------------------------------------------------------|------------|

| 48 | Channel n Sub-Picture Configuration Register (CHn_SUBPIC_CFG)                                                        | 68         |

| 49 | Channel n Image Data Address Offset Register (CHn_IMG_ADD_OFST)                                                      | 69         |

| 50 | Channel <i>n</i> Horizontal Ancillary Data Address Offset Register (CH <i>n</i> _HA_ADD_OFST)                        | 70         |

| 51 | Image of Horizontal Distance in Y/C Mode                                                                             | <b>7</b> 0 |

| 52 | Image of Horizontal Distance in CCD/CMOS Mode                                                                        | 71         |

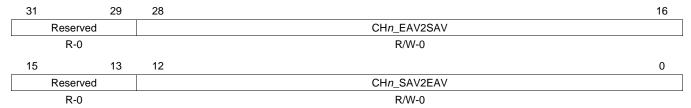

| 53 | Channel n Horizontal Data Size Configuration Register (CHn_HSIZE_CFG)                                                | 71         |

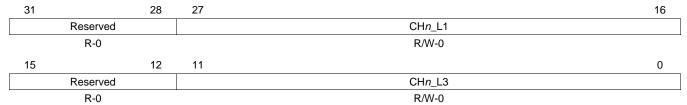

| 54 | Channel n Vertical Data Size Configuration 0 Register (CHn_VSIZE_CFG0)                                               | 72         |

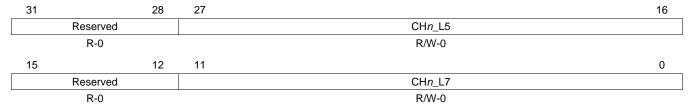

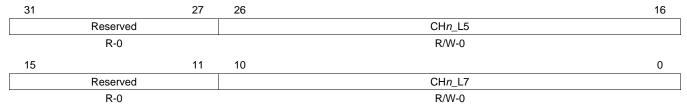

| 55 | Channel n Vertical Data Size Configuration 1 Register (CHn_VSIZE_CFG1)                                               | 73         |

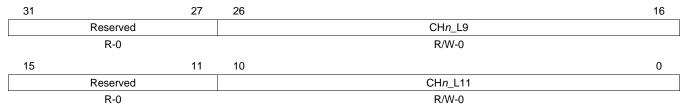

| 56 | Channel <i>n</i> Vertical Data Size Configuration 2 Register (CH <i>n</i> _VSIZE_CFG2)                               | 74         |

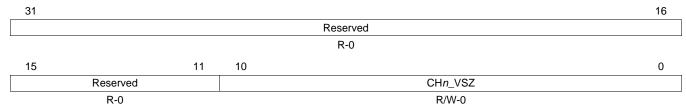

| 57 | Channel n Vertical Image Size Register (CHn_VSIZE)                                                                   | 74         |

| 58 | Channel <i>n</i> Top Field Luminance Buffer Start Address Register (CH <i>n</i> _TY_STRTADR)                         | 75         |

| 59 | Channel n Bottom Field Luminance Buffer Start Address Register (CHn_BY_STRTADR)                                      | 76         |

| 60 | Channel <i>n</i> Top Field Chrominance Buffer Start Address Register (CH <i>n</i> _TC_STRTADR)                       | 77         |

| 61 | Channel <i>n</i> Bottom Field Chrominance Buffer Start Address Register (CH <i>n</i> _BC_STRTADR)                    | 78         |

| 62 | Channel <i>n</i> Top Field Horizontal Ancillary Data Buffer Start Address Register (CH <i>n</i> _THA_STRTADR)        | 79         |

| 63 | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Buffer Start Address Register (CH <i>n</i> _BHA_STRTADR)     | 79         |

| 64 | Channel <i>n</i> Top Field Vertical Ancillary Data Buffer Start Address Register (CH <i>n</i> _TVA_STRTADR)          | 80         |

| 65 | Channel n Bottom Field Vertical Ancillary Data Buffer Start Address Register (CHn_BVA_STRTADR)                       | 81         |

| 66 | Channel n Sub-Picture Configuration Register (CHn_SUBPIC_CFG)                                                        | 82         |

| 67 | Channel n Image Data Address Offset Register (CHn_IMG_ADD_OFST)                                                      | 83         |

| 68 | Channel <i>n</i> Horizontal Ancillary Data Address Offset Register (CH <i>n</i> _HA_ADD_OFST)                        | 84         |

| 69 | Channel <i>n</i> Horizontal Data Size Configuration Register (CH <i>n</i> _HSIZE_CFG)                                | 85         |

| 70 | Channel n Vertical Data Size Configuration 0 Register (CHn_VSIZE_CFG0)                                               | 86         |

| 71 | Channel <i>n</i> Vertical Data Size Configuration 1 Register (CH <i>n</i> _VSIZE_CFG1)                               | 87         |

| 72 | Channel <i>n</i> Vertical Data Size Configuration 2 Register (CH <i>n</i> _VSIZE_CFG2)                               | 88         |

| 73 | Channel n Vertical Image Size Register (CHn_VSIZE)                                                                   | 89         |

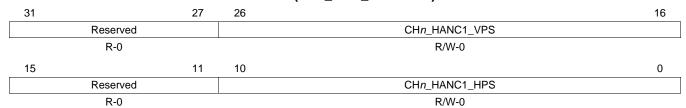

| 74 | Channel <i>n</i> Top Field Horizontal Ancillary Data Insertion Start Position Register (CH <i>n</i> _THA_STRTPOS)    | 89         |

| 75 | Channel <i>n</i> Top Field Horizontal Ancillary Data Size Register (CH <i>n</i> _THA_SIZE)                           | 90         |

| 76 | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Insertion Start Position Register (CH <i>n</i> _BHA_STRTPOS) | 91         |

| 77 | Channel n Bottom Field Horizontal Ancillary Data Size Register (CHn_BHA_SIZE)                                        | 92         |

| 78 | Channel n Top Field Vertical Ancillary Data Insertion Start Position Register (CHn_TVA_STRTPOS)                      | 93         |

| 79 | Channel n Top Field Vertical Ancillary Data Size Register (CHn_TVA_SIZE)                                             | 94         |

| 80 | Channel n Bottom Field Vertical Ancillary Data Insertion Start Position Register (CHn_BVA_STRTPOS)                   | 95         |

| 81 | Channel <i>n</i> Bottom Field Vertical Ancillary Data Size Register (CH <i>n</i> _BVA_SIZE)                          | 96         |

# **List of Tables**

| 1  | Supported Formats on VPIF                                                                                                           | 15 |

|----|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Input and Output Usage Combinations on VPIF                                                                                         | 15 |

| 3  | Pin Multiplexing Control                                                                                                            | 16 |

| 4  | VDD 3.3V I/O Power-Down Control Register (VDD3P3V_PWDN) Field Descriptions                                                          | 27 |

| 5  | VPIF Module Interrupts                                                                                                              | 27 |

| 6  | Register Configuration on BT.656 Input/Output (Unit Size = Byte in unsigned)                                                        | 32 |

| 7  | Register Configuration on BT.1120 (1080l60 and 1080l50 System) Input/Output (Unit Size = Byte in unsigned)                          | 33 |

| 8  | Register Configuration on BT.1120 (1080P30 and 1080P60 System) Input/Output (Unit Size = Byte in unsigned)                          | 34 |

| 9  | Register Configuration on SMPTE 296M Input/Output (Unit Size = Byte in unsigned)                                                    | 35 |

| 10 | Video Clock Control Register (VIDCLKCTL) Field Descriptions                                                                         | 36 |

| 11 | Video Port Interface (VPIF) Registers                                                                                               | 37 |

| 12 | VPIF Peripheral Identification Register (PID) Field Descriptions                                                                    | 40 |

| 13 | Channel 0 Control Register (CH0_CTRL) Field Descriptions                                                                            | 41 |

| 14 | Channel 1 Control Register (CH1_CTRL) Field Descriptions                                                                            | 43 |

| 15 | Channel 2 Control Register (CH2_CTRL) Field Descriptions                                                                            | 45 |

| 16 | Channel 3 Control Register (CH3_CTRL) Field Descriptions                                                                            | 47 |

| 17 | Interrupt Enable Register (INTEN) Field Descriptions                                                                                | 49 |

| 18 | Interrupt Enable Set Register (INTENSET) Field Descriptions                                                                         | 50 |

| 19 | Interrupt Enable Clear Register (INTENCLR) Field Descriptions                                                                       | 52 |

| 20 | Interrupt Status Register (INTSTAT) Field Descriptions                                                                              | 54 |

| 21 | Interrupt Status Clear Register (INTSTATCLR) Field Descriptions                                                                     | 55 |

| 22 | Emulation Suspend Control Register (EMU_CTRL) Field Descriptions                                                                    | 56 |

| 23 | DMA Size Control Register (DMA_SIZE) Field Descriptions                                                                             | 57 |

| 24 | Channel <i>n</i> Top Field Luminance Buffer Start Address Register (CH <i>n</i> _TY_STRTADR) Field Descriptions                     | 60 |

| 25 | Channel <i>n</i> Bottom Field Luminance Buffer Start Address Register (CH <i>n</i> _BY_STRTADR) Field Descriptions                  | 61 |

| 26 | Channel <i>n</i> Top Field Chrominance Buffer Start Address Register (CH <i>n</i> _TC_STRTADR) Field Descriptions                   | 62 |

| 27 | Channel <i>n</i> Bottom Field Chrominance Buffer Start Address Register (CH <i>n</i> _BC_STRTADR) Field Descriptions                | 63 |

| 28 | Channel <i>n</i> Top Field Horizontal Ancillary Data Buffer Start Address Register (CH <i>n</i> _THA_STRTADR) Field Descriptions    | 64 |

| 29 | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Buffer Start Address Register (CH <i>n</i> _BHA_STRTADR) Field Descriptions | 65 |

| 30 | Channel <i>n</i> Top Field Vertical Ancillary Data Buffer Start Address Register (CH <i>n</i> _TVA_STRTADR) Field Descriptions      | 66 |

| 31 | Channel <i>n</i> Bottom Field Vertical Ancillary Data Buffer Start Address Register (CH <i>n</i> _BVA_STRTADR) Field Descriptions   | 67 |

| 32 | Channel <i>n</i> Sub-Picture Configuration Register (CH <i>n</i> _SUBPIC_CFG) Field Descriptions                                    | 68 |

| 33 | Channel <i>n</i> Image Data Address Offset Register (CH <i>n</i> _IMG_ADD_OFST) Field Descriptions                                  | 69 |

| 34 | Channel <i>n</i> Horizontal Ancillary Data Address Offset Register (CH <i>n</i> _HA_ADD_OFST) Field Descriptions                    | 70 |

| 35 | Channel <i>n</i> Horizontal Data Size Configuration Register (CH <i>n</i> _HSIZE_CFG) Field Descriptions                            | 71 |

| 36 | Channel <i>n</i> Vertical Data Size Configuration 0 Register (CH <i>n</i> _VSIZE_CFG0) Field Descriptions                           | 72 |

| 37 | Channel <i>n</i> Vertical Data Size Configuration 1 Register (CH <i>n</i> _VSIZE_CFG1) Field Descriptions                           | 73 |

| 38 | Channel <i>n</i> Vertical Data Size Configuration 2 Register (CH <i>n</i> _VSIZE_CFG2) Field Descriptions                           | 74 |

| 39 | Channel <i>n</i> Vertical Image Size Register (CH <i>n</i> _VSIZE) Field Descriptions                                               | 74 |

| 40 | Channel $n$ Top Field Luminance Buffer Start Address Register (CH $n$ _TY_STRTADR) Field Descriptions                               | 75 |

| 41 | Channel n Bottom Field Luminance Buffer Start Address Register (CHn_BY_STRTADR) Field                                               |    |

#### www.ti.com

|    | Descriptions                                                                                                                            | 76 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 42 | Channel <i>n</i> Top Field Chrominance Buffer Start Address Register (CH <i>n</i> _TC_STRTADR) Field Descriptions                       | 77 |

| 43 | Channel <i>n</i> Bottom Field Chrominance Buffer Start Address Register (CH <i>n</i> _BC_STRTADR) Field Descriptions                    | 78 |

| 44 | Channel <i>n</i> Top Field Horizontal Ancillary Data Buffer Start Address Register (CH <i>n</i> _THA_STRTADR) Field Descriptions        | 79 |

| 45 | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Buffer Start Address Register (CH <i>n</i> _BHA_STRTADR) Field Descriptions     | 79 |

| 46 | Channel <i>n</i> Top Field Vertical Ancillary Data Buffer Start Address Register (CH <i>n</i> _TVA_STRTADR) Field Descriptions          | 80 |

| 47 | Channel <i>n</i> Bottom Field Vertical Ancillary Data Buffer Start Address Register (CH <i>n</i> _BVA_STRTADR) Field Descriptions       | 81 |

| 48 | Channel <i>n</i> Sub-Picture Configuration Register (CH <i>n</i> _SUBPIC_CFG) Field Descriptions                                        | 82 |

| 49 | Channel <i>n</i> Image Data Address Offset Register (CH <i>n</i> _IMG_ADD_OFST) Field Descriptions                                      | 83 |

| 50 | Channel <i>n</i> Horizontal Ancillary Data Address Offset Register (CH <i>n</i> _HA_ADD_OFST) Field Descriptions                        | 84 |

| 51 | Channel <i>n</i> Horizontal Data Size Configuration Register (CH <i>n</i> _HSIZE_CFG) Field Descriptions                                | 85 |

| 52 | Channel n Vertical Data Size Configuration 0 Register (CHn_VSIZE_CFG0) Field Descriptions                                               | 86 |

| 53 | Channel n Vertical Data Size Configuration 1 Register (CHn_VSIZE_CFG1) Field Descriptions                                               | 87 |

| 54 | Channel n Vertical Data Size Configuration 2 Register (CHn_VSIZE_CFG2) Field Descriptions                                               | 88 |

| 55 | Channel n Vertical Image Size Register (CHn_VSIZE) Field Descriptions                                                                   | 89 |

| 56 | Channel <i>n</i> Top Field Horizontal Ancillary Data Insertion Start Position Register (CH <i>n</i> _THA_STRTPOS) Field Descriptions    | 89 |

| 57 | Channel n Top Field Horizontal Ancillary Data Size Register (CHn_THA_SIZE) Field Descriptions                                           | 90 |

| 58 | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Insertion Start Position Register (CH <i>n</i> _BHA_STRTPOS) Field Descriptions | 91 |

| 59 | Channel <i>n</i> Bottom Field Horizontal Ancillary Data Size Register (CH <i>n</i> _BHA_SIZE) Field Descriptions                        | 92 |

| 60 | Channel <i>n</i> Top Field Vertical Ancillary Data Insertion Start Position Register (CH <i>n</i> _TVA_STRTPOS) Field Descriptions      | 93 |

| 61 | Channel n Top Field Vertical Ancillary Data Size Register (CHn_TVA_SIZE) Field Descriptions                                             | 94 |

| 62 | Channel <i>n</i> Bottom Field Vertical Ancillary Data Insertion Start Position Register (CH <i>n</i> _BVA_STRTPOS) Field Descriptions   | 95 |

| 63 | Channel <i>n</i> Bottom Field Vertical Ancillary Data Size Register (CH <i>n</i> _BVA_SIZE) Field Descriptions                          | 96 |

| 64 | Document Revision History                                                                                                               | 97 |

## Read This First

#### **About This Manual**

Describes the operation of the video port interface (VPIF) in the TMS320DM646x Digital Media System-on-Chip (DMSoC).

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

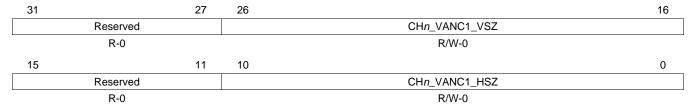

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320DM646x Digital Media System-on-Chip (DMSoC). Copies of these documents are available on the Internet at <a href="www.ti.com">www.ti.com</a>. Tip: Enter the literature number in the search box provided at <a href="www.ti.com">www.ti.com</a>.

The current documentation that describes the DM646x DMSoC, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <a href="https://www.ti.com/c6000">www.ti.com/c6000</a>.

- <u>SPRUEP8</u> *TMS320DM646x DMSoC DSP Subsystem Reference Guide.* Describes the digital signal processor (DSP) subsystem in the TMS320DM646x Digital Media System-on-Chip (DMSoC).

- SPRUEP9 TMS320DM646x DMSoC ARM Subsystem Reference Guide. Describes the ARM subsystem in the TMS320DM646x Digital Media System-on-Chip (DMSoC). The ARM subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In general, the ARM is responsible for configuration and control of the device; including the DSP subsystem and a majority of the peripherals and external memories.

- SPRUEQ0 TMS320DM646x DMSoC Peripherals Overview Reference Guide. Provides an overview and briefly describes the peripherals available on the TMS320DM646x Digital Media System-on-Chip (DMSoC).

- SPRAA84 TMS320C64x to TMS320C64x+ CPU Migration Guide. Describes migrating from the Texas Instruments TMS320C64x digital signal processor (DSP) to the TMS320C64x+ DSP. The objective of this document is to indicate differences between the two cores. Functionality in the devices that is identical is not included.

- SPRU732 TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

<u>SPRU871</u> — *TMS320C64x+ DSP Megamodule Reference Guide.* Describes the TMS320C64x+ digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

# Video Port Interface (VPIF)

#### 1 Introduction

This document describes the operation of the video port interface (VPIF) in the TMS320DM646x Digital Media System-on-Chip (DMSoC).

#### 1.1 Overview

The video port interface (VPIF) is a receiver and transmitter of video data with two input channels (channel 0 and 1) and two output channels (channel 2 and 3). Channels 0 and 1 have the same architecture, and channels 2 and 3 have the same architecture.

The input and output channel combinations of the VPIF are shown in Figure 1.

Figure 1. Input and Output Channels of VPIF

www.ti.com Introduction

#### 1.2 Features

The functional features of the VPIF are:

- Three speed grades (99 MHz, 108 MHz, and 150 MHz) available for the VPIF. See device-specific data manual for the part number associated with each speed grade.

- ITU-BT.656 format is supported.

- ITU-BT.1120, such as 1080I60, 1080P30, and 1080P60 (150 MHz VPIF devices only), and SMTPE 296 formats are supported.

- Raw data capturing function (receiver only; 8/10/12-bit format) is supported.

- VBI data storage is supported on BT.656 (SDTV) mode.

- Data clipping function for output (silicon revision 3.0 and later revisions only).

#### 1.3 Features Not Supported

The following functions are not supported:

- ITU-BT.601 format

- Separated synchronization format (which needs vertical and horizontal synchronization signal and field ID signal in independence to pixel data) is not supported (except in case of raw data capturing mode).

#### 1.4 Functional Block Diagram

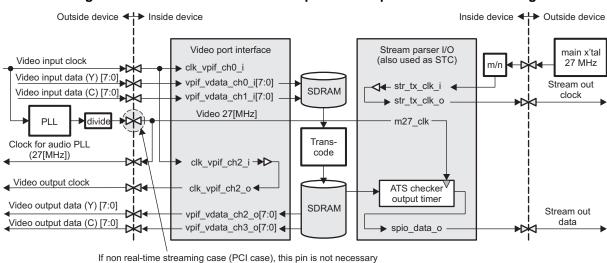

A block diagram of the VPIF is shown in Figure 2. A block diagram of the internal architecture of the VPIF is shown in Figure 3.

Figure 2. Video Port Interface (VPIF) Block Diagram

Introduction www.ti.com

Figure 3. VPIF Architecture Block Diagram

www.ti.com Introduction

#### 1.5 Supported Use Cases

The VPIF module has two input channels and two output channels. All channels can be activated simultaneously (see Table 1). One VPIF module has 4 GL type buffers (64 bit × 64 word single port SRAM).

- Channels 0 and 1 are prepared only for input.

- Channels 2 and 3 are prepared only for output.

As shown in Table 1, both NTSC and PAL formats are supported. Note that VBI is not supported for ITU-BT.1120 (HDTV). VBI support is necessary only for ITU-BT.656 (SDTV); in this case, VBI format has to be based on ITU-BT.1364. Table 2 describes the usage combinations that are supported in the VPIF.

**Table 1. Supported Formats on VPIF**

|                                  | TV Definition Format                               |                                                         |  |

|----------------------------------|----------------------------------------------------|---------------------------------------------------------|--|

| TV System Format                 | HDTV (rec. 1120)<br>(no support of ancillary data) | SDTV (rec. 656)<br>(ancillary data is based on BT.1364) |  |

| NTSC                             | 1125 line/60 field (vertical)                      | 525 line/60 field (vertical)                            |  |

|                                  | 2200 pixel (horizontal)                            | 858 pixel (horizontal)                                  |  |

| PAL                              | 1250 line/50 field (vertical)                      | 625 line/50 field (vertical)                            |  |

|                                  | 2304 pixel (horizontal)                            | 864 pixel (horizontal)                                  |  |

| Square pixel common image format | 1080P30, 1080P60 <sup>(1)</sup>                    | -                                                       |  |

<sup>1080</sup>P60 is supported on 150 MHz VPIF devices only.

Table 2. Input and Output Usage Combinations on VPIF

|                             |                                      | Output Format                                               |                                      |

|-----------------------------|--------------------------------------|-------------------------------------------------------------|--------------------------------------|

| Input Format                | HDTV Output                          | SDTV Output                                                 | No Output                            |

| HDTV input (1 channel only) | V                                    | √                                                           | V                                    |

| Raw capture mode            | $\checkmark$                         | $\checkmark$                                                | $\checkmark$                         |

| SDTV input                  | (both 1-channel and 2-channel input) | $\sqrt{\text{(both 1-channel and 2-channel input/output)}}$ | (both 1-channel and 2-channel input) |

| No input                    | $\checkmark$                         | (both 1-channel and 2-channel output)                       |                                      |

#### 2 Architecture

This section describes the architecture of the video port interface module (VPIF).

#### 2.1 Clock Control

The VPIF has 4 clock input pins and 2 clock output pins. Each channel has 1 clock input pin and has clock edge control using the CLK\_EDGE\_CTRL\_CHn bit in the channel n control register (CHn\_CTRL). You can provide a clock for an external device on channel 2 or 3 using the CH2\_CLKEN bit in CH2\_CTRL or the CH3\_CLKEN bit in CH3\_CTRL. The source clocks for the VPIF are selected using the video interface clock control register (VIDCLKCTL) in the System module. You must enable the source clock for the VPIF using the video interface source clock disable register (VSCLKDIS) in the System module. The VSCLKDIS is also used to disable the clock inputs when changing the source clock to ensure glitch-free operation.

#### 2.2 Signal Descriptions

Table 3 describes the pin assignment on the VPIF. The video data input ports are for receiving video stream and capturing raw data; the two modes are controlled by the CH0\_FORMAT bit in the channel 0 control register (CH0\_CTRL). Shaded signals in Table 3 are synchronization signals that are necessary for capturing raw data.

| Pin Name  | Role on rec. 656 | Role on Raw Data<br>Capturing | Pin Name  | Role on rec. 656 | Role on Raw Data<br>Capturing |

|-----------|------------------|-------------------------------|-----------|------------------|-------------------------------|

| VP_D[0]   | vin_data_00[0]   | vin_data_raw[0]               | VP_D[8]   | vin_data_01[0]   | vin_data_raw[8]               |

| VP_D[1]   | vin_data_00[1]   | vin_data_raw[1]               | VP_D[9]   | vin_data_01[1]   | vin_data_raw[9]               |

| VP_D[2]   | vin_data_00[2]   | vin_data_raw[2]               | VP_D[10]  | vin_data_01[2]   | vin_data_raw[10]              |

| VP_D[3]   | vin_data_00[3]   | vin_data_raw[3]               | VP_D[11]  | vin_data_01[3]   | vin_data_raw[11]              |

| VP_D[4]   | vin_data_00[4]   | vin_data_raw[4]               | VP_D[12]  | vin_data_01[4]   | not used                      |

| VP_D[5]   | vin_data_00[5]   | vin_data_raw[5]               | VP_D[13]  | vin_data_01[5]   | raw_field_id                  |

| VP_D[6]   | vin_data_00[6]   | vin_data_raw[6]               | VP_D[14]  | vin_data_01[6]   | raw_h_sync                    |

| VP_D[7]   | vin_data_00[7]   | vin_data_raw[7]               | VP_D[15]  | vin_data_01[7]   | raw_v_sync                    |

| VP_CLKIN0 | vin_data_00_clk  | vin_data_raw_clk              | VP_CLKIN1 | vin_data_01_clk  | vin_data_raw_clk              |

**Table 3. Pin Multiplexing Control**

#### 2.3 Pin Multiplexing

On the DM646x DMSoC, the VPIF is pin multiplexed to accommodate multiple peripheral functions in a smaller possible package. Pin multiplexing is controlled by using a combination of hardware configuration at device reset and software programmable register settings. Refer to the device-specific data manual to determine how pin multiplexing affects the VPIF.

#### 2.4 Video Stream Capture Mode

The video stream capture mode is for digital interface of video data that is defined by BT.656/1120 and SMTPE 296.

#### 2.4.1 Line Format

In the VPIF, both the input data and output data are stored in SDRAM. All video data is divided into image data and VBI data. The image data is divided into luminance and chrominance data in each field, independently. Each start address to be stored in SDRAM can be configured by the ARM processor through the register interface.

#### 2.4.1.1 Interlaced Image

The stored image of the video I/O data is shown in Figure 4 (for interlaced image).

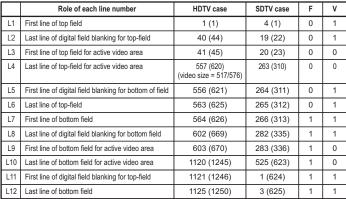

SDRAM stored image (SDTV 480i case) Video I/O format of 656/1120 268 h sync 1440 (byte) (byte) Top field Top field horizontal Horizontal blanking ancillary data field Top field active Bottom field Ľ3 Bottom field horizontal VBI data lop f È5: 240 (lines) Top field luminance data 17 Top field chrominance data 240 (lines) L9 Bottom field active Bottom field luminance data 240 (lines) SYNC video area Bottom field chrominance data 240 (lines) Top field VBI start address Top field VBI start address (vertical ancillary) L/1 (vertical ancillary) í 12 720 (byte) (4words) (4words) SDRAM stored image (HDTV 1080i case) Role of each line number HDTV case SDTV case ν Top field luminance data First line of top field 1 (1) 4 (1) 0 Last line of digital field blanking for top-field 40 (44) 19 (22) 0 1 Top field chrominance data

Figure 4. Storage Format of Data in SDRAM (Interlaced Image)

NOTE: L11 is regarded as the start line of the frame in the VPIF. The line number written is the same as the standard book of BT.656 and BT.1120. In interlace case, all register values, such as SDRAM base address, are detected at timing of L11.

All parameters (L1 to L11) and vertical screen size (distance between L1 to L12) in Figure 4 is configured by the software register. If the V-sync value on the EAV/SAV signal is different from the configured value on registers L1 to L12, the configured value has a higher priority than the detected V-sync value.

In Figure 4, the video data is distinguished into eight categories:

- Top field VBI data in vertical ancillary area

- Top field VBI data in horizontal ancillary area

- Bottom field VBI data in vertical ancillary area

- Bottom field VBI data in horizontal ancillary area

- Top field luminance data

- Top field chrominance data

- Bottom field luminance data

- Bottom field chrominance data

For each data, the following elements are a configuration parameter of each function:

Start address in SDRAM (corresponding to the start position of the storage area). (This data is prepared for top field and bottom field, independently. Other data is prepared for common use in top and bottom field.)

- Start position (horizontal and vertical), which is defined as a related position from the (0,0) position defined for VBI data output (VBI data only).

- Horizontal data size (VBI data only) to be read from SDRAM.

- Vertical image size to be stored in SDRAM.

- Address line offset (byte: minimum unit size = 8 bytes).

- Sub-picture size (byte) in horizontal direction (image data only).

#### 2.4.1.2 Progressive Image

The stored image of the video I/O data is shown in Figure 5 (for progressive image).

Figure 5. Storage Format of Data in SDRAM (Progressive Image)

Video I/O format of Progressive mode

|    | Role of each line number                      | 720P | 1080P | F | ٧ |

|----|-----------------------------------------------|------|-------|---|---|

| L1 | First line of upper blanking for the frame    | 1    | 1     | 0 | 1 |

| L2 | Last line of upper blanking for the frame     | 25   | 41    | 0 | 1 |

| L3 | First line of the frame for active video area | 26   | 42    | 0 | 0 |

| L4 | Last line of the frame for active video area  | 745  | 1121  | 0 | 0 |

| L5 | First line of lower blanking for the frame    | 746  | 1122  | 0 | 1 |

| L6 | Last line of lower blanking for the frame     | 750  | 1125  | 0 | 1 |

- (1) The register value (such as SDRAM storage address) is detected at timing of L1 in progressive case. Data on L5 to L6 is stored into a different SDRAM area from data on L1 to L2 because the base address is changed at timing of L1. If you would like to use ancillary data, you need to insert the ancillary data on the L1 to L2 area.

- (2) 1080P60 is supported on 150 MHz VPIF devices only.

All parameters (L1 to L6) and vertical screen size (distance between L1 to L6) in Figure 5 is configured by the software register. If the V-sync value on the EAV/SAV signal is different from the configured value on registers L1 to L6, the configured value has a higher priority than the detected V-sync value.

In Figure 5, the video data is distinguished into four categories:

- · VBI data in vertical ancillary area

- VBI data in horizontal ancillary area

- Luminance data

- Chrominance data

For each data, the following elements are a configuration parameter of each function:

- Start address in SDRAM (in VBI, two area start address values should be configured).

- Start position (horizontal and vertical), which is defined as related position from the (0,0) position defined for VBI data output (VBI data only).

- Horizontal data size (VBI data only) to be read from SDRAM.

- Vertical image size to be stored in SDRAM.

- Address line offset (byte: minimum unit size = 8 bytes).

- Sub-picture size (byte) in horizontal direction (image data only).

#### 2.4.2 **Functional Performance Image**

In this section, we describe the functional performance that is related to the SDRAM storage format. These are two functions, the receiver (VPIF receives input video data) and the transmitter (VPIF transmits video data stored in SDRAM).

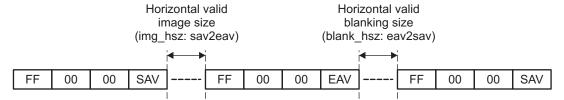

- Image Data Input: In interlace mode (Figure 4), the VPIF starts to store the input image data in SDRAM horizontally between the SAV code and the EAV code and vertically between L3 to L4 or L9 to L10. In progressive mode (Figure 5), the video image data exists only between L3 to L4.

- Horizontal VBI Data Input: In interlace mode (Figure 4), the VPIF starts to store the input horizontal blanking data in SDRAM just after the EAV code in the horizontal blanking area between L1 to L12. In progressive mode (Figure 5), in the horizontal blanking area between L1 to L6.

- Vertical VBI Data Input: In interlace mode (Figure 4), the VPIF module starts to store the input vertical blanking data in SDRAM horizontally between the SAV code and EAV code and vertically between L1 to L2, L5 to L8, or L11 to L12. In progressive mode (Figure 5), between L1 to L2 or L5 to L6.

- Image Data Output: In interlace mode (Figure 4), the VPIF starts to read the source image data from SDRAM and asserts the read data to display horizontally between the SAV code and the EAV code and vertically between L3 to L4 or L9 to L10. In progressive mode (Figure 5), only L3 to L4 is displayed.

- Horizontal VBI Data Output: The VPIF starts to read the source horizontal blanking data from SDRAM and asserts the data from the configured start position with the configured size (both horizontal and vertical). Other than the configured area in horizontal blanking area should be filled with 10h (luminance position) or 80h (chrominance position).

- Vertical VBI Data Output: The VPIF starts to read the store vertical blanking data from SDRAM and asserts the data from the configured start position with the configured size (both horizontal and vertical), Other than the configured area in horizontal blanking area should be filled with 10h (luminance position) or 80h (chrominance position).

The functional image is shown in Figure 6. Addressing methods are discussed in Section 2.4.3.

Screen displaying image SDRAM storing image (image and VBI data) EAV FAV H sync (imaginary) **SDRAM** Horizontal image size (img\_hsz) Address offset value for each line start address Vertical image size (vsz) sync (imaginary) Vertical image size (img\_vsz) Vertical blanking Horizontal image size (hsz) size (blank vsz)

Figure 6. Relationship Between SDRAM Stored Image and Incoming (Outgoing) Image

Horizontal blanking size

(blank hsz)

#### 2.4.3 SDRAM Addressing

You have to define the address offset value for each line and select the storage method in SDRAM from two methods, field mode and frame mode, as shown in Figure 7.

Figure 7. SDRAM Storage Method

In Figure 7, the upper illustration is a functional image of the SDRAM storage method. With register configuration (horizontal and vertical image size, and horizontal sub-picture size), a detailed address for each pixel is defined. The lower left illustration shows the raster scanning format addressing in field format and the lower right illustration shows the frame format.

The INPUT\_FIELD\_OR\_FRAME bit in the channel 0 control register (CH0\_CTRL) and the OUTPUT\_FIELD\_OR\_FRAME bit in the channel 2 control register (CH2\_CTRL) defines the SDRAM storage format and these bits have no effect on the storage format in raster scanning mode. You should configure each register in field/frame mode as follows (based on the parameters shown in Figure 7):

- Field format:

- Top and bottom field start address is strt add

- Line offset value per one field line is equal to hofst

- Frame format:

- Top field start address is strt\_add

- Bottom field start address is strt\_add + hofst

- Line offset value per each field line is equal to hofst x 2

#### 2.4.4 VBI Data Transmit Function

The VPIF can insert VBI data in the horizontal and vertical blanking intervals. The source VBI data is prepared in SDRAM as a result of processing by the CPU (DSP or ARM). The VPIF reads the source data based on the register configuration of the VPIF and transmits to outside the DSP.

To reduce any redundant load of processing in the CPU (DSP or ARM), the CPU writes the result of the VBI data only into SDRAM and no stuffing data is prepared in SDRAM. You need to configure the control registers (shown in Figure 8 for interlaced mode) on the VPIF, in order to receive and transmit VBI data.

In Figure 8, two assignments are prepared for both horizontal ancillary data and vertical ancillary data in interlaced mode because ancillary data exists in both the top and bottom field blanking interval.

Each parameter is configured by the register interface of the VPIF. Note that the V-origin of each parameter in Figure 8 is a falling edge of the vertical synchronization signal that is defined in each video standard such as BT.656 or BT.1120.

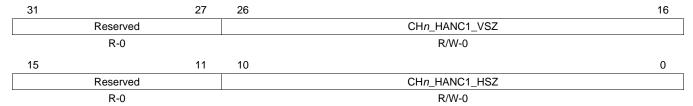

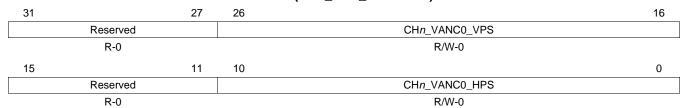

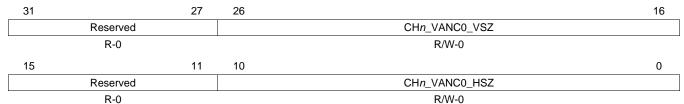

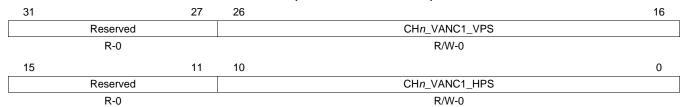

In this register map,

- HANC = horizontal ancillary data between EAV and SAV (horizontal blanking interval).

- VANC = vertical ancillary data between SAV and EAV (horizontal active video area).

The value of the horizontal start position should be a multiple of 8 on both the horizontal and vertical ancillary data areas. You can define any value as the horizontal size that does not exceed each data area.

Figure 8. VBI Result Data Transmit Image for Interlaced Image

#### 2.4.5 VBI Data Receive Function

The VPIF receives VBI data in the horizontal and vertical blanking interval. If the VBI receive function is enabled, the VPIF receives all data in the horizontal and vertical blanking data. The VPIF cannot receive VBI data from any selectable area. The CPU has to receive valid data from this data and you have to prepare for the correct size of data buffer. For example in the NTSC case, the horizontal ancillary data needs 268 bytes × 525 lines and the vertical ancillary data needs 1440 bytes × 38 lines buffer.

The address line offset for the vertical ancillary data uses the channel n image data address offset register (CHn\_IMG\_ADD\_OFST).

#### 2.4.6 Processing Method for Specific Ancillary Data

The VPIF has the ability to capture/assert video ancillary data (Figure 9) that is not video image data but is VBI data. In most cases, video ancillary data is inserted in the blanking interval for either the horizontal or vertical direction. But in some cases, such as CGMS or closed-caption that is in Japanese and US applications, the line number where these kinds of ancillary data is inserted is in the active video area. In the case that ancillary data is inserted in the active video area, the VPIF regards the incoming (or stored data) as video data.

Figure 9. Image of Specific Ancillary Data on NTSC

#### 2.4.7 Raw Data Capturing Function

The VPIF supports raw data capturing. With this function, you can connect a camera AFE output signal directly into an input port of the DSP. Usually, the output format of the camera AFE device is in raw format that consists of an RGB component (sometimes RGrGbB format). The following functions are supported:

- Storing pixel data in SDRAM (no storage of blanking data).

- Data bit width varies from 8 bits/pixel, 10 bits/pixel, and 12 bits/pixel mode.

- Maximum screen size with valid pixel is 2048(H) x 1536(V) in frame format.

- All data should be stored in SDRAM in byte-aligned format.

- Selectable polarity for H/V pixel valid signal and field ID signal.

- Separated field storage (top field and bottom field are stored independently) and interleaved field storage (normal frame format) support in SDRAM storage.

- Two kinds of interrupt support. One is asserted once per each configured line size (line\_interrupt) and

the other is asserted at the end of the capture area (frame\_interrupt). See Figure 10. Note that

line\_interrupt is only supported in raw mode. In other modes (BT.656, BT.1120, and SMPTE 296M),

line\_interrupt is not supported.

- Only raster scan format is supported in SDRAM storage format.

The following functions are not supported:

- No support of color space conversion from RGB to YCbCr.

- No CFA interpolation for each raw data pattern (such as Bayer or Foveon).

- No push-storage function on non-byte aligned data format (10 bits/pixel and 12 bits/pixel). Data should be stored in SDRAM in byte-aligned format.

The active period of each synchronization signal is regarded as the blanking area and any other area is regarded as the active video area that is stored in SDRAM. See Figure 10.

Figure 10. Functional Image of Raw Data Capturing Mode

NOTE: All register configurations related to raw capture mode are reflected with the falling edge of the internal V-sync, which source is raw\_v\_valid, in normal polarity (low = blanking, high = data).

#### 2.4.7.1 Timing Chart on Raw Capture Mode

Both interlace and progressive interface modes are supported. The following signals are assigned to the interface signal of the raw capture mode:

- raw\_h\_valid: horizontal pixel valid signal (regarded as horizontal synchronization signal)

- raw\_v\_valid: vertical line valid signal (regarded as vertical synchronization signal)

- raw\_field\_id: field ID signal

- vin data raw[11:0]: raw data input (8 bits/pixel, 10 bits/pixel, and 12 bits/pixel)

#### 2.4.7.1.1 Progressive CCD Raw Capture Mode

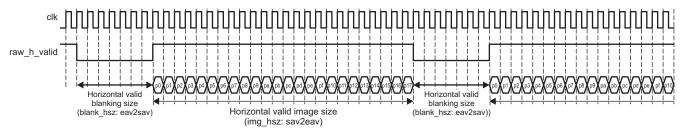

See Figure 11. The falling edge of the vertical valid signal (raw\_v\_valid) and the horizontal valid signal (raw\_h\_valid) is regarded as the normal vertical and horizontal synchronization signals, respectively. The description of the detail value in Figure 11 is based on the description on the Micron Image sensor device specification sheet.

In this mode, data with an active period of both of raw\_v\_valid and raw\_h\_valid is detected by the VPIF and the VPIF stores the valid data in SDRAM. The falling edge of the two signals is regarded as the vertical and horizontal synchronization signals (the valid signal polarity can be configured by the channel 0 control register (CH0\_CTRL)). You have to set the image address offset.

In this mode, without the activated period of raw\_v\_valid, no raw\_h\_valid signal is activated. Only in the period when both raw\_v\_valid and raw\_h\_valid signals are activated, the incoming data is regarded as valid data.

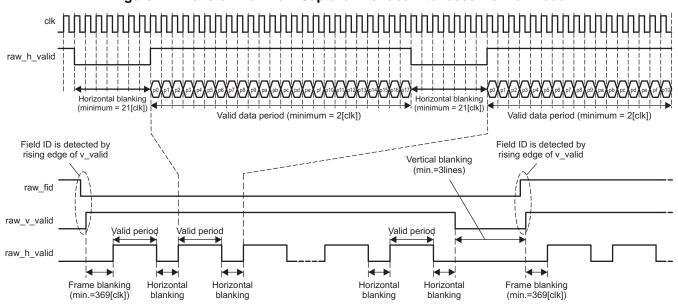

Figure 11. Waveform on Raw Capture Interface Normal Mode

#### 2.4.7.1.2 Interlace CCD Raw Capture Mode

See Figure 12. The falling edge of the vertical valid signal (raw\_v\_valid) and the horizontal valid signal (raw\_h\_valid) is regarded as the normal vertical and horizontal synchronization signals, respectively. The field ID (raw\_fid) is detected at the rising edge of the raw\_v\_valid signal. The description of the detail value in Figure 11 is based on the description on the Micron Image sensor device specification sheet.

In this mode, data with an active period of both of raw\_v\_valid and raw\_h\_valid is detected by the VPIF and the VPIF stores the valid data in SDRAM. The falling edge of the two signals is regarded as the vertical and horizontal synchronization signals (the valid signal polarity and the field ID polarity can be configured by the channel 0 control register (CH0\_CTRL)). You have to set the image address offset.

Figure 12. Waveform on Raw Capture Interface Interlaced Normal Mode

#### 2.4.7.2 SDRAM Format on Raw Capture Mode

All active video data shall be stored in SDRAM in byte-aligned format. In order to do this, you have to stuff blanked room of data in 10 bits/pixel and 12 bits/pixel mode (see Figure 13. The MSB side of each data is stuffed by 0 and pixel 0 is the first pixel of each line.

| Pixel 3 Pixel 2 Pixel 1             |                                 |

|-------------------------------------|---------------------------------|

| FIXEL 5 FIXEL 2 FIXEL I             | Pixel 0                         |

|                                     |                                 |

| 000000" & pixel 1[9:0]   "000000" & | pixel 0[9:0]                    |

|                                     |                                 |

| 0000" & pixel 1[11:0]               | ixel 0[11:0]                    |

| 00                                  | 0000" & pixel 1[9:0] "000000" & |

Figure 13. Stuffing Manner in SDRAM Storage

#### 2.5 Clipping Function for Output

**NOTE:** The data clipping function for output is supported only on silicon revision 3.0 and later revisions.

In certain cases, the active video data or the ancillary data contains a combination of FF-00-00-XY, which is the same as the TRC (EAV/SAV). Many video encoders will consider this combination as the TRC. As a result, the synchronization might fail. In order to avoid this issue, the VPIF module is capable of clipping the output data, with the exception of the TRC, to be between 01h and FEh. The value 00h is clipped to 01h and the value FFh is clipped to FEh. All other values are kept unchanged.

The cliping function is enabled for both channel 2 and channel 3; and it can be activated in each channel separately. Each channel has two types of data region other than the TRC: the blanking region and the active video region; and the clipping function can be activated in each region separately. The following shows the register setup needed to activate clipping:

- To enable clipping in the blanking region for channel 2: set CH2\_CTRL[14] = 1.

- To enable clipping in the active region for channel 2: set CH2\_CTRL[13] = 1.

- To enable clipping in the blanking region for channel 3: set CH3\_CTRL[14] = 1.

- To enable clipping in the active region for channel 3: set CH3\_CTRL[13] = 1.

#### 2.6 Reset Considerations

The VPIF does not have a software reset. When a hardware reset is asserted, all VPIF registers are set to their default values.

#### 2.7 Initialization

The general procedure for VPIF initialization is:

**NOTE:** The VDD 3.3V I/O power-down control register (VDD3P3V\_PWDN) in the System Module only controls the power to the I/O buffers. The Power and Sleep Controller (PSC) determines the clock/power state of the VPIF, see Section 2.9.

- 1. Enable I/O VDD power using the VDD 3.3V I/O power-down control register (VDD3P3V\_PWDN) in the System Module (see Figure 14 and Table 4).

- 2. Program the corresponding bits in the DMA size control register (DMA\_SIZE) and the channel *n* sub-picture configuration register (CH*n*\_SUBPIC\_CFG).

- 3. Program the Emulation related registers, such as the emulation suspend control register (EMU\_CTRL) in the VPIF and the emulation suspend source register (SUSPSRC) in the System Module (see Section 2.10 for more detail). The default values of SUSPSRC are configured to the ARM as the main processor.

#### Figure 14. VDD 3.3V I/O Power-Down Control Register (VDD3P3V\_PWDN)

#### Table 4. VDD 3.3V I/O Power-Down Control Register (VDD3P3V\_PWDN) Field Descriptions

| Bit | Field         | Value | Description                       |

|-----|---------------|-------|-----------------------------------|

| 3-0 | VPIF <i>n</i> |       | VPIF <i>n</i> power-down control. |

|     |               | 0     | I/O cells powered up              |

|     |               | 1     | I/O cells powered down            |

#### 2.8 Interrupt Support

#### 2.8.1 Interrupt Events and Requests

The VPIF sends interrupt events (Table 5) to the ARM and/or the DSP. The VP\_ERRINT interrupt is generated for the following reasons:

- For channels 0 or 1:

- Internal buffer overflow

- Length of eav2sav or sav2eav is not the same as the configured value

- Bit error detected on 4th field of TRC

- For channels 2 or 3:

- Internal buffer overflow

**Table 5. VPIF Module Interrupts**

| ARM Event | Acronym     | Source |  |

|-----------|-------------|--------|--|

| 0         | VP_VERTINT0 | VPIF   |  |

| 1         | VP_VERTINT1 | VPIF   |  |

| 2         | VP_VERTINT2 | VPIF   |  |

| 3         | VP_VERTINT3 | VPIF   |  |

| 4         | VP_ERRINT   | VPIF   |  |

#### 2.8.2 Field/Frame Interrupt to CPU

This section describes the conditions of the field/frame based interrupt assertion from the VPIF. The VPIF interrupt is designed to make the processor identify the timing for updating the address register of the VPIF module. The timing of the interrupt from the VPIF module is different from the timing of the V-sync. The interrupt is generated when the last data transfer between the VPIF module and the VBUS is finished.

#### 2.8.2.1 Interrupt Condition

The interrupt signal from the VPIF described in this section means the beginning of a field (or frame). A way to indicate the beginning of a field (or a frame) varies from the function mode; normal YC receive/transmit mode and CCD/CMOS capture mode differ because of the vertical synchronization signal.

The VPIF generates the following events as conditions for interrupt assertion:

- In normal YC receive/transmit mode, EAV on line L1 (and EAV on line L7 in field interrupt for bottom field). Both L1 and L7 are described in Figure 4 and Figure 5.

- In CCD/CMOS capture mode, starting edge for first line of vertical valid pixel area.

#### 2.8.2.2 First Interrupt from VPIF

NOTE: The first vertical synchronization signal is defined as the transition from the L10 line to the L11 line in the interlace mode or from the L4 line to the L5 line in the progressive mode.

For raw capture mode, the VPIF immediately starts to capture the data if you enable middle of frame.

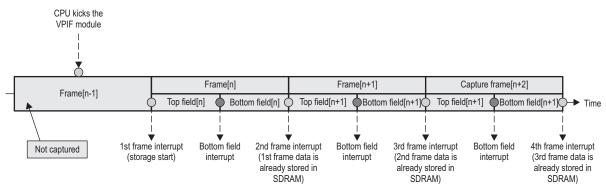

In channels 0 and 1, the VPIF starts to capture incoming picture data from the first vertical synchronization signal after the CPU activates the VPIF with register configuration. The interrupt signal from the VPIF is asserted when the vertical synchronization signal is received. So, no incoming data is written in SDRAM when the first interrupt is asserted from the VPIF (Figure 15).

As shown in Figure 15, the lighter point is the top-field interrupt and the darker point is the bottom-field interrupt. It depends on the register configuration, if these interrupt pulses are asserted.

If the CPU uses this interrupt signal not only for the time interval between each video frame but also for the timing to read the stored data from the defined area in SDRAM, note that the CPU has to ignore the first interrupt signal from the VPIF.

Figure 15. Relationship Between the First Interrupt and Incoming Data

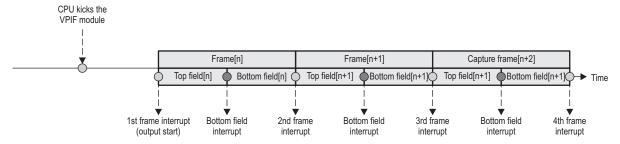

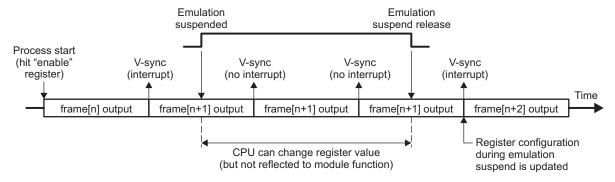

In channels 2 and 3, the VPIF starts to assert displaying picture data after the CPU activates the VPIF with register configuration. The output displaying data is asserted from the VPIF just after the VPIF reads the output data from SDRAM (Figure 16).

So, any redundant data such as the frame[n - 1] area in Figure 15 is not necessary to be prepared. The relationship between the interrupt pulse activation and the register configuration is the same as for capturing data.

If the Figure 16 described relationship with the CPU activates the VPIF and the incoming data and frame[n] start the L11 line for the interlace mode or the L5 line for the progressive mode, the VPIF starts the data store from frame[n+1] not frame[n]. The first frame interrupt happens after frame[n] (at the 2nd frame interrupt in Figure 16), because at the start of the incoming data, there is no first vertical synchronization signal.

Figure 16. Relationship Between the First Interrupt and Outgoing Data

#### 2.9 Power Management

The VPIF can be placed in reduced power modes to conserve power during periods of low activity. The power management of the peripheral is controlled by the processor Power and Sleep Controller (PSC). The PSC acts as a master controller for power management for all of the peripherals on the device. For detailed information on power management procedures using the PSC, see the *TMS320DM646x DMSoC ARM Subsystem Reference Guide* (SPRUEP9).

The VPIF uses two LPSC domains and you have to set the same state for these two domains. The LPSC controls only when all channels are disabled. If some channels are enabled, the LPSC can not change the VPIF state. You have to disable all channels before powering down using the LPSC.

#### 2.10 Emulation Considerations

In this section, the CPU is the processor that is selected by the emulation suspend source register (SUSPSRC) in the System Module.

#### 2.10.1 Emulation Suspend Mode Support

The VPIF supports the emulation suspend signal from the CPU. The emulation suspend signal (a high signal indicates that the CPU is suspended) is asserted by the CPU when the CPU is halted with a breakpoint or any other reason during debug.

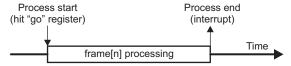

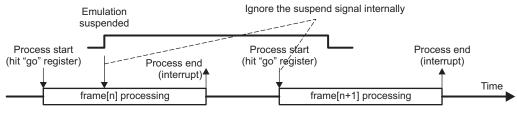

Functional performance, when the emulation suspend signal is received, is defined by the register configuration and is different for each use (receiver and transmitter). Because the VPIF has to process real-time incoming (or outgoing) data that has a unit size of 1 frame, the VPIF can be stalled at the nearest end of the present processing frame when the emulation suspend signal is received. The fundamental performance of emulation suspend is shown in Figure 17.

Figure 17. Module Performance with Emulation Suspend Signal

(a) Normal case (no input of emulation suspend)

(b) Free-run mode

#### 2.10.1.1 Receiver (Channels 0 and 1)

The VPIF receives input data from an external video device. The input format is BT.656 or BT.1120 (see Section 2.4.1). If the emulation suspend comes from the CPU during image processing, the VPIF will first try to run at the end of the present frame and then the VPIF will be stalled (see Figure 17 (c)).

The VPIF should have only a software stop mode; the hardware stop mode is not supported. If the CPU changes the register configuration during an emulation suspended period, the new configuration should be validated at the first V-sync after the suspended period.

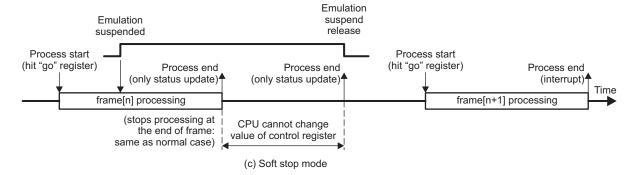

#### 2.10.1.2 Transmitter (Channels 2 and 3)

The VPIF transmits output data to an external video device. Source data for this output data is stored in SDRAM. The VPIF needs information about the start address of the source data stored in SDRAM. The output format is BT.656 or BT.1120 (see Section 2.4.1).

In this mode, any suspend function should not be activated because you would like to see a displayed picture, taking usage of this signal into consideration. From a system's stand point, the VPIF should act in the following sequence if the emulation suspend signal is detected:

- 1. The VPIF continues processing at the end of the present frame.

- 2. If the present frame is finished, interrupt assertion is stalled.

- 3. At phase (b), during the active period of the emulation suspend signal, the VPIF continues reading the same frame data from SDRAM (no register change is reflected to module performance during this period).

- 4. After the CPU returns back to the normal state, the VPIF performs as usual. New register configurations done during an emulation suspend period are reflected in the functional performance at the first V-sync after deassertion of the suspend signal.

If the CPU changes the register configuration during an emulation suspended period, the new configuration should be validated at the first V-sync after the suspended period. Functional performance of this mode is shown in Figure 18.

Figure 18. Emulation Suspend Function on Channels 2 and 3 (Transmit)

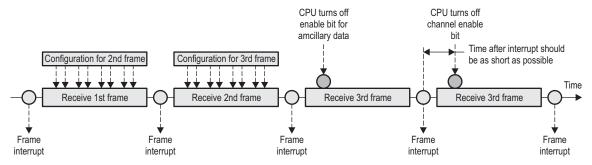

#### 2.11 Rules for Module Control

When you turn off the VPIF, see Figure 19, follow this sequence:

- 1. If you activate transmitting or capturing ancillary data (both of horizontal and vertical), turn off the enable bit before deactivating a channel of the VPIF.

- 2. Wait for frame interrupt of the channel.

- 3. Turn off the channel enable bit of the channel.

The VPIF stops immediately after writing 0 to the  $CHn_EN$  bit in the channel n control register ( $CHn_CTRL$ ). Writing to  $CHn_CTRL$  takes effect exactly at the same time you write to it, it does not wait to be latched by the VSYNC.

Figure 19. Method for Turning off Module Channel

#### 2.12 PIXEL Enable

The VPIF channels 2 and 3 pixel enable/disable is controlled by the  $CHn_PIX_EN$  bit in the channel n control register ( $CHn_CTRL$ ). Note that when you enable a pixel while the VPIF is enabled, the output pixel is not correct during reaching the next V-sync and you also receive a FIFO underflow error during that period.

#### 2.13 Operation

#### 2.13.1 BT.656 Mode

See Figure 20. The input clock source of 27 MHz is used for the source clock of the video output. In BT.656 mode, either channel of the input port on the VPIF is used as the actual input of the data. Note that you have to provide the same 27 MHz clock to the transport stream interface (TSIF) module as the video input clock, if you would like to transmit the encoded stream data in real-time; otherwise (for example, using a PCI module that has non real-time interface), you do not have to provide the 27 MHz clock to the TSIF module. Also, you have to provide a 27-MHz output to the external PLL device that provides the audio clock synchronized to the video output clock.

Outside device ◀+▶ Inside device Inside device ◆+ Outside device Video (27[MHz]) main x'tal Video port interface (0) Stream parser I/O Video input clock 27 MHZ m/r (also used as STC) (27[MHz]) clk\_vpif\_ch0\_i Video input data [7:0] vpif\_vdata\_ch0\_i[7:0] SDRAM Stream output clock str\_tx\_clk\_o m27\_clk Clock for audio PLL (27[MHz]) Transclk\_vpif\_ch2\_i → ▶ code ATS checker Video output clock output timer (27[MHz]) clk\_vpif\_ch2\_o◀ Stream output data Video output data [7:0] (with control flags) vpif\_vdata\_ch2\_o[7:0] SDRAM ▶ spio\_data\_o

Figure 20. Clock Control on Video Input and Output with SDTV Encoding

This path is necessary for real-time streaming output. (If non real-time streaming case (PCI case), this pin is not necessary)

#### 2.13.1.1 Parameter Configuration for BT.656 Mode

The configuration for each register in BT.656 mode is shown in Table 6.

| _                   |                | • • •            | -    | • ,  |

|---------------------|----------------|------------------|------|------|

| Parameter           | Register       | Bit Name         | NTSC | PAL  |

| EAV2SAV             | CHn_HSIZE_CFG  | CHn_EAV2SAV      | 268  | 280  |

| SAV2EAV             | CHn_HSIZE_CFG  | CHn_SAV2EAV      | 1440 | 1440 |

| Vertical frame size | CHn_VSIZE      | CHn_VSZ          | 525  | 625  |

| L1                  | CHn_VSIZE_CFG0 | CHn_L1           | 4    | 1    |

| L3                  | CHn_VSIZE_CFG0 | CHn_L3           | 20   | 23   |

| L5                  | CHn_VSIZE_CFG1 | CHn_L5           | 264  | 311  |

| L7                  | CHn_VSIZE_CFG1 | CHn_L7           | 266  | 313  |

| L9                  | CHn_VSIZE_CFG2 | CHn_L9           | 283  | 336  |

| L11                 | CHn_VSIZE_CFG2 | CH <i>n</i> _L11 | 1    | 624  |

Table 6. Register Configuration on BT.656 Input/Output (Unit Size = Byte in unsigned)

#### 2.13.2 BT.1120 Mode

The BT.1120 mode requires the same clock control for the VPIF as in BT.656 mode. The video input clock (74.25 MHz or 148.5 MHz) is also connected to another VPIF that manages the output image data. The BT.1120 format is necessary to support HDTV input and output for the VPIF. So, two VPIFs are necessary to receive (encode) an input image and to display (local decode) the output image. The functional image and clock control is shown in Figure 21. In this case, VPIF channels 0 and 1 are used for input and VPIF channels 2 and 3 are used for output.