SPRT490B-OCTOBER 2008-REVISED JUNE 2011

# TMS320C6472 Fixed-Point Digital Signal Processor Technical Brief

Check for Samples: TMS320C6472

## 1 Features

- Six On-Chip TMS320C64x+ Megamodules

- Endianess: Little Endian, Big Endian

- C64x+ Megamodule Main Features:

- High-Performance, Fixed-Point TMS320C64x+ DSP

- 500/625/700 MHz

- Eight 32-Bit Instructions/Cycle

- 4000 MIPS/MMACS (16-Bits) at 500 MHz

- Dedicated SPLOOP Instruction

- Compact Instructions (16-Bit)

- Instruction Set Enhancements

- Exception Handling

- L1/L2 Memory Architecture:

- 256K-Bit (32K-Byte) L1P Program RAM/Cache [Direct Mapped, Flexible Allocation]

- 256K-Bit (32K-Byte) L1D RAM/Cache [2-Way Set-Associative, Flexible Allocation]

- 4.75M-Bit (608K-Byte) L2 Unified Mapped RAM/Cache [4-Way Set-Associative, Flexible Allocation]

- L1P Memory Controller

- L1D Memory Controller

- L2 Memory Controller

- Time Stamp Counter

- One 64-Bit General-Purpose/Watchdog Timer

- Shared Peripherals and Interfaces

- EDMA Controller (64 Independent Channels)

- Shared Memory Architecture

- Shared L2 Memory Controller

- 768K-Byte of RAM

- Boot ROM

- Three Telecom Serial Interface Ports (TSIPs)

- Each TSIP is 8 Links of 8 Mbps per Direction

- 32-Bit DDR2 Memory Controller (DDR2-533 SDRAM)

- 256 M-Byte x 2 Addressable Memory Space

- Two 1x Serial RapidIO<sup>®</sup> Links, v1.2 Compliant

- 1.25-, 2.5-, 3.125-Gbps Link Rates

- Message Passing, DirectIO Support,

Error Management Extensions, and Congestion Control

- IEEE 1149.6 Compliant I/Os

- UTOPIA

- UTOPIA Level 2 Slave ATM Controller

- 8/16-Bit Transmit and Receive

Operations up to 50 MHz per Direction

- User-Defined Cell Format up to 64 Bytes

- Two 10/100/1000 Mb/s Ethernet MACs (EMACs)

- Both EMACs are IEEE 802.3 Compliant

- EMAC0 Supports:

- MII, RMII, SS-SMII, GMII, and RGMII

- 8 Independent Transmit (TX) Channels

- 8 Independent Receive (RX) Channels

- EMAC1 Supports:

- RMII, SS-SMII and RGMII

- 8 Independent Transmit (TX) Channels

- 8 Independent Receive (RX) Channels

- Both EMACs (EMAC0 and EMAC1) Share MDIO Interface

- 16-Bit Host-Port Interface (HPI)

- One Inter-Integrated Circuit (I<sup>2</sup>C) Bus

- Six Shared 64-Bit General-Purpose Timers

- System PLL and PLL Controller

- Secondary PLL and PLL Controller, Dedicated to EMAC

- Third PLL and PLL Controller Dedicated to DDR2 Memory Controller

- 16 General-Purpose I/O (GPIO) Pins

- IEEE-1149.1 (JTAG™) Boundary-Scan-Compatible

- 737-Pin Ball Grid Array (BGA) Package (CTZ or ZTZ Suffix), 0.8-mm Ball Pitch

- 0.09-µm/7-Level Cu Metal Process (CMOS)

- 3.3-, 1.8-, 1.5-, 1.2-V I/O Supplies

- 1.0-/1.1-, 1.2-V Core Supplies

- Commercial Temperature [0°C to 85°C]

- Extended Temperature [-40°C to 100°C]

- Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPRT490B-OCTOBER 2008-REVISED JUNE 2011

## 1.1 CTZ/ZTZ BGA Package (Bottom View)

The TMS320C6472 devices are designed for a package temperature range of 0°C to 85°C (commercial temperature range) or -40°C to 100°C (extended temperature range).

**NOTE** Extended temperature (A) range is available only on 500-MHz and 625-MHz devices.

|          | 000000000000000000000000000000000000000                                                                                     |

|----------|-----------------------------------------------------------------------------------------------------------------------------|

| AF AE    |                                                                                                                             |

|          |                                                                                                                             |

|          |                                                                                                                             |

| Y W      | 0000000      0000000000      0000000        0000000      0000000000      0000000        0000000      000000000      0000000 |

| τU       |                                                                                                                             |

| R<br>P   |                                                                                                                             |

| м        | 0000000      0000000000      0000000        0000000      000000000      0000000        0000000      000000000      0000000  |

| К」       |                                                                                                                             |

| H<br>_ G |                                                                                                                             |

| F E<br>D |                                                                                                                             |

| С<br>В   |                                                                                                                             |

| Α        | 000000000000000000000000000000000000000                                                                                     |

|          | 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29                                                                                     |

|          | 2 4 6 8 10 12 14 16 18 20 22 24 26 28                                                                                       |

Figure 1-1. CTZ/ZTZ 737-Pin Ball Grid Array (BGA) Package (Bottom View)

www.ti.com

### 1.2 Description

The TMS320C6472 device is a Texas Instruments next-generation fixed-point digital signal processor (DSP) targeting high-performance computing applications, including high-end industrial, mission-critical, high-end image and video, communication, media gateways, and remote access servers. This device was designed with these applications in mind. A common key requirement of these applications is the availability of large on-chip memories to handle vast amounts of data during processing. With 768K-Byte of shared RAM and 608K-Byte local L2 RAM per C64x+ Megamodule, the TMS320C6472 device can eliminate the need for external memory, thereby reducing system power dissipation and system cost and optimizing board density.

The TMS320C6472 device has six optimized TMS320C64x+<sup>™</sup> megamodules, which combine high performance with the lowest power dissipation per port. The TMS320C6472 device includes three different speeds: 500 MHz, 625 MHz, and 700 MHz. The C64x+ megamodules are the highest-performance fixed-point DSP generation in the TMS320C6000<sup>™</sup> DSP platform. The C64x+ megamodule is based on the third-generation high-performance, advanced VelociTI<sup>™</sup> very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making devices like TMS320C6472 an excellent choice for applications including video and telecom infrastructure, imaging/medical, and wireless infrastructure (WI). The C64x+<sup>™</sup> devices are upward code-compatible from previous devices that are part of the C6000<sup>™</sup> DSP platform.

The C64x+ megamodule core employs eight functional units, two register files, and two data paths. Like the earlier C6000 devices, two of these eight functional units are multipliers or .M units. Each C64x+ megamodule core .M unit doubles the multiply throughput versus the C64x core by performing four 16-bit x 16-bit multiply-accumulates (MACs) every clock cycle. Thus, eight 16-bit x 16-bit MACs can be executed every cycle on the C64x+ core. At a 500-MHz clock rate, this means 4000 16-bit MMACs can occur every second. Moreover, each multiplier on the C64x+ megamodule core can compute one 32-bit x 32-bit MAC or four 8-bit x 8-bit MACs every clock cycle.

The C64x+ megamodule integrates a large amount of on-chip memory organized as a two-level memory system. The level-1 (L1) program and data memories on this C64x+ megamodule are 32KB each. This memory can be configured as mapped RAM, cache, or some combination of the two. When configured as cache, L1 program (L1P) is a direct mapped cache where as L1 data (L1D) is a two-way set associative cache. The level 2 (L2) memory is shared between program and data space and is 608K-Byte in size. L2 memory can also be configured as mapped RAM, cache, or some combination of the two. The C64x+ megamodule also has a 32-bit peripheral configuration (CFG) port, an internal DMA (IDMA) controller, a system component with reset/boot control, interrupt/exception control, a power-down control, and a free-running 32-bit timer for time stamp.

The peripheral set includes: three Telecom Serial Interface Port (TSIPs); an 16/8 bit Universal Test and Operations PHY Interface for Asynchronous Transfer Mode (ATM) Slave [UTOPIA Slave] port; two 10/100/1000 Ethernet media access controllers (EMACs), which provide an efficient interface between the C6472 DSP core processor and the network; a management data input/output (MDIO) module (shared by both EMACs) that continuously polls all 32 MDIO addresses in order to enumerate all PHY devices in the system; a Serial RapidIO<sup>®</sup> with two 1x lanes and support for packet forwarding; a 32-bit DDR2 SDRAM interface; 12 64-bit general-purpose timers; an inter-integrated circuit bus module (I2C); 16 general-purpose input/output ports (GPIO) with programmable interrupt/event generation modes; and a 16-bit multiplexed host-port interface (HPI16).

The C6472 device has a complete set of development tools which includes: a C compiler, an assembly optimizer to simplify programming and scheduling, and a Windows<sup>®</sup> debugger interface for visibility into source code execution.

TMS320C6472

SPRT490B-OCTOBER 2008-REVISED JUNE 2011

www.ti.com

**NSTRUMENTS**

Texas

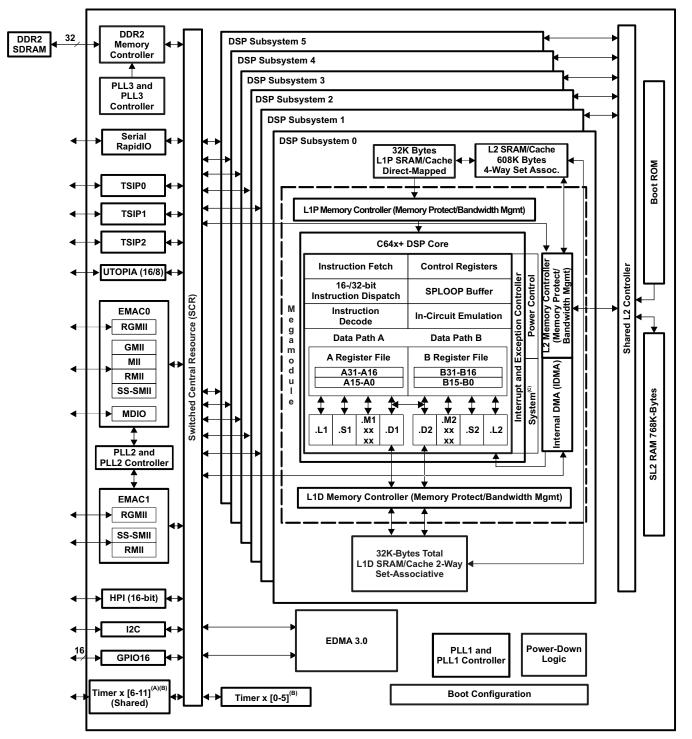

### 1.3 Functional Block Diagram

Figure 1-2 shows the functional block diagram of the C6472 device.

A. Timers 6-11 are shared.

B. Each of the Timer peripherals are configurable as either one 64-bit general-purpose timer *or* two 32-bit general-purpose timers *or* a watchdog timer.

C. System consists of Test, Emulation, Power Down, and Interrupt Controller.

#### Figure 1-2. C6472 Functional Block Diagram

4

**PRODUCT PREVIEW**

## 2 Device Operating Conditions

| Otherwise Noted)                                   |                                                              |                                      |

|----------------------------------------------------|--------------------------------------------------------------|--------------------------------------|

|                                                    | CV <sub>DD</sub>                                             | -0.5 V to 1.5 V                      |

|                                                    | CV <sub>DD2</sub>                                            | -0.5 V to 1.5 V                      |

|                                                    | DV <sub>DD33</sub>                                           | -0.5 V to 4.2 V                      |

|                                                    | DV <sub>DD18</sub> , AV <sub>DDA3</sub> , AV <sub>DDA4</sub> | -0.5 V to 2.5 V                      |

| Supply voltage range:                              | AV <sub>DDA1</sub> , AV <sub>DDA2</sub>                      | -0.5 V to 2.5 V                      |

|                                                    | DV <sub>DD15</sub>                                           | -0.5 V to 2.5 V                      |

|                                                    | DV <sub>DDR</sub>                                            | -0.5 V to 2.5 V                      |

|                                                    | CV <sub>DD1</sub>                                            | -0.5 V to 1.5 V                      |

|                                                    | AV <sub>DDA</sub> , DV <sub>DDD</sub> , AV <sub>DDT</sub>    | -0.5 V to 1.5 V                      |

|                                                    | 3.3-V pins                                                   | -0.5 V to DV <sub>DD33</sub> + 0.5 V |

|                                                    | RGMII pins                                                   | -0.3 V to DV <sub>DD15</sub> + 0.3 V |

| Input voltage (V <sub>I</sub> ) range:             | DDR2 memory controller pins                                  | -0.3 V to DV <sub>DD18</sub> + 0.3 V |

|                                                    | RIO pins                                                     | 0 V to 1.32 V                        |

|                                                    | 3.3-V pins                                                   | -0.5 V to DV <sub>DD33</sub> + 0.5 V |

|                                                    | RGMII pins                                                   | -0.3 V to DV <sub>DD15</sub> + 0.3 V |

| Output voltage (V <sub>O</sub> ) range:            | DDR2 memory controller pins                                  | -0.3 V to DV <sub>DD18</sub> + 0.3 V |

|                                                    | RIO pins                                                     | 0 V to 1.32 V                        |

|                                                    | Standard                                                     | 0°C to 85°C                          |

| Operating case temperature range, T <sub>C</sub> : | A version <sup>(4)</sup>                                     | -40°C to 100°C                       |

| Storage temperature range, T <sub>stg</sub>        |                                                              | -65°C to 150°C                       |

# 2.1 Absolute Maximum Ratings Over Operating Case Temperature Range (Unless Otherwise Noted)<sup>(1)(2)(3)</sup>

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to V<sub>SS</sub>.

(3) Overshoot and undershoot transients due to impedance mismatch on 3.3-V pins can be up to 30% of the supply voltage for up to 30% of the signal period without significantly impacting reliability. For RGMII and DDR2 pins, limit overshoot/undershoot to 20% of supply voltage for up to 20% of the duty cycle. These period limits assume continuous operation.

(4) Extended temperature (A version) range is available only on 500-MHz and 625-MHz devices.

# TMS320C6472

**PRODUCT PREVIEW**

SPRT490B-OCTOBER 2008-REVISED JUNE 2011

| Submit Documentation Feedback        |

|--------------------------------------|

| Product Folder Link(s) : TMS320C6472 |

| 2.2 | Recommended Operati | ing Conditions <sup>(1)</sup> |

|-----|---------------------|-------------------------------|

|-----|---------------------|-------------------------------|

|                                                     | PARAMETER                        |                                                                | MIN                          | NOM     | MAX                          | UNIT |

|-----------------------------------------------------|----------------------------------|----------------------------------------------------------------|------------------------------|---------|------------------------------|------|

|                                                     |                                  | 500 MHz                                                        | 0.95                         | 1.0     | 1.05                         |      |

| CV <sub>DD</sub>                                    | Supply voltage, Core             | 625 MHz                                                        | 1.05                         | 1.1     | 1.16                         | V    |

|                                                     |                                  | 700 MHz                                                        | 1.14                         | 1.2     | 1.26                         |      |

|                                                     |                                  | 500 MHz                                                        | 0.95                         | 1.0     | 1.05                         |      |

| CV <sub>DD2</sub>                                   | Supply voltage, SRIO Core        | 625 MHz                                                        | 1.05                         | 1.1     | 1.16                         | V    |

|                                                     |                                  | 700 MHz                                                        | 1.14                         | 1.2     | 1.26                         | -    |

| CV <sub>DD1</sub>                                   | Supply volttage, 1.2-V DDR       | Core                                                           | 1.14                         | 1.2     | 1.26                         | V    |

| DV <sub>DD33</sub>                                  | Supply voltage, 3.3-V I/O        |                                                                | 3.135                        | 3.3     | 3.465                        | V    |

| DV <sub>DD18</sub>                                  | Supply voltage, 1.8-V I/O (DI    | DR)                                                            | 1.71                         | 1.8     | 1.89                         | V    |

| DV <sub>DD15</sub>                                  | Supply voltage, 1.8-V/1.5-V I    |                                                                | 1.4                          |         | 1.9                          | V    |

| V <sub>REFHSTL</sub><br>(0.5 * DV <sub>DD15</sub> ) | Reference voltage, RGMII I/0     |                                                                | 0.7                          |         | 0.95                         | V    |

| V <sub>REFSSTL</sub><br>(0.5 * DV <sub>DD18</sub> ) | Reference voltage, DDR2 I/C      | )                                                              | 0.855                        | 0.9     | 0.945                        | V    |

| AV <sub>DDA1</sub>                                  | Analog supply voltage, PLL1      | (System PLL)                                                   | 1.71                         | 1.8     | 1.89                         | V    |

| AV <sub>DDA2</sub>                                  | Analog supply voltage, PLL2      | (EMAC PLL)                                                     | 1.71                         | 1.8     | 1.89                         | V    |

| AV <sub>DDA3</sub>                                  | Analog supply voltage, PLL3      | (DDR PLL)                                                      | 1.71                         | 1.8     | 1.89                         | V    |

| AV <sub>DDA4</sub>                                  | Analog supply voltage, DDR       |                                                                | 1.71                         | 1.8     | 1.89                         | V    |

| DV <sub>DDD</sub>                                   | SRIO Digital supply voltage      |                                                                | 1.14                         | 1.2     | 1.26                         | V    |

| AV <sub>DDA</sub>                                   | SRIO Analog supply voltage       |                                                                | 1.14                         | 1.2     | 1.26                         | V    |

| AV <sub>DDT</sub>                                   | SRIO Termination voltage         |                                                                | 1.14                         | 1.2     | 1.26                         | V    |

| DV <sub>DDR</sub>                                   | SRIO Regulator supply voltage    | ge                                                             | 1.35                         | 1.5/1.8 | 1.98                         | V    |

|                                                     |                                  | 3.3-V pins (except<br>I2C pins)                                | 2.0                          |         | DV <sub>DD33</sub> + 0.5     |      |

| N/                                                  |                                  | I2C pins                                                       | 0.7 * DV <sub>DD33</sub>     |         | DV <sub>DD33</sub> + 0.5     |      |

| V <sub>IH</sub>                                     | High-level input voltage         | RGMII pins                                                     | V <sub>REFHSTL</sub> + 0.10  |         | DV <sub>DD15</sub> + 0.3     | V    |

|                                                     |                                  | DDR2 memory controller pins                                    | V <sub>REFSSTL</sub> + 0.125 |         | DV <sub>DD18</sub> + 0.3     |      |

|                                                     |                                  | 3.3-V pins (except<br>I2C pins)                                | -0.5                         |         | 0.8                          |      |

| M                                                   | Low lovel input veltage          | I2C pins                                                       | -0.5                         |         | 0.3 * DV <sub>DD33</sub>     | v    |

| V <sub>IL</sub>                                     | Low-level input voltage          | RGMII pins                                                     | -0.3                         |         | V <sub>REFHSTL</sub> - 0.1   | v    |

|                                                     |                                  | DDR2 memory<br>controller pins                                 | -0.3                         |         | V <sub>REFSSTL</sub> - 0.125 |      |

|                                                     |                                  | $CV_{DD} = CV_{DD2} =$<br>1.0 V, CPU<br>frequency =<br>500 MHz |                              | 2.38    |                              |      |

| P <sub>CDD</sub>                                    | Core supply power <sup>(2)</sup> | $CV_{DD} = CV_{DD2} =$<br>1.1 V, CPU<br>frequency =<br>625 MHz |                              | 3.76    |                              | W    |

|                                                     |                                  | $CV_{DD} = CV_{DD2} =$<br>1.2 V, CPU<br>frequency =<br>700 MHz |                              | 5.42    |                              |      |

Operating conditions are at 500 MHz, 625 MHz, or 700 MHz. Assumes the following conditions: CPU utilization 30% DSP/60% control; DDR2 at 30% utilization (266 MHz), 35% writes, 32 bits, 15% bit switching; TSIP0, TSIP1, and TSIP2 at 20% utilization, 15% switching; UTOPIA 50 MHz, 16-bit at 50% utilization, 15% switching EMAC0, 1000 Mbps, RGMII, 50% utilization, 50% switching; EMAC1 disabled; SRIO both lanes disabled; all timers active; HPI disabled; I2C enabled at 10% utilization; room temperature (25°C). The actual power consumption is application-dependent. For more details on core and I/O activity, see the TMS320C6472/TMS320TCI6486 Power Consumption Summary (literature number SPRAAS4).

(1)

Texas NSTRUMENTS

www.ti.com

TMS320C6472

SPRT490B-OCTOBER 2008-REVISED JUNE 2011

# Recommended Operating Conditions<sup>(1)</sup> (continued)

|                  | PARAMETER                                       |                                                                                                                                                    | MIN                                   | NOM  | MAX | UNIT |  |

|------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|-----|------|--|

| P <sub>DDD</sub> |                                                 |                                                                                                                                                    | 3.3-V Supply<br>(DV <sub>DD33</sub> ) |      | 0.2 |      |  |

|                  | I/O supply power <sup>(2)</sup>                 | 1.8-V Supplies,<br>including PLLs<br>(DV <sub>DD18</sub> , AV <sub>DDA1</sub> ,<br>AV <sub>DDA2</sub> , AV <sub>DDA3</sub> ,<br>AV <sub>DDA4</sub> |                                       | 0.26 |     | W    |  |

|                  | (DV <sub>DE</sub><br>1.2-V<br>(CV <sub>DE</sub> | 1.5-V Supplies<br>(DV <sub>DD15</sub> , DV <sub>DDR</sub> )                                                                                        |                                       | 0.05 |     |      |  |

|                  |                                                 | 1.2-V Supplies<br>(CV <sub>DD1</sub> , AV <sub>DDA</sub> ,<br>DV <sub>DDD</sub> , AV <sub>DDT</sub> )                                              |                                       | 0.28 |     |      |  |

# TMS320C6472

SPRT490B-OCTOBER 2008-REVISED JUNE 2011

#### www.ti.com

NSTRUMENTS

Texas

### 2.3 Electrical Characteristics Over Recommended Ranges of Supply Voltage and Operating Case Temperature (Unless Otherwise Noted)

|                 | PARAMETEI                 | R                                                                                                                                       | TEST<br>CONDITIONS <sup>(1)</sup>                                                                 | MIN                      | ТҮР  | МАХ   | UNIT |

|-----------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------|------|-------|------|

|                 |                           | 3.3 V pins (except I2C pins)                                                                                                            | DV <sub>DD33</sub> = MIN,<br>I <sub>OH</sub> = MAX                                                | 0.8 * DV <sub>DD33</sub> |      |       | V    |

| V <sub>OH</sub> | High-level ouput voltage  | I2C pins                                                                                                                                | DV <sub>DD33</sub> = MIN,<br>I <sub>OH</sub> = MAX                                                | 0.8 * DV <sub>DD33</sub> |      |       | V    |

| 011             |                           | RGMII pins                                                                                                                              |                                                                                                   | DV <sub>DD15</sub> - 0.4 |      |       | V    |

|                 |                           | DDR2 memory<br>controller pins                                                                                                          |                                                                                                   | DV <sub>DD18</sub> - 0.4 |      |       | V    |

|                 |                           | 3.3-V pins (except I2C pins)                                                                                                            | DV <sub>DD33</sub> = MIN,<br>I <sub>OL</sub> = MAX                                                |                          |      | 0.4   | V    |

| V <sub>OL</sub> | Low-level ouput voltage   | I2C pins                                                                                                                                | Pulled up to 3.3 V,<br>3 mA sink current                                                          |                          |      | 0.4   | V    |

| 0L              |                           | RGMII pins                                                                                                                              |                                                                                                   |                          |      | 0.4   | V    |

|                 |                           | DDR2 memory controller pins                                                                                                             |                                                                                                   |                          |      | 0.4   | V    |

| ų               |                           |                                                                                                                                         | $V_{I} = V_{SS}$ to<br>$DV_{DD33}$ , pins<br>without internal<br>pull-up or<br>pull-down resistor | -1                       |      | 1     | uA   |

|                 |                           | 3.3-V pins (except I2C pins)                                                                                                            | $V_{I} = V_{SS}$ to<br>DV <sub>DD33</sub> , pins with<br>internal pull-up<br>resistor             | 50                       | 100  | 400   | uA   |

|                 | Input current (DC)        |                                                                                                                                         | $V_{I} = V_{SS}$ to<br>DV <sub>DD33</sub> , pins with<br>internal pull-down<br>resistor           | -400                     | -100 | -50   | uA   |

|                 |                           | I2C pins                                                                                                                                | $0.1 * DV_{DD33} \le V_{I} \le 0.9 * DV_{DD33}$                                                   | -10                      |      | 10    | uA   |

|                 |                           | RGMII pins                                                                                                                              |                                                                                                   | -1                       |      | 1     | uA   |

|                 |                           | DDR2 memory controller pins                                                                                                             |                                                                                                   | -1                       |      | 1     | uA   |

| I <sub>OH</sub> |                           | E Class Buffers -<br>EMU[18:0] and all<br>3.3-V Ethernet, except<br>MCRS0_RMCRSDV0,<br>MCOL0, GMDIO, and<br>GMDCLK                      |                                                                                                   |                          |      | -7    | mA   |

|                 |                           | D Class Buffers -<br>GPIO[15:0], TDO,<br>HOUT, and<br>SYSCLKOUT                                                                         |                                                                                                   |                          |      | -3    | mA   |

|                 | High-level output current | C Class Buffers - HPI,<br>TSIP, UTOPIA,<br>BOOTACTIVE,<br>WDOUT,<br>RESETSTAT, TIMO2,<br>MCRS0_RMCRSDV0,<br>MCOL0, GMDIO, and<br>GMDCLK |                                                                                                   |                          |      | -3    | mA   |

|                 |                           | RGMII pins                                                                                                                              |                                                                                                   |                          |      | -8    | mA   |

|                 |                           | DDR pins                                                                                                                                |                                                                                                   |                          |      | -13.4 | mA   |

(1) For test conditions shown as MIN, MAX, or NOM, use the appropriate value specified in the recommended operating conditions table.

8

Copyright © 2008–2011, Texas Instruments Incorporated

# Electrical Characteristics Over Recommended Ranges of Supply Voltage and Operating Case Temperature (Unless Otherwise Noted) *(continued)*

|                                         | PARAMETER                |                                                                                                                                         | TEST<br>CONDITIONS <sup>(1)</sup> | ΜΙΝ Τ΄ | YP MAX | UNIT |

|-----------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------|--------|------|

|                                         | Low-level output current | E Class Buffers -<br>EMU[18:0] and all<br>3.3-V Ethernet, except<br>MCRS0_RMCRSDV0,<br>MCOL0, GMDIO, and<br>GMDCLK                      |                                   |        | 7      | mA   |

| I <sub>OL</sub>                         |                          | D Class Buffers -<br>GPIO[15:0], TDO,<br>HOUT, and<br>SYSCLKOUT                                                                         |                                   |        | 3      | mA   |

|                                         |                          | C Class Buffers - HPI,<br>TSIP, UTOPIA,<br>BOOTACTIVE,<br>WDOUT,<br>RESETSTAT, TIMO2,<br>MCRS0_RMCRSDV0,<br>MCOL0, GMDIO, and<br>GMDCLK |                                   |        | 3      | mA   |

|                                         |                          | RGMII pins                                                                                                                              |                                   |        | 8      | mA   |

|                                         |                          | DDR pins                                                                                                                                |                                   |        | 13.4   | mA   |

|                                         |                          | 3.3-V pins                                                                                                                              |                                   | -10    | 20     | uA   |

| I <sub>OZ</sub>                         | Off-state output current | RGMII pins                                                                                                                              |                                   | -10    | 10     | uA   |

|                                         |                          | DDR pins                                                                                                                                |                                   | -10    | 10     | uA   |

| -                                       |                          | commercial<br>temperature                                                                                                               | 0                                 | 85     | °C     |      |

| T <sub>C</sub> Operating case temperatu |                          | extended<br>temperature <sup>(2)</sup>                                                                                                  |                                   | -40    | 100    | C    |

(2) Extended temperature (A) range is available only on 500-MHz and 625-MHz devices.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                     |                                   |

|-----------------------------|------------------------|----------------------------------|-----------------------------------|

| Audio                       | www.ti.com/audio       | Communications and Telecom       | www.ti.com/communications         |

| Amplifiers                  | amplifier.ti.com       | Computers and Peripherals        | www.ti.com/computers              |

| Data Converters             | dataconverter.ti.com   | Consumer Electronics             | www.ti.com/consumer-apps          |

| DLP® Products               | www.dlp.com            | Energy and Lighting              | www.ti.com/energy                 |

| DSP                         | dsp.ti.com             | Industrial                       | www.ti.com/industrial             |

| Clocks and Timers           | www.ti.com/clocks      | Medical                          | www.ti.com/medical                |

| Interface                   | interface.ti.com       | Security                         | www.ti.com/security               |

| Logic                       | logic.ti.com           | Space, Avionics and Defense      | www.ti.com/space-avionics-defense |

| Power Mgmt                  | power.ti.com           | Transportation and<br>Automotive | www.ti.com/automotive             |

| Microcontrollers            | microcontroller.ti.com | Video and Imaging                | www.ti.com/video                  |

| RFID                        | www.ti-rfid.com        | Wireless                         | www.ti.com/wireless-apps          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        |                                  |                                   |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated