# Design Guide: TIDEP-01030 mmWave Diagnostic and Monitoring for High-End Corner Radar Reference Design

Features

efficient

Applications

quick time-to-market

Ultra short range radar

Medium and short range radar

Long range radar

٠

Demonstrates the usage of inbuilt Diagnostic and

Monitor features of mmWave Radar Sensors to

improve system performance and robustness

Use of safety resources to build ASIL-B SIL2

applications to make system implementation

mmWave sensors across different devices and

Based on proven EVM hardware designs enabling

# Description

This reference design features the built-in autonomous monitoring functionality in the mmWave Radar sensors that enhances design efficiency by minimizing the processing load on the host. This reference design uses Safety Diagnostic Library (SDL) to perform a diagnostic test at programmable digital cores, peripherals, and memories. The design also configures and enables radio frequency (RF) and Analog Monitor features of different hardware components. By assisting in the implement of ASIL-B SIL2 compliant products with the various safety resources, this reference design accelerates overall development time and time to market.

#### Resources

| TIDEP-01030        | Design Folder  |

|--------------------|----------------|

| AWR2944            | Product Folder |

| AWR2944EVM         | Tool Folder    |

| mmWave MCUPLUS SDK | Tool Folder    |

Ask our TI E2E<sup>™</sup> support experts

# **1** System Description

The TIDEP-01030 provides a reference for creating a diagnostic and monitoring application using TI's AWR2944 based on 77GHz mmWave radio-frequency complementary metal-oxide semiconductor (RF-CMOS) technology. mmWave sensing technology detects vehicles, such as cars, motorcycles, and bicycles, at extended ranges regardless of environmental conditions, such as rain, fog, or dust. TI's mmWave sensing devices integrate a 76–81GHz mmWave radar front end with Arm<sup>®</sup> microcontroller (MCU) and TI DSP cores for single-chip systems.

TI mmWave system on chip (SOC) has built-in circuits for diagnostic and monitoring which enables the detection of both the systematic and random faults. These safety mechanisms significantly reduce system complexity and cost in safety-critical applications. It is important to test these diagnostic mechanisms using SafeTI diagnostic Library (SDL).

TI's radar mmWave integrated chips (ICs) include hardware and firmware elements to enable monitoring of the mmWave analog and digital subsystems. These built-in features of RadarSS are exposed to the application through firmware APIs.

This reference design demonstrates the use of inbuilt diagnostic and monitoring functionality of mmWave Radar Sensor. The design provides a list of required hardware, schematics, and reference software to quickly begin ASIL-B SIL2 compliance product development. This reference design describes the example use case as well as the design principle, implementation details, and engineering tradeoffs made in the development of this application. High-level instructions for replicating the design are provided. A few of the key diagnostic features of the device are listed below:

- Self-test controller (STC)

- Programmable built-in self-test (PBIST)

- Error Correction Code (ECC)

- Bus Safety

2

PARITY on miscellaneous memories or peripherals

The details are covered in the Safety Manual.

Note

For the remainder of this document *mmWave Sensor* implies AWR2944 and *EVM* implies AWR2944EVM, unless otherwise mentioned.

# 2 System Overview

TI's radar mmWave integrated chips (ICs) include hardware and firmware elements to enable monitoring of the mmWave, analog and digital sections. Most of the digital elements of the device have built-in diagnostic capability.

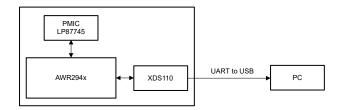

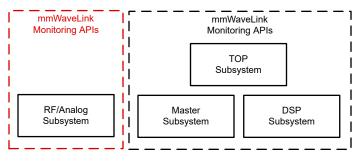

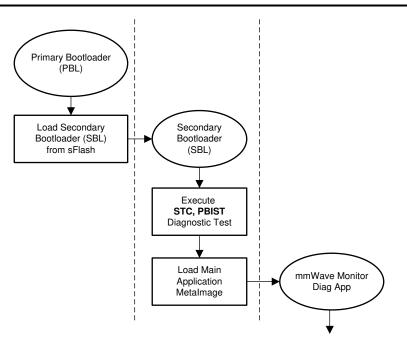

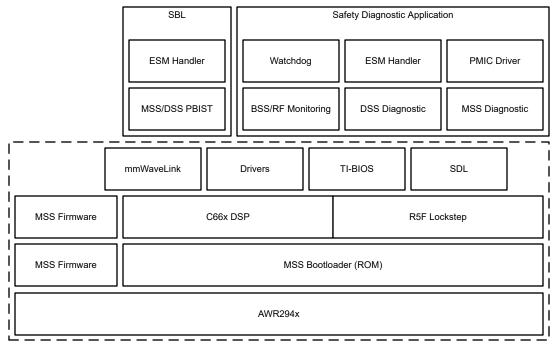

Figure 2-1. mmWave Sensor Monitor and Diagnostic

The analog subsystem contains the Analog and RF functionality of the device. The AWR294x has three or four transmitters and four receiver chains along with the clock oscillator and frequency modulated continuous wave (FMCW) signal generation circuitry (Cleanup APLL, Synthesizer, frequency multipliers, and so forth). The *Radar Subsystem* is responsible for initializing and calibrating the Analog and RF modules. The subsystem periodically monitors the Analog and RF functionality to make sure all the Analog and RF modules work in the defined

limits. This functionality can be configured through mmWavelink Monitoring APIs by MSS or DSS application with various mode and reporting options.

TOP, Master, and DSP subsystems contain various memory and digital components which have safety diagnostic features. These features can be configured and verified using the Safety Diagnostic Library to manage both systematic and random faults of the device.

# 2.1 Block Diagram

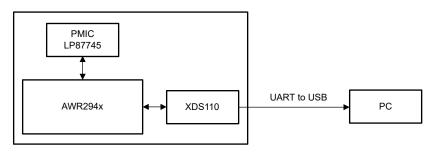

Figure 2-2. TIDEP-01030 Block Diagram

# 2.2 Design Considerations

This reference design shows the use of the Diagnostic and Monitoring feature. Diagnostic tests are implemented through the SDL whereas Monitoring features are enabled on RadarSS through the mmWaveLink library. Some sets of the Diagnostic tests are destructive which can cause a soft or warm reset, so within this reference design those tests are part of the Secondary Bootloader (SBL). This way main application flow does not get hampered due to the execution of these destructive Diagnostic tests. Apart from these DIAG tests, remaining DIAG are executed on MSS as well DSS core during the application initialization. See Section 2.4.2 for further implementation details.

# 2.3 Highlighted Products

#### 2.3.1 LP87745

The LP87745-Q1 helps meet the power management requirements of the latest platforms, particularly in automotive radar and camera and industrial radar applications. The device contains three step-down DC/DC converters, and a 5V boost converter switch and bypass switch. To support safety critical applications, the device integrates two voltage monitoring inputs for external power supplies, and a window watchdog.

#### 2.3.1.1 LP87745 Features

- AEC-Q100 qualified with the following results:

- Device temperature grade 1: -40°C to +125°C ambient operating temperature

- Functional safety-compliant device

- Developed for functional safety applications

- Documentation available to aid ISO 26262 functional safety system design up to ASIL-C and SIL-2

- Input supply overvoltage and undervoltage monitoring

- Regulator output overvoltage and undervoltage monitoring

- Overvoltage and undervoltage monitoring for one external rail

- Q and A watchdog

- Level or PWM error signal monitor (ESM)

- BIST and CRC

- Input voltage: 3.3V nominal (3V to 4V range)

- Three low-noise step-down DC/DC converters:

- Output voltage: 0.9V to 1.9V, 0.8V (BUCK3), 0.82V (BUCK3)

- Maximum output current: 3A, 3A, 3A

- Switching frequency: 4.4MHz, 8.8MHz, and 17.6MHz

- 5V boost converter

- Maximum output current: 350mA

- 150mA LDO

- Output voltage 1.8V or 3.3V

- Output short-circuit and overload protection

- Input overvoltage protection (OVP) and undervoltage lockout (UVLO)

- Overtemperature warning and protection

- Serial peripheral interface (SPI)

### 2.3.1.2 Safety Features

The LP8774x-Q1 device is an ISO26262 functional safety-compliant power management IC (PMIC) to aid safety system designs up to ASIL-C, SIL-2 with the following key functional safety features. See the *LP87745-Q1 Three Buck Converters and 5-V Boost for AWR and IWR Radar Sensors* data sheet specification and the LP87745-Q1 Functional Safety Manual SFFS159 for more details about the safety mechanisms and how to integrate this device in a functional safety system.

#### Monitoring of VCCA Input, Regulator Outputs, and VMON Inputs

The LP8774x-Q1 device monitors the undervoltage (UV) and overvoltage (OV) conditions of the output voltage of the bucks, the boost, VIO\_LDO, VMON1 (general purpose voltage monitor) input and the VCCA input through independent voltage monitors. In addition, regulator outputs are monitored by short-circuit and current limit comparators. Regulator monitors are enabled when the corresponding regulator is enabled and OV, UV self-test is completed.

#### • Finite state machine (FSM) and Safing outputs: NRSTOUT, nINT, CAN\_DIS

The LP8774x-Q1 device integrates a finite state machine (FSM) engine which manages the state of the device during operating state transitions. The device supports NVM configurable power-up, power-down sequences and error handing. In the case of severe errors, the main processor reset signal (NRSTOUT) is pulled low and all the supply rails are turned off to keep the system in safe state. If moderate error events occur, depending on the NVM configuration, PMIC can notify the processor of these events through the interrupt signal (nINT) and through software interrupts and can disable Controller Area Network (CAN) communication with nINT or CAN\_DIS signal.

#### Q&A watchdog

The watchdog monitors the correct operation of the MCU. The Question Answer (Q&A) mode watchdog in LP8774x-Q1 requires specific messages from the MCU in specific time intervals to detect correct operation of the MCU. During operation, the device provides a question for the MCU through the SPI. The MCU performs a fixed series of arithmetic operations on this question to calculate the required 32-bit answer. This answer is split into four answer bytes: Answer-3, Answer-2, Answer-1, and Answer-0 and the MCU must send these answers in a correct sequence and timing through the SPI. If the MCU answer or the answer sequence is not correct, the device detects the error and the response to the error depends on the NVM, OTP configuration and in if there are persistent errors, PMIC error counter overflows and all the supply rails are shut down to keep the system in safe state.

#### • Error signal monitor (ESM)

The LP8774x-Q1 device has an Error Signal Monitor (ESMs) to monitor the MCU error output signal at the nERR input pin. By default, ESM is disabled at start-up of the LP8774x-Q1 device. To start ESM, the MCU sets the start bit.

ESM\_MCU\_START initiates through software after the system is powered up and the LP8774x-Q1 configuration is completed by MCU. The device supports either Level mode or PWM mode. If the device detects the ESM error and the response to the error depends on the NVM, OTP configuration and in the case of persistent errors, the PMIC error counter overflows and all the supply rails are shut down to keep the system in safe state.

#### ABIST, LBIST and CRC

4

The device has analog build in self-test (ABIST) which checks the health of voltage monitors and TSD compactors and logic built-in self-test (LBIST) which checks the digital features during the device start-up and notification is sent to the processor. Device trim registers, configuration registers and SPI communication are protected with CRC to detect the bit errors.

#### 2.3.2 AWR294x mmWave Sensor

The mmWave sensor is an integrated single-chip, frequency-modulated continuous wave (FMCW) sensor capable of operation in the 76–81GHz frequency band. The device is built with TI's low-power, 45nm RFCMOS processor and enables unprecedented levels of analog and digital integration in an extremely small form factor. The device has four receivers and three, four transmitters with a closed-loop phase-locked loop (PLL) for precise and linear chirp synthesis.

The sensor includes a built-in radio processor (BIST) for RF calibration and safety monitoring. Based on real baseband architecture, the sensor device supports an IF bandwidth of 15MHz with reconfigurable output sampling rates. The presence of Arm<sup>®</sup> Cortex<sup>®</sup> R5F and Texas Instruments C66xx Digital Signal Processor (DSP) (fixed and floating point) along with 4MB of on-chip RAM enables high-level algorithm development. This device is ASIL-B certified and an excellent choice for low power, self-monitored, and ultra-accurate radar systems in the automotive space.

# 2.4 System Design

#### 2.4.1 Hardware Block Diagram

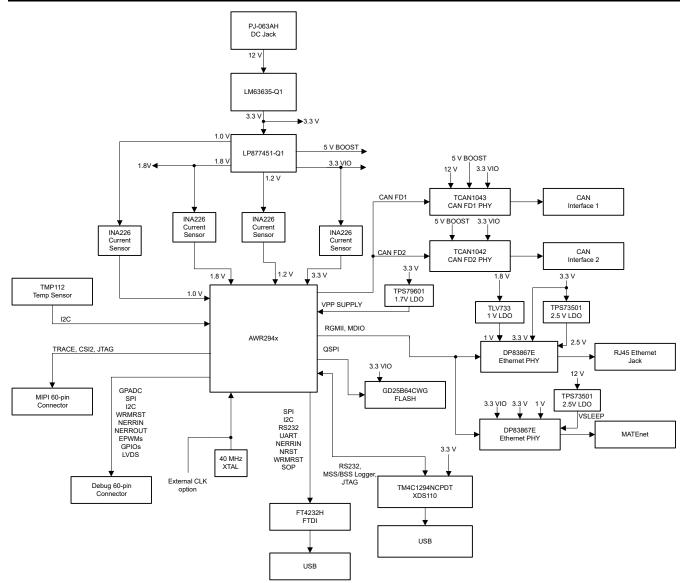

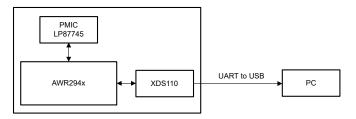

The TIDEP-01030 is implemented using the AWR2944BOOST EVM. The EVM needs to be connected to a host PC through universal asynchronous receiver-transmitter (UART) for Meta Image load and log collection.

The AWR2944EVM includes the following features:

- 1. AWR2944 Radar Device on AWR2944EVM

- 2. Power management circuit to provide all the required supply rails from a single 5V input

- 3. Four onboard TX antennas and four RX antennas

- 4. Onboard XDS110 that provides a JTAG interface, UART for sending Diagnostic test and Monitor report from mmWave device

#### Figure 2-3. Block Diagram AWR2944EVM

For more details on the hardware, see the following:

#### • AWR2944 Evaluation Module (AWR2944EVM)

#### 2.4.2 Software Components

6

This application showcases the Diagnostic and Monitoring feature of the mmWave sensor. The application uses the SafeTI<sup>™</sup> Diagnostic Library (SDL) for diagnostic test implementation and mmWaveLink to configure monitoring on RF front end.

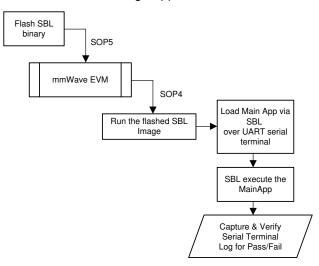

In this reference design application, a few diagnostic tests are done in secondary bootloader (SBL) at the MSS core. At the end of these tests, SBL loads the main application to the MSS and DSS RAM location reading Meta Image from supervisory flash (sFlash).

Figure 2-4. Application Control Flow Diagram

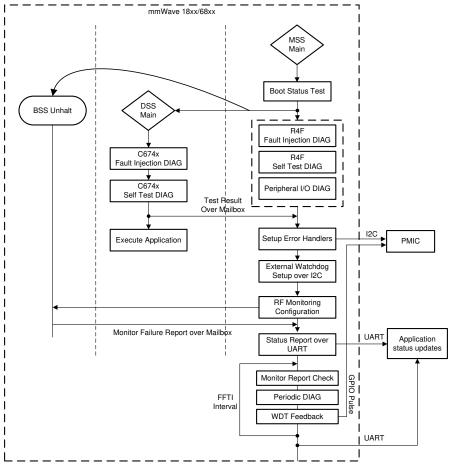

Figure 2-5 shows the high-level flow diagram of the main application which contains the MSS and DSS images. Diagnostic and Monitor test status from the sensor are sent over UART to PC.

Figure 2-5. DIAG and Monitor App Flow Diagram

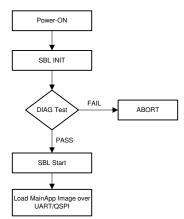

# 2.4.2.1 Secondary Bootloader (SBL)

The secondary bootloader is primarily responsible for updating the application meta image in the sFlash by receiving the image over a serial interface. The SBL then loads and runs the updated application meta image.

The ROM (primary) bootloader always loads the SBL. Applications can choose to either update or load and run the application meta image.

For safety applications, the SBL can be used to perform some of destructive tests like PBIST and STC that need to be run during boot time. These DIAG can cause core reset during the execution which is the main reason to move these tests to SBL. These tests are validated before loading the main application. In the case of a failure, the SBL aborts and exits.

Figure 2-6. SBL Flow Diagram

#### 2.4.2.2 mmWaveLink APIs

mmWaveLink library provides miscellaneous APIs to communicate with RadarSS over the mailbox interface. In this application, monitoring features are configured by MSS/DSS application through mmWaveLink APIs. Later applications receive monitoring reports through mmWaveLink callback in the form of an asynchronous event from RadarSS.

#### 2.4.2.3 mmWave Safety Diagnostic Library (SDL)

The mmWave SafeTI Diagnostic Library (SDL) is a collection of functions for access to safety functions and response handlers for various safety mechanisms for TI mmWave sensors. These functions assist in the development of software applications involving functional safety.

The SDL provides a collection of diagnostic APIs and low-level driver functions to access the diagnostic features. These safety mechanisms are defined in the *mmWave Device Safety Manual*.

Diagnostics Library (DIAG) is the Software diagnostics library that provides APIs to access Safety functions and inject or detect faults.

|        | Customer Code                              | Legend:       |

|--------|--------------------------------------------|---------------|

| OSAL 4 | Diagnostic Library<br>CSL Functional Layer | Customer Code |

|        | SCL Register Layer                         |               |

|        | HW VIM ESM RCM                             | SPI           |

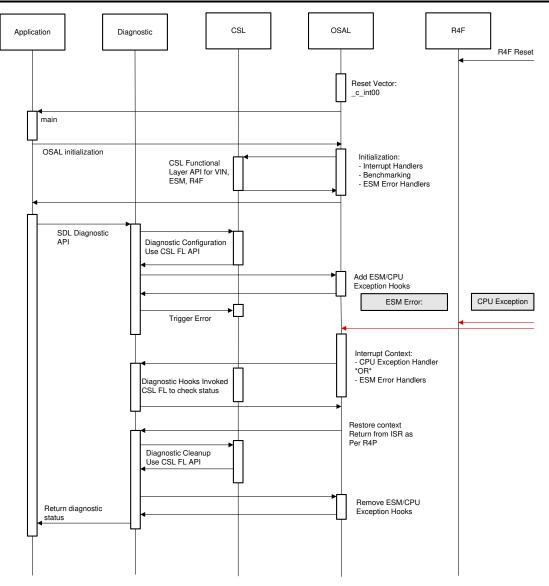

Figure 2-7. SDL Layer Architecture

In Figure 2-7, the red blocks are Functional safety quality, all relevant documents and reports are provided in SDL package.

The Diagnostic Library provides the implementation of the diagnostics specified in the mmWave Device Safety Manual.

Diagnostic test categories (based on time duration):

- Single-shot diagnostics

- Periodic diagnostics

- Fault insertion diagnostics: ECC, Parity, MPU diagnostics.

- Self test diagnostics: LBIST, PBIST, DCC, CCM diagnostics.

- · Peripheral IO diagnostics: peripheral loopback, Nerror In or Out diagnostics

- · Readback of static configuration registers: diagnostics to periodically check static configuration registers

#### **Typical DIAG Test Flow**

- Operating System Adaptation Layer (OSAL) defines the ability to add and delete hooks. Hooks can be added to ESM error and CPU exceptions

- · HW Configuration HW IP registers which need to be configured to execute the diagnostic

- CPU Exception, ESM Error Diagnostic generate ESM error, CPU exceptions

- All diagnostic handlers are internal to the diagnostic layer

#### 2.4.2.4 mmWave SDK Software Block Diagram

The mmWave software development kit (SDK) enables the development of mmWave sensor applications using the mmWave EVM. The SDK provides foundational components that help designers focus on the applications. In addition, the SDK provides several demonstration applications, which serve as a guide for integrating the SDK into end-user mmWave applications. This reference design is developed on the SDK framework and uses the SDL library.

Figure 2-9. SBL and App Block Diagram

# 3 Hardware, Software, Testing Requirements, and Test Results

#### 3.1 Hardware Requirements

Texas Instruments' AWR2944EVM is an easy-to-use evaluation board for the AWR2944 mmWave sensing device.

This reference design requires AWR2944EVM to execute the reference application. However, customers can run this on the board as well.

# 3.2 Test Setup

The test setup contains AWR2944EVM that is connected with the PC over a USB cable.

Figure 3-1. Test Setup

Figure 3-2 is the typical test flow for a reference design application.

Figure 3-2. Typical Test Flow

#### 3.3 Test Results

AWR2944EVM is connected with the PC over a USB cable. The SBL image is flashed first then the main application. Refer to the Getting started document in the software package for the exact steps to execute this application.

Figure 3-3, Figure 3-4, and Figure 3-5 show the test results of a Diagnostic test result performed by SBL as well as the Main application.

| **                                                                         | COM88 - Tera Term VT                                           |

|----------------------------------------------------------------------------|----------------------------------------------------------------|

| DSS Safety Mechanims Logs                                                  | File Edit Setup Control Window Help                            |

| HWA Parity Test Application                                                | All tests have passed for ECC Bus Safety Applaiction.          |

| HWA TEST START : starting                                                  | MCRC Test Application                                          |

| All test passed for HWA Parity Application                                 | MCRC AUTO CPU mode on Channel 1: Transfer Test Started         |

| ECC Test Application for HWA Memory                                        | Calculating Reference MCRC signature Value.                    |

| ECC UC-1 and UC-2 Test                                                     | MCRC signature value : 0x1c133adab4dd50fU                      |

| UC-1: Injected 1-bit error and got ESM Interrupt                           | MCRC Full Mode Computation Time: 5293us                        |

| UC-2: Injected 2-bit error and got ESM Interrupt                           | Sector signature matches - Passed                              |

| All Use_Cases have passed for ECC Test Application for HWA Memory.         | Calculated MCRC signature value : 0x01c133adab4dd50fU          |

| ECC Test Application for L3 Memory                                         | EDMA Data transfer completed !!                                |

| ECC UC-1 and UC-2 Test                                                     | MCRC Auto Mode Computation Time: 17us                          |

| UC-1: Injected 1-bit error and got ESM Interrupt                           | MCRC AUTO CPU mode on Channel 2: Transfer Test Started         |

| UC-2: Injected 2-bit error and got ESM Interrupt                           | Using Pre-Defined Reference MCRC signature Value.              |

| All Use_Cases have passed for ECC Test Application for L3 Memory.          | Pre-defined MCRC signature value : 0x1c133adab4dd50fU          |

| ECC Test Appliaction for DSS Mailbox memory                                | Sector signature matches - Passed                              |

| ECC UC-1 and UC-2 Test                                                     | Calculated MCRC signature value : 0x01c133adab4dd50fU          |

| UC-1: Injected 1-bit error and got ESM Interrupt                           | EDMA Data transfer completed !!                                |

| UC-2: Injected 2-bit error and got ESM Interrupt                           | MCRC Auto Mode Computation Time: 15us                          |

| All Use_Cases have passed for ECC Test Appliaction for DSS Mailbox memory. | TPCC Parity Test Application for MSS Instance                  |

| DSS TPCC PARITY Example : Started                                          | MSS TPCC PARITY Example : Started                              |

| All tests have passed for TPCC Parity Test Application.                    | ESM_Test_init: Init MSS ESM complete                           |

| ***************************************                                    | MSS TPCCA Parity                                               |

| **                                                                         | Paran Register = 82000007                                      |

| MSS Safety Mechanims Logs                                                  | MSS TPCCA Parity : Completed                                   |

| TCM Parity Test Application Statrting                                      | ESM_Test_init: Init MSS ESM complete                           |

| TCM PARITY Test Applaiction : Started                                      | MSS TPCCB Parity                                               |

| ESM_Test_init: Init MSS ESM complete                                       | Paran Register = 82000007                                      |

| MSS TCM PARITY: ATCM0 Started                                              | MSS TPCCB Parity : Completed                                   |

| MSS ATCM0 Parity : Completed                                               | All tests have passed for TPCC Parity Test Application.        |

| ESM_Test_init: Init MSS ESM complete                                       | Debug: ADCBUF Instance 10292CE0 has been reopened successfully |

| MSS TCM PARITY: ATCM1 Started                                              | **************************************                         |

| MSS ATCM1 Parity : Completed                                               | Debug: Launching the mmwaveLink                                |

| ESM_Test_init: Init MSS ESM complete                                       | ***************************************                        |

| MSS TCM PARITY: BØTCMØ Started                                             | Debug: CRC Channel 1 has been opened successfully              |

| MSS BOTCMO Parity : Completed                                              | mmWave Link Initialization Pass                                |

| ESM_Test_init: Init MSS ESM complete                                       | Debug: BootupStatus = 0x3b3b7ffa                               |

| MSS TCM PARITY: BOTCM1 Started                                             | Debug: Finished get radarSS bootup status to BSS               |

| MSS BØTCM1 Parity : Completed                                              | Get radarSS bootup status Pass                                 |

| ESM_Test_init: Init MSS ESM complete                                       | Debug: Finished rlRfSetDeviceCfg                               |

| MSS TCM PARITY: BITCM0 Started                                             | Set Async event config status Pass                             |

|                                                                            | Debug: Set HSI clock successfully                              |

| Figure 3-3. Diagnostic Test Results 1                                      | Figure 2.4 Disgnastic Test Besults 2                           |

#### re 3-3. Diagnostic Test Results

Figure 3-4. Diagnostic Test Results 2

Debug: Finished information related to GPADC Internal Analog Signals monitoring configurations to BSS -nWave Link GPADC Internal Analog Signals Config Debug: Finished information related to APLL and Synthesizer's control voltage si gnals monitoring configurations to BSS Set nmWave Link MmwaveLink\_setRfPllContrlVoltMonConfig Config Debug: Finished information related to the DCC based clock frequency monitoring configurations to BSS Set nmWave Link Dual Clk Config Debug: Finished rlRfAnaMonConfig configurations to BSS Start Monitoring Pass Sensor Start Debug: Frames are already stopped [21] Sensor Stop Monitoring results Pass Debug: Monitoring R RL\_RF\_AE\_MON\_TEMPERATURE\_REPORT\_SB [0×13] RL\_RF\_AE\_MON\_RX\_GAIN\_PHASE\_REPORT [0×f] RL\_RF\_AE\_MON\_RX\_IF\_STAGE\_REPORT [0×5] RL\_RF\_AE\_MON\_TX0\_POWER\_REPORT [0x3] RL\_RF\_AE\_MON\_TX1\_POWER\_REPORT [0x3] RL\_RF\_AE\_MON\_TX2\_POWER\_REPORT [0x3] BL BE AF MON TX3 POVER REPORT (0x3) RL\_RF\_AE\_MON\_IX0\_BALLBREAK\_REPORT [0×1] RL\_RF\_AE\_MON\_TX1\_BALLBREAK\_REPORT [Ø×1] RL RF AF MON TX2 BALLBREAK REPORT (0x1) RL\_RF\_AE\_MON\_IX3\_BALLBREAK\_REPORT [Ø×1] RL\_RF\_AE\_MON\_Adv\_TX\_GAIN\_MISMATCH\_REPORT [0x3] RL\_RF\_AE\_MON\_SYNTHESIZER\_FREQ\_REPORT [Øx1] RL\_RF\_AE\_MON\_TXØ\_INT\_ANA\_SIG\_REPORT [Øx3] BL RE AE MON TX1 INT ANA SIG REPORT (0×3) RL\_RF\_AE\_MON\_TX2\_INT\_ANA\_SIG\_REPORT [0×3] RL\_RF\_AE\_MON\_TX2\_INT\_ANA\_SIG\_REPORT [0×3] RL\_RF\_AE\_MON\_RX\_INT\_ANALOG\_SIG\_REPORT [0×ff] RL\_RF\_AE\_MON\_PMCLKLO\_INT\_ANA\_SIG\_REPORT [0×3] RL\_RF\_AE\_MON\_GPADC\_INT\_ANA\_SIG\_REPORT [0×7] RL\_RF\_AE\_MON\_PLL\_CONTROL\_VOLT\_REPORT [0×37] RL\_RF\_AE\_MON\_DCC\_CLK\_FREQ\_REPORT [0x3f] All tests have completed!!

#### Figure 3-5. Diagnostic Test Results 3

# 4 Design and Documentation Support

#### 4.1 Design Files

#### 4.1.1 Schematics

To download the schematics, see the design files at TIDEP-01030.

#### 4.1.2 BOM

To download the bill of materials (BOM), see the design files at TIDEP-01030.

#### 4.2 Tools and Software

#### Tools

**Serial Terminal** This application takes input and streams the log over the UART COM port. The Serial Terminal tool is required to connect to the device over the COM port.

#### Software

Diagnostic and Monitoring Reference Application Application source code and binary files are available at TI-Rex Radar Toolbox. Refer to the Getting Started document available in the same package for SW installation and execution steps.

# 4.3 Documentation Support

- 1. Texas Instruments, Enabling Functional Safety in TI mmWave Devices Seminar Presentation

- 2. Texas Instruments, *LP87745-Q1 Three Buck Converters and 5-V Boost for AWR and IWR Radar Sensors Data Sheet*

- 3. Texas Instruments, AWR2943/44 Single-Chip 76- and 81-GHz FMCW Radar Sensor Data Sheet

#### 4.4 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 4.5 Trademarks

TI E2E<sup>™</sup> and SafeTI<sup>™</sup>, and are trademarks of Texas Instruments. Arm<sup>®</sup> and Cortex<sup>®</sup> are registered trademarks of Arm Limited. All trademarks are the property of their respective owners.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated